## 4 x 4 REGISTER FILE; 3-STATE

# FEATURES

- Simultaneous and independent read and write operations

- Expandable to almost any word size and bit length

- Output capability: bus driver ٠

- ICC category: MSI •

#### GENERAL DESCRIPTION

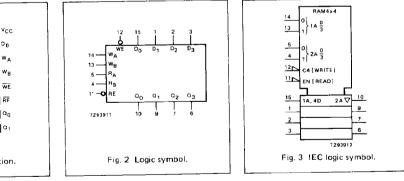

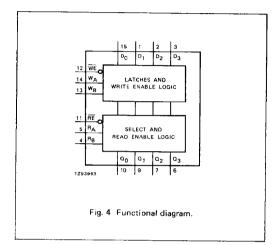

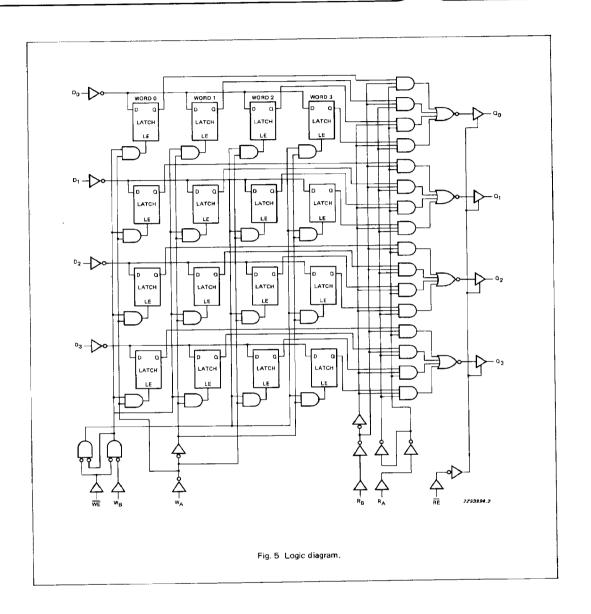

The 74HC/HCT670 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT670 are 16-bit 3-state register files organized as 4 words of 4 bits each. Separated read and write address inputs ( $R_A$ ,  $R_B$  and  $W_A$ ,  $W_B$ ) and enable inputs ( $R_E$  and  $W_E$ ) are available, permitting simultaneous writing into one word location and reading from another location. The 4-bit word to be stored is presented to four data inputs ( $D_0$  to  $D_3$ ). The  $W_A$  and  $W_B$  inputs determine the location of the stored word. When the  $\overline{WE}$  input is LOW, the data is entered into the addressed location. The addressed location remains transparent to the data while the WE input is LOW. Data supplied at the inputs will be read out in true (non-inverting) form from the 3-state outputs  $(Q_0 \text{ to } Q_3)$ .  $D_n \text{ and } W_n \text{ inputs are inhibited when WE is HIGH.}$

Direct acquisition of data stored in any Direct acquisition of data stored in any of the four registers is made possible by individual read address inputs (R<sub>A</sub> and R<sub>B</sub>). The addressed word appears at the four outputs when the RE is LOW. Data outputs are in the high impedance OFF-state when RE is HIGH. This permits outputs to be tied together to increase the word capacity to very large numbers.

(continued on next page)

|               |                                                       |                                                 | ТҮР |     |      |

|---------------|-------------------------------------------------------|-------------------------------------------------|-----|-----|------|

| SYMBOL        | PARAMETER                                             | CONDITIONS                                      | нс  | нст | UNIT |

| tPHL/<br>tPLH | propagation delay<br>D <sub>B</sub> to Q <sub>B</sub> | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | 23  | 23  | ns   |

| CI            | input capacitance                                     |                                                 | 3.5 | 3.5 | рF   |

| CPD           | power dissipation<br>capacitance per package          | notes 1 and 2                                   | 122 | 124 | рF   |

GND = 0 V;  $T_{amb}$  = 25 °C;  $t_r$  =  $t_f$  = 6 ns

Notes

- 1. CPD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

- $PD = CPD \times VCC^2 \times f_i + \Sigma (CL \times VCC^2 \times f_0)$  where: CL = output load capacitance in pF VCC = supply voltage in V

- $f_i = input frequency in MHz$   $f_0 = output frequency in MHz$

- $\Sigma (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs}$

- For HC the condition is VI = GND to VCC For HCT the condition is VI = GND to VCC 1.5 V

PACKAGE OUTLINES 16-lead DIL.; plastic (SOT38Z).

16-lead mini-pack; plastic (SO16; SOT109A).

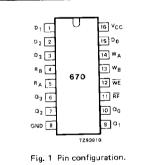

#### PIN DESCRIPTION

| PIN NO.     | SYMBOL                                 | L NAME AND FUNCTION                                           |  |  |  |  |

|-------------|----------------------------------------|---------------------------------------------------------------|--|--|--|--|

| 5, 4<br>8   | R <sub>A</sub> , R <sub>B</sub><br>GND | read address inputs<br>ground (0 V)                           |  |  |  |  |

| 10, 9, 7, 6 | 00 to 03                               | data outputs<br>3-state output read enable input (active LOW) |  |  |  |  |

| 11<br>12    | RE                                     | write enable input (active LOW)                               |  |  |  |  |

| 14, 13      | W <sub>A</sub> , W <sub>B</sub>        | write address inputs                                          |  |  |  |  |

| 15, 1, 2, 3 | D <sub>0</sub> to D <sub>3</sub>       | data inputs                                                   |  |  |  |  |

| 16          | Vcc                                    | positive supply voltage                                       |  |  |  |  |

777 December 1990

# 74HC/HCT670

MSI

# WRITE MODE SELECT TABLE

| OPERATING    | INP    | UTS    | INTERNAL  |

|--------------|--------|--------|-----------|

| MODE         | WE     | Dn     | LATCHES*  |

| write data   | L<br>L | L<br>H | L<br>H    |

| data latched | н      | х      | no change |

\* The write address (W<sub>A</sub> and W<sub>B</sub>) to the "internal latches" must be stable while WE is LOW for conventional operation.

# READ MODE SELECT TABLE

| OPERATING |        | INPUTS                | ουτρυτ         |  |

|-----------|--------|-----------------------|----------------|--|

| MODE      | RE     | INTERNAL<br>LATCHES** | 0 <sub>n</sub> |  |

| read      | L<br>L | L<br>H                | L<br>H         |  |

| disabled  | н      | х                     | z              |  |

\*\* The selection of the "internal latches" by read address (R<sub>A</sub> and R<sub>B</sub>) are not constrained by WE or RE operation.

778

H = HIGH voltage level L = LOW voltage level X = don't care Z = high impedance OFF-state

January 1986

# GENERAL DESCRIPTION (Cont'd)

GENERAL DESCHIPTION (Cont'd) Design of the read enable signals for the stacked devices must ensure that there is no overlap in the LOW levels which would cause more than one output to be active at the same time. Parallel expansion to generate n-bit words is accomplished by driving the enable and address inputs of each device in parallel.

4 x 4 register file; 3-state

March 1988

779

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see chapter "HCMOS family characteristics", section "Family specifications".

Output capability: bus driver ICC category: MSI

-

# AC CHARACTERISTICS FOR 74HC

$GND = 0 \text{ V; } t_r = t_f = 6 \text{ ns; } C_L = 50 \text{ pF}$

|                                       |                                                                        | T <sub>amb</sub> (°C) |                |                 |                 |                 |                 |                 |      | TEST CONDITIONS   |           |  |

|---------------------------------------|------------------------------------------------------------------------|-----------------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------|-------------------|-----------|--|

| SYMBOL                                | PARAMETER                                                              | PARAMETER 74HC        |                |                 | ]               |                 |                 |                 |      |                   |           |  |

|                                       |                                                                        |                       | +25            |                 | 40              | to +85          | -40 t           | o +125          | UNIT | Vcc<br>V          | WAVEFORMS |  |

|                                       |                                                                        | min.                  | typ.           | max.            | mìn.            | max.            | min.            | max,            | 1    |                   |           |  |

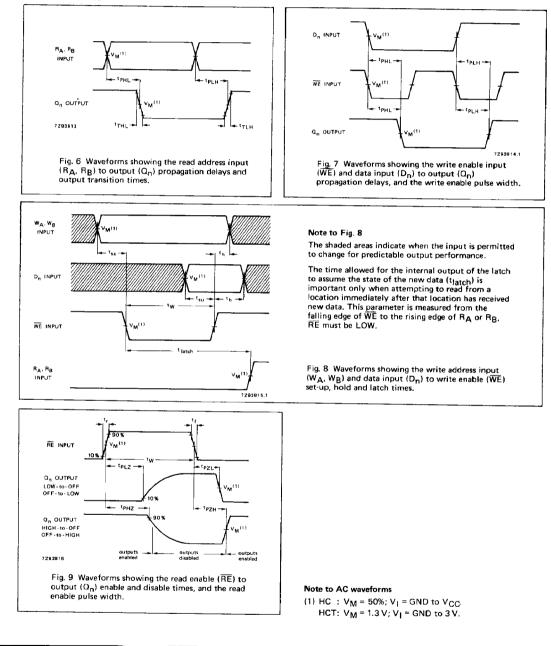

| <sup>t</sup> PHL/<br><sup>t</sup> PLH | propagation delay<br>R <sub>A</sub> , R <sub>B</sub> to Q <sub>R</sub> |                       | 58<br>21<br>17 | 195<br>39<br>33 |                 | 245<br>49<br>42 |                 | 295<br>59<br>50 | ns   | 2.0<br>4.5<br>6.0 | Fig. 6    |  |

| <sup>t</sup> РНL/<br>tРLН             | p <u>rop</u> agation delay<br>WE to Q <sub>n</sub>                     |                       | 77<br>28<br>22 | 250<br>50<br>43 |                 | 315<br>63<br>54 |                 | 375<br>75<br>64 | ns   | 2.0<br>4.5<br>6.0 | Fig. 7    |  |

| <sup>t</sup> PHL <sup>/</sup>         | propagation delay<br>D <sub>n</sub> to Q <sub>n</sub>                  |                       | 74<br>27<br>22 | 250<br>50<br>43 |                 | 315<br>63<br>54 |                 | 375<br>75<br>64 | ns   | 2.0<br>4.5<br>6.0 | Fig. 7    |  |

| <sup>tp</sup> ZH/<br><sup>t</sup> PZL | 3-state output enable time<br>RE to Q <sub>n</sub>                     |                       | 39<br>14<br>11 | 150<br>30<br>26 |                 | 190<br>38<br>33 |                 | 225<br>45<br>38 | ns   | 2.0<br>4.5<br>6.0 | Fig. 9    |  |

| <sup>t</sup> PHZ/<br>tPLZ             | 3-state output disable time<br>RE to Q <sub>n</sub>                    |                       | 47<br>17<br>14 | 150<br>30<br>26 |                 | 190<br>38<br>33 |                 | 225<br>45<br>38 | ns   | 2.0<br>4.5<br>6.0 | Fig. 9    |  |

| tTHL/<br>tTLH                         | Output transition time                                                 |                       | 14<br>5<br>4   | 60<br>12<br>10  |                 | 75<br>15<br>13  |                 | 90<br>18<br>15  | ns   | 2.0<br>4.5<br>6.0 | Fig. 6    |  |

| tw                                    | write enable pulse width<br>LOW                                        | 80<br>16<br>14        | 14<br>5<br>4   |                 | 100<br>20<br>17 |                 | 120<br>24<br>20 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig. 8    |  |

| t <sub>su</sub>                       | set-up time<br>D <sub>n</sub> to WE                                    | 60<br>12<br>10        | 3<br>1<br>1    |                 | 75<br>15<br>13  |                 | 90<br>18<br>15  |                 | ns   | 2.0<br>4.5<br>6.0 | Fig. 8    |  |

| t <sub>su</sub>                       | set-up time<br>W <sub>A</sub> , W <sub>B</sub> to WE                   | 60<br>12<br>10        | 6<br>2<br>2    |                 | 75<br>15<br>13  |                 | 90<br>18<br>15  |                 | ns   | 2.0<br>4.5<br>6.0 | Fig. 8    |  |

| t <sub>h</sub>                        | hold time<br>D <sub>n</sub> to WE                                      | 5<br>5<br>5           | 0<br>0<br>0    |                 | 5<br>5<br>5     |                 | 5<br>5<br>5     |                 | ns   | 2.0<br>4.5<br>6.0 | Fig. 8    |  |

| th                                    | hold time $W_A, W_B$ to $\overline{WE}$                                | 5<br>5<br>5           | 0<br>0<br>0    |                 | 5<br>5<br>5     |                 | 5<br>5<br>5     |                 | ns   | 2.0<br>4.5<br>6.0 | Fig. 8    |  |

| Hatch                                 | latch time<br>WE to R <sub>A</sub> , R <sub>B</sub>                    | 100<br>20<br>17       | 28<br>10<br>8  |                 | 125<br>25<br>21 |                 | 150<br>30<br>26 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig. 8    |  |

780

. . ......

March 1988

# DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see chapter "HCMOS family characteristics", section "Family specifications".

Output capability: bus driver ICC category: MSI

## Note to HCT types

The value of additional quiescent supply current ( $\Delta$ ICC) for a unit load of 1 is given in the family specifications. To determine  $\Delta$ ICC per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT              | UNIT LOAD            | IN       | PUT | UNIT LOAD<br>COEFFICIENT |  |  |

|--------------------|----------------------|----------|-----|--------------------------|--|--|

| Dn<br>WE, WA<br>WB | 0.25<br>0.40<br>0.60 | RA<br>RE | i.  | 0.70<br>1.10<br>1.35     |  |  |

# AC CHARACTERISTICS FOR 74HCT

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                                   |                                                                     | T <sub>amb</sub> (℃) |      |            |      |             |      |      | TEST CONDITIONS |     |        |

|---------------------------------------------------|---------------------------------------------------------------------|----------------------|------|------------|------|-------------|------|------|-----------------|-----|--------|

| SYMBOL                                            |                                                                     |                      |      |            | 74HC | HCT         | UNIT | Vcc  | WAVEFORMS       |     |        |

|                                                   | PARAMETER                                                           | +25                  |      | -40 to +85 |      | -40 to +125 |      |      |                 |     |        |

|                                                   |                                                                     | min.                 | typ. | max.       | min. | max.        | min. | max. | ]               |     |        |

| tPHL/<br>tPLH                                     | propagation delay $B_A$ , $B_B$ to $Q_n$                            |                      | 21   | 40         |      | 50          |      | 60   | ns              | 4.5 | Fig. 6 |

| tPHL/<br>tPLH                                     | propagation delay<br>WE to Q <sub>n</sub>                           |                      | 28   | 50         |      | 63          |      | 75   | ns              | 4.5 | Fig. 7 |

| <sup>t</sup> PHL <sup>/</sup><br><sup>t</sup> PLH | propagation delay $D_n$ to $Q_n$                                    |                      | 27   | 50         |      | 63          |      | 75   | ns              | 4.5 | Fig. 7 |

| <sup>t</sup> PZH <sup>/</sup><br><sup>t</sup> PZL | $\frac{3\text{-state output enable time}}{RE \text{ to } \Omega_n}$ |                      | 18   | 35         |      | 44          |      | 53   | ns              | 4.5 | Fig. 9 |

| tPHZ/<br>tPLZ                                     | $\frac{3\text{-state output disable time}}{\text{RE to } Q_n}$      |                      | 19   | 35         |      | 44          |      | 53   | ns              | 4.5 | Fig. 9 |

| tthl/<br>ttlh                                     | output transition time                                              |                      | 5    | 12         |      | 15          |      | 18   | ns              | 4.5 | Fig. 6 |

| tw                                                | write enable pulse width LOW                                        | 18                   | 9    |            | 23   |             | 27   |      | ns              | 4.5 | Fig. 8 |

| t <sub>su</sub>                                   | set-up time<br>D <sub>n</sub> to WE                                 | 12                   | 4    |            | 15   |             | 18   | 1    | ns              | 4.5 | Fig. 8 |

| t <sub>su</sub>                                   | set-up time<br>WA, WB to WE                                         | 12                   | -2   |            | 15   |             | 18   |      | ns              | 4.5 | Fig. 8 |

| th                                                | hold time<br>D <sub>n</sub> to WE                                   | 5                    | -1   |            | 5    |             | 5    |      | ns              | 4.5 | Fig. 8 |

| th                                                | hold time<br>W <sub>A</sub> , W <sub>B</sub> to WE                  | 5                    | 0    |            | 5    |             | 5    |      | ns              | 4.5 | Fig. 8 |

| tlatch                                            | latch time<br>WE to R <sub>A</sub> , R <sub>B</sub>                 | 25                   | 11   |            | 31   |             | 38   |      | ns              | 4.5 | Fig. 8 |

March 1988

This Material Copyrighted By Its Respective Manufacturer

781

AC WAVEFORMS

782 January 1986

January 1900