8274

B.F.W PACKAGES

# DIGITAL 8000 SERIES TTL/MSI

## DESCRIPTION

The 8274 10-Bit Shift Register is an array of binary elements interconnected to perform the parallel-in, serial-out shift function. The circuit has ten parallel inputs and a single true serial output. The D1 input can also be used for serial entry. Two control inputs, S0 and S1, determine the operating mode of the shift register as shown in the Truth Table. A single buffered clock line connects all ten flip-flops which are activated on the high-to-low transition of the clock pulse. Guaranteed input clock frequency is 25MHz. With the exception of the Hold Mode, the control inputs may be changed when the clock is in either the high or low state without causing false triggering. The Hold Mode can be entered only when the clock is low. Applications for the 8274 Shift Register include Parallel-to-Serial conversion,

Modem Data Transmission, Pseudo-Random Code generation and Modulo-N Frequency Division.

#### **TRUTH TABLE**

| s <sub>o</sub> | s <sub>1</sub> | OPERATING MODE |

|----------------|----------------|----------------|

| 0              | 0              | Hold           |

| 0              | 1              | Clear          |

| 1              | o              | Load           |

| 1              | 1              | Shift          |

|                |                |                |

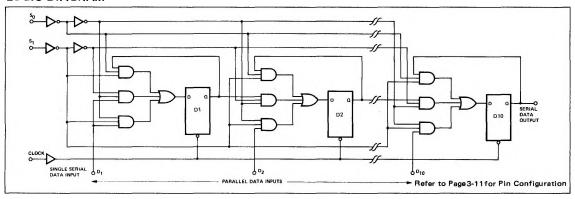

#### LOGIC DIAGRAM

## ELECTRICAL CHARACTERISTICS (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS                   |      | LIMITS |      |       | TEST CONDITIONS |                |                |       |         | NOTES |

|-----------------------------------|------|--------|------|-------|-----------------|----------------|----------------|-------|---------|-------|

|                                   | MIN. | TYP.   | MAX. | UNITS | D <sub>n</sub>  | s <sub>o</sub> | s <sub>1</sub> | CLOCK | OUTPUTS | NOTES |

| "1" Output Voltage                | 2.6  | 3.4    |      | V     | 2.0V            | 2.0V           | 2.0V           | Pulse | -800µA  | 6     |

| "0" Output Voltage                |      | 0.2    | 0.4  | v     | 0.8∨            | 2.0V           | 2.0V           | Pulse | 16mA    | 7     |

| "0" Input Current                 |      |        | ļ    |       |                 |                |                | 1     |         |       |

| D <sub>n</sub>                    | -0.2 |        | -1.2 | mA    | 0.4∨            |                |                |       |         |       |

| S <sub>0</sub> and S <sub>1</sub> | -0.2 |        | -1.2 | mA    |                 | 0.4∨           | 0.4∨           |       |         |       |

| Clock                             | ÷0.2 |        | -1.6 | mA    |                 |                |                | 0.4V  |         |       |

| "1" Input Current                 |      |        |      |       |                 |                |                |       | ļ       |       |

| D <sub>n</sub>                    |      |        | 40   | μА    | 4.5V            |                |                | }     |         |       |

| S <sub>0</sub> and S <sub>1</sub> |      |        | 40   | μА    |                 | <b>4</b> .5V   | 4.5V           |       |         |       |

| Clock                             |      |        | 40   | μА    |                 |                |                | 4.5V  |         |       |

$T_A = 25^{\circ} C$  and  $V_{CC} = 5.0 V$

| CHARACTERISTICS                   | LIMITS |        |         | TEST CONDITIONS |               |                |                |       |        |       |

|-----------------------------------|--------|--------|---------|-----------------|---------------|----------------|----------------|-------|--------|-------|

|                                   | MIN.   | TYP.   | MAX.    | UNITS           | Dn            | s <sub>o</sub> | S <sub>1</sub> | CLOCK | ООТРОТ | NOTES |

| Data Transfer Rate                | 25MHz  | 30     |         | MHz             |               |                |                |       |        | 10    |

| Turn-On Delay (Clock to Output)   |        | 27     | 40      | ns              |               |                |                |       |        | 10    |

| Turn-Off Delay (Clock to Output)  |        | 21     | 40      | ns              |               |                |                |       |        | 10    |

| Clock Pulse Width                 |        | 15     | 20      | ns              |               |                |                |       |        | 10    |

| Set-Up Time (t <sub>setup</sub> ) |        |        |         |                 |               |                |                |       |        | 10    |

| D <sub>n</sub>                    |        | 16     | 10      | ns              |               |                |                | ļ     |        |       |

| s <sub>0</sub> , s <sub>1</sub>   |        | 16     | 25      | ns              |               |                |                |       |        |       |

| Hold Time (thold)                 |        |        |         |                 |               |                |                |       |        |       |

| D <sub>n</sub>                    |        | 2      | 15      | ns              |               |                |                |       |        | Ì     |

| s <sub>0</sub> , s <sub>1</sub>   |        | 16     | 25      | ns              |               |                |                |       |        |       |

| Power Consumption/Supply Current  |        | 380/72 | 567/108 | mW              | 4.5V          | 4.5V           | 4.5V           | 0∨    |        | 8     |

| Short Circuit Output Current      | -20    |        | -70     | mA              | 2. <b>0</b> V | 2.0V           | 2.0V           | Pulse | 0.0∨   | 8,9   |

| Input Voltage Rating              | 5.5    |        |         | l v             | 10mA          |                |                |       |        |       |

#### NOTES:

- All voltage and capacitance measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- All measurements are taken with ground pin tied to zero volts.

- 3. Positive current flow is defined as into the terminal referenced.

- 4. Positive logic definition:

- "UP" Level = "1", "DOWN" Level = "0".

- 5. Precautionary measures should be taken to ensure current

- limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- Output source current is supplied through a resistor to ground.

- 7. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 8. V<sub>CC</sub> = 5.25V.

- 9. Not more than one output should be shorted at one time.

- 10. See AC Test Figure.

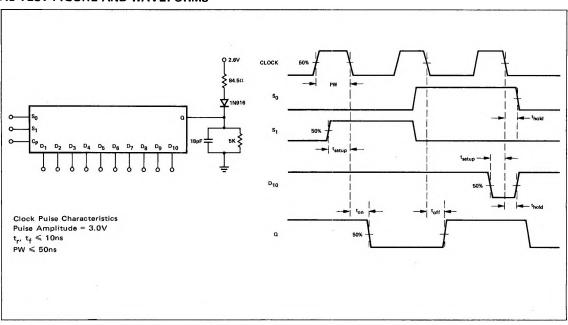

# AC TEST FIGURE AND WAVEFORMS