ISL GATE ARRAY 8A1664

## **FEATURES**

- Customer programmable LSI

- 1560 ISL (NAND) gates

- Two-layer metal interconnection

- · 60 Schottky buffers

- 64 I/O buffers

- LS TTL compatible

- Standard PNP inputs

- 8-, or 24-milliamperes output current sink

- -55°C to +125°C ambient temperature

- · 4-nanosecond gate speed (typical)

- Speed-power product 0.7 picojoules

- 68 pin package

## PRODUCT DESCRIPTION

The 8A1664 Gate Array (Figure 1) is an uncommitted array of ISL gates (Figure 2), Schottky Buffers (Figure 3), and the LSTTL compatible I/O cells. Thus, up to 1600 gates can be custom interconnected to provide the advantages of both Large Scale Integration (LSI) and proprietary design. The 8A1664 array is based on a technological subset of LSI called ISL (Integrated Schottky Logic). ISL combines the

features of Schottky and the density of I<sup>2</sup>L Bipolar technologies.

Designing with the 8A1664 is easy and fast, requiring no more than conventional logic design, logic simulation, and custom coding of metal interconnections among preprocessed logic gates on the array. The design techniques and the implementation processes are analogous to the design of a Printed Circuit Board.

Logic functions are defined by the user and are implemented by interconnecting 1560 ISL NAND gates, using two layers of metal routing. Sixty Schottky buffers are provided to drive multi-load internal clock or enable signals. For external interface, up to 64 LS TTL I/O buffers can be specified. Each 8-milliampere I/O site can be configured as 1-of-6 input/internal buffers or as 1-of-8 output buffers; each 24-milliampere I/O site can also be configured as 1-of-6 input/internal buffers but the output buffer configuration can be 1-of-12. For a transceiver, either I/O site can be connected in combinations of one input and one output buffer.

## ORDERING INFORMATION

Contact Local Sales Representative

Figure 1. Internal Configuration of 8A1664

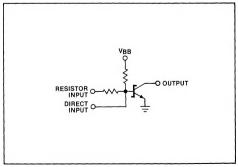

Figure 2. ISL Gate — Schematic Diagram

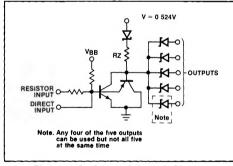

Figure 3. Schottky Buffer — Schematic Diagram