# Two s Complement Dual, 12-Bit DACs

# **Preliminary Technical Data**

**AD5329**

## **FEATURES**

- Monotonic DNL < ±1 LSB</li>

- Improved Accuracy at Zero Scale

- Fast 2μs Settling Time

- Power ON Reset

- 3-Wire Serial Data Input

- 25MHz Data Load Rate

- Internal Reference Voltage

- +4.5V to +5.5V Single Supply Operation

### **APPLICATIONS**

· Digital Control of Gain & Offset

#### GENERAL DESCRIPTION

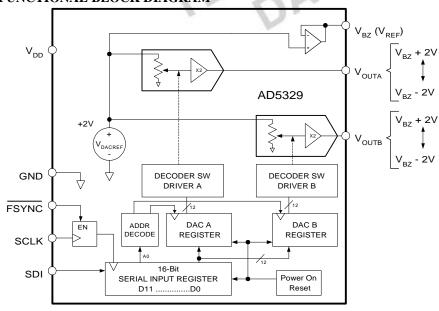

The AD5329 is a serial-input, dual 12-bit digital-to-analog converter that accepts two's complement digital coding. An internal voltage reference generates a stable 2V DACREF. The buffered DACREF output generates the system bipolar ground reference at pin  $V_{BZ}$ . The bipolar DAC output swing programs over a  $4V_{PP}$  range. The device is specified for operation from +5 volts  $\pm 10\%$ .

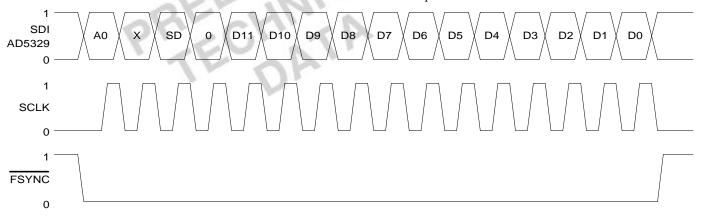

Data is loaded MSB first on the positive clock edge (SCLK) when the frame synch (*FSYNC*) input is active low. The serial clock input word is 16-bits with the MSB position containing an address bit. The last 12

data bits clocked into the register will be transferred to the internal DAC register when the strobe input is returned to logic high.

The output transfer equation is:

$V_{OUT} = [(D-2048) / 4096 * V_{DACREF}] + V_{BZ}$

Where D is the 12-bit decimal data, and  $V_{\text{OUT}},\,V_{\text{DACREF}},\,V_{\text{BZ}}$  are with respect to ground.

The AD5329 is available in the compact 1.1mm thin  $\mu$ SOIC-10 package. All parts are guaranteed to operate over the industrial temperature range of 0°C to +70°C.

### PIN CONFIGURATION

|                     | _ |                   |

|---------------------|---|-------------------|

| V <sub>DD</sub> 1   |   | 10 GND            |

| SDA 2               |   | 9 SCLK            |

| NC 3                |   | 8 FSYNC           |

| V <sub>OUTB</sub> 4 |   | 7 NC              |

| V <sub>OUTA</sub> 5 |   | 6 V <sub>BZ</sub> |

|                     |   |                   |

#### ORDERING GUIDE

|                 | RES    | Temp    | Package     | Package |

|-----------------|--------|---------|-------------|---------|

| Model           | (bits) | Range   | Description | Option  |

| AD5329KRM-REEL7 | 12     | 0/+70°C | μSOIC-10    | RM-10   |

## FUNCTIONAL BLOCK DIAGRAM

REV PrC, 20 DEC 99

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781/329-4700 Fax:617/326-8703 World Wide Web Site: http://www.analog.com ©Analog Devices, Inc., 1998

# **AD5329 -- SPECIFICATIONS**

## ELECTRICAL CHARACTERISTICS (Vpp = +5V±10%, 0°C < TA < +70°C unless otherwise noted.)

| Parameter Parameter                                                                                                                                                                                                                                         |                                                                                                                          | <b>&gt;</b> (V <sub>DD</sub> = +5V±10%, 0°C < T <sub>A</sub> < +70°C unless oth<br><b>Conditions</b>                                                                        | nerwise noted.)  Min                         | Typ <sup>1</sup>                                        | Max                                          | Units                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|----------------------------------------------|------------------------------------------|

| DC CHARACTERISTICS                                                                                                                                                                                                                                          |                                                                                                                          |                                                                                                                                                                             |                                              |                                                         |                                              |                                          |

| Resolution Differential Nonlinearity Error Integral Nonlinearity Error Integral Nonlinearity Error Integral Nonlinearity Error Full-Scale Temperature Coefficient <sup>2</sup> Positive-Full-Scale Error Bipolar-Zero-Scale Error Negative-Full-Scale Error | N<br>DNL<br>INL<br>INL<br>ΔV <sub>FS</sub> /ΔT<br>V <sub>+FSE</sub><br>V <sub>BZSE</sub><br>V <sub>-FSE</sub>            | Within 256 codes of V <sub>BZ</sub> Code = 7FF <sub>H</sub> Code = 7FF <sub>H</sub> Code = 000 <sub>H</sub> Code = 800 <sub>H</sub>                                         | 12<br>1<br>0.05<br>0.02<br>0.1<br>0.1<br>0.1 | ±0.5<br>±0.02<br>±0.01<br>100<br>-0.05<br>+0.1<br>-0.05 | +1<br>+0.05<br>+0.02<br>+0.1<br>+0.1<br>+0.1 | Bits LSB %FS %FS ppm/°C %FS V %FS        |

| ANALOG OUTPUTS                                                                                                                                                                                                                                              |                                                                                                                          |                                                                                                                                                                             |                                              |                                                         |                                              |                                          |

| Nominal Positive Full-Scale<br>Positive Full-Scale Tempco <sup>2</sup><br>Nominal V <sub>BZ</sub> Output Voltage<br>Bipolar-Zero Output Resistance <sup>2</sup><br>Nominal Peak-Peak Output Swing                                                           | VOUTA/B<br>TCVOUTA/B<br>VBZ<br>RBZ<br> V+FS  +  V-FS                                                                     | Code = 7FF <sub>H</sub> Code = 7FF <sub>H</sub> Code 7FF <sub>H</sub> to Code 800 <sub>H</sub>                                                                              |                                              | 4<br>±100<br>2<br>1<br>4                                |                                              | Volts<br>ppm/°C<br>Volts<br>Ohm<br>Volts |

| DIGITAL INPUTS                                                                                                                                                                                                                                              |                                                                                                                          |                                                                                                                                                                             |                                              |                                                         |                                              |                                          |

| Input Logic High<br>Input Logic Low<br>Input Current<br>Input Capacitance <sup>2</sup>                                                                                                                                                                      | V <sub>IH</sub> V <sub>IL</sub> I <sub>IL</sub> C <sub>IL</sub>                                                          | $V_{DD} = +5V$<br>$V_{DD} = +5V$<br>$V_{IN} = 0V \text{ or } +5V, V_{DD} = +5V$                                                                                             | 2.4                                          | 5                                                       | 0.8<br>±1                                    | V<br>V<br>µA<br>pF                       |

| POWER SUPPLIES                                                                                                                                                                                                                                              | -1.1                                                                                                                     | 110                                                                                                                                                                         |                                              |                                                         |                                              |                                          |

| Power Supply Range Supply Current Supply Current in Shutdown Power Dissipation <sup>3</sup> Power Supply Sensitivity                                                                                                                                        | V <sub>DD Range</sub> I <sub>DD</sub> I <sub>DD_SHDN</sub> P <sub>DISS</sub> PSS                                         | $V_{IH} = V_{DD}$ or $V_{IL} = 0V$<br>$V_{IH} = V_{DD}$ or $V_{IL} = 0V$ , B14=0<br>$V_{IH} = V_{DD}$ or $V_{IL} = 0V$ , $V_{DD} = +5.5V$<br>$\Delta V_{DD} = +5V \pm 10\%$ | 4.5                                          | 2.5<br>40<br>12.5<br>0.0002                             | 5.5<br>0.01                                  | V<br>mA<br>μA<br>mW<br>%/%               |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                                                                                                                                                                                                                        |                                                                                                                          |                                                                                                                                                                             |                                              |                                                         |                                              |                                          |

| Settling Time                                                                                                                                                                                                                                               | t <sub>S</sub>                                                                                                           | For a 16 LSB step change                                                                                                                                                    |                                              | 2                                                       | 3                                            | μs                                       |

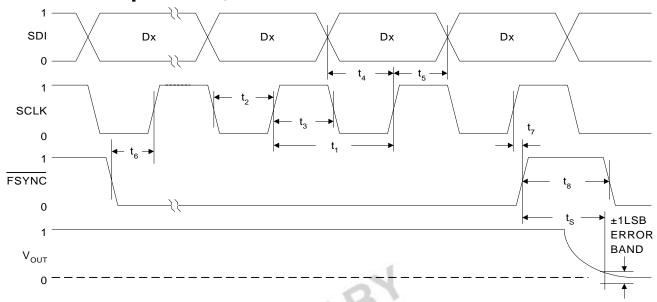

| INTERFACE TIMING CHARACTERISTICS <sup>2,4</sup>                                                                                                                                                                                                             |                                                                                                                          |                                                                                                                                                                             |                                              |                                                         |                                              |                                          |

| SCLK Clock Cycle time Input Clock Pulse Width Data Setup Time Data Hold Time FSYNC to SCLK active edge Setup Time SCLK to FSYNC Hold Time                                                                                                                   | t <sub>1</sub><br>t <sub>2</sub> ,t <sub>3</sub><br>t <sub>4</sub><br>t <sub>5</sub><br>t <sub>6</sub><br>t <sub>7</sub> | Clock level low or high                                                                                                                                                     | 35<br>20<br>5<br>5<br>10                     |                                                         |                                              | ns<br>ns<br>ns<br>ns<br>ns               |

| Minimum FSYNC High Time                                                                                                                                                                                                                                     | t <sub>8</sub>                                                                                                           |                                                                                                                                                                             | 35                                           |                                                         |                                              | ns                                       |

## NOTES:

Typicals represent average readings at +25°C and V<sub>DD</sub> = +5V.

Guaranteed by design and not subject to production test.

<sup>3.</sup> PDISS is calculated from (IDD x VDD). CMOS logic level inputs result in minimum power dissipation.

<sup>4.</sup> See timing diagram for location of measured values. All input control voltages are specified with t<sub>R</sub>=t<sub>F</sub>=2ns(10% to 90% of +3V) and timed from a voltage level of 1.5V. Switching characteristics are measured using V<sub>DD</sub> = +5V. Input logic should have a 1V/µsec minimum slew rate.

# Two s Complement, Dual 12-Bit DAC

# AD5329

| <b>ABSOLUTE MAXIMUM RATINGS</b> ( $T_A = +25$ °C, unless        |

|-----------------------------------------------------------------|

| otherwise noted)                                                |

| $V_{DD}$ to GND0.3,+6V                                          |

| $V_{OUTA},V_{OUTB},V_{BZ}toGND0V,V_{DD}$                        |

| Digital Input Voltages to GND $0V$ , $V_{DD} + 0.3V$            |

| Operating Temperature Range0°C to +70°C                         |

| $Maximum\ Junction\ Temperature\ (T_J \text{MAX})+150^{\circ}C$ |

| Storage Temperature65°C to +150°C                               |

| Lead Temperature (Soldering, 10 sec)+300°C                      |

| Package Power Dissipation(T_JMAX - $T_A) \; / \; \theta_{JA}$   |

| Thermal Resistance $\theta_{JA}$ ,                              |

| uSOIC-10 206°C/W                                                |

## **AD5329 Two's Complement Coding**

| Binar | Y    |      | <u>H</u> | <u>Hexadecimal</u> |   | al <u>Scale</u> |

|-------|------|------|----------|--------------------|---|-----------------|

| 0111  | 1111 | 1111 | 7        | F                  | F | +FS             |

| 0111  | 1111 | 1110 | 7        | F                  | F | +FS-1LSB        |

| 0000  | 0000 | 0001 | 0        | ٥                  | 1 | BZS+1LSB        |

|       |      | 0000 | -        | -                  | _ | BZS             |

|       |      | 1111 | -        | F                  | - | BZS-1LSB        |

| 1111  | 1111 | 1111 | F        | F                  | F | DZ5-115B        |

| 1000  | 0000 | 0001 | 8        | 0                  | 1 | -FS+1LSB        |

| 1000  | 0000 | 0000 | 8        | 0                  | 0 | -FS             |

**TABLE 2:** AD5329 PIN Descriptions

| Pin | Name                | Description                                    |

|-----|---------------------|------------------------------------------------|

| 1   | $V_{\mathrm{DD}}$   | Positive power supply, specified for operation |

|     |                     | at +5V.                                        |

| 2   | SDA                 | Serial Data Input, MSB first format            |

| 3   | NC                  | No Connect                                     |

| 4   | $V_{\mathrm{OUTB}}$ | DAC B Voltage Output (A0 = logic "1")          |

| 5   | $V_{\text{OUTA}}$   | DAC A Voltage Output (A0 = logic "0")          |

| 6   | $ m V_{BZ}$         | Virtual Bipolar Zero (Active Output)           |

| 7   | NC                  | No Connect                                     |

| 8   | FSYNC               | Frame Sync Input, Active Low. When FSYNC       |

|     |                     | returns HIGH data in the serial input register |

|     |                     | is transferred into the DAC register.          |

| 9   | SCLK                | Serial Clock Input, positive edge triggered    |

| 10  | GND                 | Ground                                         |

TABLE 1: AD5329 Serial-Data Word Format

| ADD        | R   |            |     | DAT        | A   |            |           |           |           |           |

|------------|-----|------------|-----|------------|-----|------------|-----------|-----------|-----------|-----------|

| <b>B16</b> | B15 | <b>B14</b> | B13 | <b>B12</b> | B11 | <>         | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> |

| A0         | X   | SD         | 0   | D11        | D10 | $\Diamond$ | D3        | D2        | D1        | D0        |

| MSB        |     |            |     |            |     |            |           |           |           | LSB       |

| 100        |     |            |     |            |     |            |           |           |           |           |

SD: Shutdown is active high B14="1". Both DACs and the DACREF becomes open circuit.

Figure 1A. Timing Diagram

# Two s Complement, Dual 12-Bit DAC

# **AD5329**

Figure 1B. Detail Timing Diagram

## **OPERATION**

The AD5329 provides a 12-bit, 2's complement, dual, voltage-output digital-to-analog converter. The first data bit of the 16-bit serial register is decoded to determine which DAC register (DAC A: A0= "0", DAC B: A0= "1") will be loaded with the final 12-bits of data.

**TABLE 3: Input Logic Control Truth Table**

| SCLK | FSYNC | Register Activity                  |

|------|-------|------------------------------------|

| L    | Н     | No Shift Register Effect           |

| P    | L     | Shift One bit in from the SDA pin. |

| L    | P     | Transfer SR data into DAC Register |

| X    | L     | No Operation                       |

NOTE: P = positive edge, X = don't care, SR = Shift Register

The data setup and data hold times in the specification table determine the data valid time requirements. The last 12 bits of the data word entered into the serial register are held when FSYNC returns high.

The internal power ON reset circuit clears the serial input registers to all zeros, and sets the two DAC registers to  $V_{BZ}$  (zero code).

All digital inputs are ESD protected with a series input resistor and parallel Zener as shown in figure 7. Applies to digital input pins SCLK, SDA, FSYNC

Figure 7. Equivalent ESD Protection Circuit

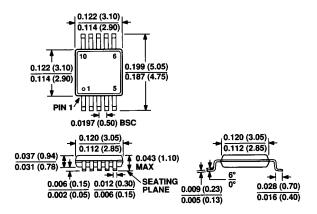

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm)

10-Lead μSOIC (RM-10)