## ANALOG DEVICES

# Low-Power CMOS Analog Front End with Flash based DSP Microcomputer

## **Preliminary Technical Data**

## AD73511

#### FEATURES

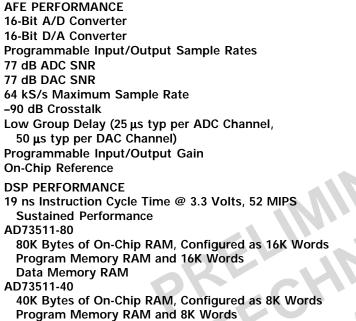

FUNCTIONAL BLOCK DIAGRAM

Data Memory RAM

FLASH Memory

64 kbytes

Writable in pages of 128 bytes Fast Page Write Cycle of 5 ms (typical)

#### **GENERAL DESCRIPTION**

The AD73511 is a single-device incorporating a single analog front end, microcomputer optimized for digital signal processing (DSP) and a FLASH based boot memory for the DSP.

The AD73511's analog front end (AFE) section is suitable for general purpose applications including speech and telephony. The AFE section features a 16-bit A/D converter and a 16-bit D/A converter. Each converter provides 77 dB signal-to-noise ratio over a voiceband signal bandwidth.

The AD73511 is particularly suitable for a variety of applications in the speech and telephony area including low bit rate, high quality compression, speech enhancement, recognition and synthesis. The low group delay characteristic of the AFE makes it suitable for single or multichannel active control applications. The A/D and D/A conversion channels feature programmable input/ouput gains with ranges 38 dB and 21 dB respectively. An on-chip reference voltage is included to allow single supply operation.

#### REV. PrA 08/99

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

The sampling rate of the AFE is programmable with four separate settings offering 64, 32, 16 and 8 kHz sampling rates (from a master clock of 16.384 MHz) while the serial port (SPORT2) allows easy expansion of the number of I/O channels by cascading extra AFEs external to the AD73511.

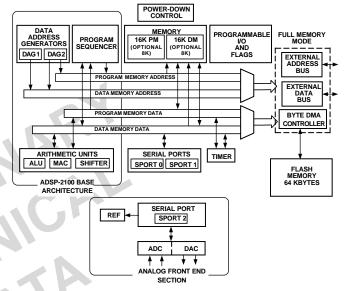

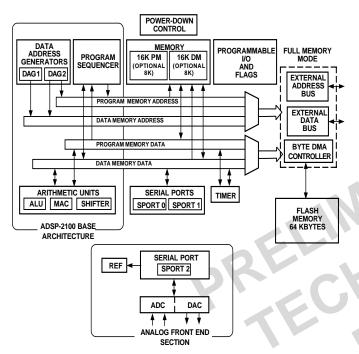

The AD73511's DSP engine combines the ADSP-2100 family base architecture (three computational units, data address generators and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities and on-chip program and data memory.

The AD73511-80 integrates 80K bytes of on-chip memory configured as 16K words (24-bit) of program RAM, and 16K words (16-bit) of data RAM. The AD73511-40 integrates 40K bytes of on-chip memory configured as 8K words (24bit) of program RAM, and 8K words (16-bit) of data RAM. Both devices feature a Flash memory array of 64 kbytes (512 kbits) connected to the DSP's byte-wide DMA port (BDMA). This allows non-volatile storage of the DSP's boot code and system data parameters. Power-down circuitry is also provided to meet the low power needs of battery operated portable equipment. The AD73511 is available in a 119-ball PBGA package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 Analog Devices, Inc., 1998

## AD73511

#### **ARCHITECTURE OVERVIEW**

The AD73511 instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Every instruction can be executed in a single processor cycle. The AD73511 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

#### Figure 1. Functional Block Diagram

Figure 1 is an overall block diagram of the AD73511. The processor section contains three independent computational units: the ALU, the multiplier/accumulator (MAC) and the shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/ subtract operations with

40 bits of accumulation. The shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations.

The internal result (R) bus connects the computational units so that the output of any unit may be the input of any unit on the next cycle.

## **Preliminary Technical Data**

A powerful program sequencer and two dedicated data address generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps, subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the AD73511 executes looped code with zero overhead; no explicit jump instructions are required to maintain loops.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches (from data memory and program memory). Each DAG maintains and updates four address pointers. Whenever the pointer is used to access data (indirect addressing), it is post-modified by the value of one of four possible modify registers. A length value may be associated with each pointer to implement automatic modulo addressing for

circular buffers.

The two address buses (PMA and DMA) share a single external address bus, allowing memory to be expanded offchip, and the two data buses (PMD and DMD) share a single external data bus. Byte memory space and I/O memory space also share the external buses.

An interface to low cost byte-wide memory is provided by the Byte DMA port (BDMA port). The BDMA port is bidirectional and can directly address up to four megabytes of external RAM or ROM for off-chip storage of program overlays or data tables.

The AD73511 can respond to eleven interrupts. There can be up to six external interrupts (one edge-sensitive, two levelsensitive and three configurable) and seven internal interrupts generated by the timer, the serial ports (SPORTs), the Byte DMA port and the power-down circuitry. There is also a master RESET signal. The two serial ports provide a complete synchronous serial interface with optional companding in hardware and a wide variety of framed or frameless data transmit and receive modes of operation.

Each port can generate an internal programmable serial clock or accept an external serial clock.

The AD73511 provides up to 13 general-purpose flag pins. The data input and output pins on SPORT1 can be alternatively configured as an input flag and an output flag. In addition, there are eight flags that are programmable as inputs or outputs and three flags that are always outputs.

A programmable interval timer generates periodic interrupts. A 16-bit count register (TCOUNT) is decremented every n processor cycle, where n is a scaling value stored in an 8-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

#### AD73511

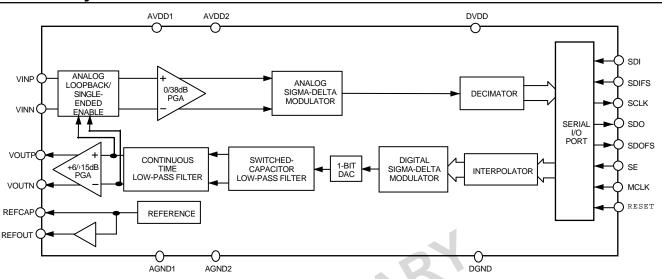

Figure 2: Functional Block Diagram of Analog Front End Section

#### **Analog Front End**

The AFE section is configured as a separate block which is normally connected to either SPORT0 or SPORT1 of the DSP section. As it is not hard-wired to either SPORT the user has total flexibility in how they wish to allocate system resources to support the AFE. It is also possible to further expand the number of analog I/O channels connected to the SPORT by cascading other single or dual channel AFEs (AD73311 or AD73322) external to the AD73511.

The AFE is configured as a single I/O channel (similar to that of the discrete AD73311L - refer to the AD73311L datasheet for more details) having a 16-bit sigma-delta based ADC and DAC. Both ADC and DAC share a common reference whose nominal value is 1.2V. Figure 2 shows a block diagram of the AFE section of the AD73511. It shows an ADC and DAC as well as a common reference. Communication to both channels is handled by the SPORT2 block which interfaces to either SPORT0 or SPORT1 of the DSP section. The I/O channel features fully differential inputs and outputs. The input section allows direct connection to the internal Programmable Gain Amplifier at the input of the sigma-delta ADC section. The input section also features programmable differential channel inversion and configuration of the the differential input as two separate single-ended inputs. The ADC features a second order sigmadelta modulator which samples at MCLK/8. Its bitstream output is filtered and decimated by a Sinc-cubed decimator to provide a sample rate selectable from 64 kHz, 32 kHz, 16 kHz or 8 kHz (based on an MCLK of 16.384 MHz).

The DAC channel features a Sinc-cubed interpolator which increases the sample rate from the selected rate to the digital sigma-delta modulator rate of MCLK/8. The digital sigma-delta modulator's output bit-stream is fed to a single-bit DAC whose output is reconstructed/filtered by two stages of low-pass filtering (switched capacitor and continuous time) before being applied to the differential output driver.

## $\label{eq:AD73511-SPECIFICATIONS} \begin{array}{l} (\text{AVDD} = \text{DVDD} = +3.0\text{V to } 3.6\text{V}; \ \text{DGND} = \text{AGND} = 0 \ \text{V}, \ f_{\text{MCLK}} = 16.384 \ \text{MHz}, \\ f_{\text{SAMP}} = 64 \ \text{kHz}; \ T_{\text{A}} = T_{\text{MIN}} \ \text{to} \ T_{\text{MAX}}, \ \text{unless otherwise noted}) \end{array}$

| PARAMETER                                  | Min  | Тур    | Max  | Units  | Test Conditions                                                           |

|--------------------------------------------|------|--------|------|--------|---------------------------------------------------------------------------|

| AFE SECTION                                |      |        |      |        |                                                                           |

| REFERENCE                                  |      |        |      |        |                                                                           |

| REFCAP                                     |      |        |      |        |                                                                           |

| Absolute Voltage, V <sub>REFCAP</sub>      | 1.08 | 1.2    | 1.32 | V      |                                                                           |

| REFCAP TC                                  |      | 50     |      | ppm/°C | 0.1 µF Capacitor Required from                                            |

| REFOUT                                     |      |        |      |        | <b>REFCAP to AGND2</b>                                                    |

| Typical Output Impedance                   |      | 145    |      | Ω      |                                                                           |

| Absolute Voltage, V <sub>REFOUT</sub>      | 1.08 | 1.2    | 1.32 | V      | Unloaded                                                                  |

| Minimum Load Resistance                    | 1    |        |      | kΩ     |                                                                           |

| Maximum Load Capacitance                   |      |        | 100  | pF     |                                                                           |

| ADC SPECIFICATIONS                         |      |        |      |        |                                                                           |

| Maximum Input Range at VIN <sup>2, 3</sup> |      | 1.578  |      | V p-p  | Measured Differentially.                                                  |

|                                            |      | -2.85  |      | dBm    | Max. Input = $(1.578/1.2)*V_{REFCAP}$                                     |

| Nominal Reference Level at VIN             |      | 1.0954 |      | V p-р  | Measured Differentially                                                   |

| (0 dBm0)                                   |      | -6.02  |      | dBm    |                                                                           |

| Absolute Gain                              |      |        |      |        | 6                                                                         |

| PGA = 0 dB                                 | -2.2 | -0.6   | +1.0 | dB     | 1.0 kHz, 0 dBm0                                                           |

| PGA = 38 dB                                |      | -1.0   |      | dB     | 1.0 kHz, 0 dBm0                                                           |

| Gain Tracking Error                        |      | ±0.1   |      | dB     | 1.0 kHz, +3 dBm0 to -50 dBm0                                              |

| Signal to (Noise + Distortion)             |      |        |      |        | Refer to Figure 5                                                         |

| PGA = 0 dB                                 | 70   | 76     |      | dB     | 300 Hz to 3400 Hz;                                                        |

|                                            | 70   | 74     |      | dB     | 0 Hz to $f_{SAMP}/2$ ;                                                    |

|                                            |      | 72     |      | dB     | 300 Hz to 3400 Hz; f <sub>SAMP</sub> = 64 kHz                             |

|                                            |      | 56     |      | dB     | 0 Hz to $f_{SAMP}/2$ ; $f_{SAMP} = 64 \text{ kHz}$                        |

| PGA = 38 dB                                |      | 60     |      | dB     | 300 Hz to 3400 Hz;                                                        |

|                                            |      |        |      | 59     | dB 0 Hz to $f_{SAMP}/2$                                                   |

| Total Harmonic Distortion                  |      |        |      |        |                                                                           |

| PGA = 0 dB                                 |      | -85    | -70  | dB     | 300 Hz to 3400 Hz;                                                        |

| PGA = 38 dB                                |      | -85    |      | dB     | 300 Hz to 3400 Hz;                                                        |

| Intermodulation Distortion                 |      | -82    |      | dB     | PGA = 0 dB                                                                |

| Idle Channel Noise                         |      | -76    |      | dBm0   | PGA = 0 dB                                                                |

| Crosstalk                                  |      | -100   |      | dB     | ADC Input Level: 1.0kHz, 0 dBm0                                           |

|                                            |      |        |      |        | DAC Input at Idle                                                         |

| DC Offset                                  | -20  | +2     | +25  | mV     | $PGA = \hat{0} dB$                                                        |

| Power Supply Rejection                     |      | -84    |      | dB     | Input Signal Level at AVDD and DVD                                        |

| 11.5 5                                     |      |        |      |        | Pins: 1.0 kHz, 100 mV p-p Sine Wave                                       |

| Group Delay <sup>4, 5</sup>                |      | 25     |      | μs     | $f_{SAMP} = 64 \text{ kHz}$                                               |

| Input Resistance at PGA <sup>2, 4, 6</sup> |      | 45     |      | kΩ     | DMCLK = 16.384 MHz                                                        |

| DACSPECIFICATIONS                          |      |        |      |        |                                                                           |

| Maximum Voltage Output Swing <sup>2</sup>  |      |        |      |        |                                                                           |

| Single Ended                               |      | 1.578  |      | V p-p  | PGA = 6 dB                                                                |

| 0                                          |      | -2.85  |      | dBm    | Max. Output = $(1.578/1.2)*V_{REFCAP}$                                    |

| Differential                               |      | 3.156  |      | V p-p  | PGA = 6 dB                                                                |

|                                            |      | 3.17   |      | dBm    | Max. Output = $2^*((1.578/1.2)^*V_{\text{REFCARE}})$                      |

| Nominal Voltage Output Swing (0 dBm0)      |      |        |      |        | I CONTRACTOR REPORT                                                       |

| Single-Ended                               |      | 1.0954 |      | V p-p  | PGA = 6 dB                                                                |

| ~                                          |      | -6.02  |      | dBm    |                                                                           |

| Differential                               |      | 2.1909 |      | V p-p  | PGA = 6 dB                                                                |

|                                            |      | 0      |      | dBm    |                                                                           |

| Output Bias Voltage                        | 1.08 | 1.2    | 1.32 | V      | REFOUT Unloaded                                                           |

| Absolute Gain                              | -1.8 | -0.7   | +0.4 |        | 1.0 kHz, 0 dBm0; Unloaded                                                 |

| Gain Tracking Error                        |      | ± 0.1  |      | dB     | 1.0 kHz, $+3$ dBm0 to $-50$ dBm0                                          |

| Signal to (Noise + Distortion) at 0 dBm0   |      |        |      |        |                                                                           |

| PGA = 0 dB                                 | 70   | 77     |      | dB     | 300 Hz to 3400 Hz                                                         |

|                                            |      |        | 76   |        | dB 300 Hz to 3400 Hz; $f_{SAMP} = 64$ kH                                  |

| PGA = 6 dB                                 |      | 77     |      | dB     | 300  Hz to  3400  Hz;                                                     |

|                                            |      | 77     |      | dB     | $300 \text{ Hz to } 3400 \text{ Hz}$ ; $f_{\text{SAMP}} = 64 \text{ kHz}$ |

|                                            |      |        |      | uЪ     | 555 112 to 5400 112, ISAMP - 04 KI IZ                                     |

|                                            |      |        |      |        |                                                                           |

| PARAMETER                                               |        | Min          | Тур  | Max | Units | Test Conditions (STYLE: table col.head)    |

|---------------------------------------------------------|--------|--------------|------|-----|-------|--------------------------------------------|

| Total Harmonic Distortion at 0 dBm0                     |        |              |      |     |       |                                            |

| PGA = 0 dB                                              |        |              | -80  | -70 | dB    |                                            |

| PGA = 6 dB                                              |        |              | -80  |     | dB    |                                            |

| Intermodulation Distortion                              |        |              | -85  |     | dB    | PGA = 0 dB                                 |

| Idle Channel Noise                                      |        |              | -76  |     | dBm0  | PGA = 0 dB                                 |

| Crosstalk                                               |        |              | -100 |     | dB    | ADC Input Level: AGND;                     |

|                                                         |        |              |      |     |       | DAC Output Level: 1.0 kHz, 0 dBm0          |

| Power Supply Rejection                                  |        |              | -81  |     | dB    | Input Signal Level at AVDD and DVDD        |

|                                                         |        |              |      |     |       | Pins: 1.0 kHz, 100 mV p-p Sine Wave        |

| Group Delay <sup>4, 5</sup>                             |        |              | 25   |     | μs    | $f_{SAMP} = 64$ kHz; Interpolator Bypassed |

|                                                         |        |              | 50   |     | μs    | $f_{SAMP} = 64 \text{ kHz}$                |

| Output DC Offset <sup>2, 7</sup>                        |        | -30          | +5   | +50 | mV    | PGA = 6 dB                                 |

| Minimum Load Resistance, R <sub>L</sub> <sup>2, 8</sup> |        |              |      |     |       |                                            |

| Single-Ended <sup>4</sup>                               |        | 150          |      |     | Ω     | 1                                          |

| Differential                                            |        | 150          |      |     | Ω     |                                            |

| Maximum Load Capacitance, ${\rm C_L}^{2, 8}$            |        |              |      |     |       |                                            |

| Single-Ended <sup>4</sup>                               |        |              |      | 500 | pF    |                                            |

| Differential                                            |        |              |      | 100 | pF    |                                            |

| LOGIC INPUTS                                            |        |              |      |     |       |                                            |

| V <sub>INH</sub> , Input High Voltage                   | DVDD - | - 0.8        | D١   | /DD | V     |                                            |

| V <sub>INL</sub> , Input Low Voltage                    | 0      |              | 0.8  | 3   | V     |                                            |

| I <sub>IH</sub> , Input Current                         | -10    |              | +1   | 0   | μA    |                                            |

| C <sub>IN</sub> , Input Capacitance                     |        |              | 10   |     | pF    |                                            |

| LOGIC OUTPUT                                            |        |              |      |     |       |                                            |

| V <sub>OH</sub> , Output High Voltage                   | DVDD - | - 0.4        | D    | /DD | V     | IOUT  - 100 μA                             |

| V <sub>OL</sub> , Output Low Voltage                    | 0      | $\mathbf{C}$ | 0.4  | 1   | V     | IOUT  - 100 μA                             |

| Three-State Leakage Current                             | -10    |              | +1   | 0   | μA    |                                            |

| POWER SUPPLIES                                          |        |              |      |     |       |                                            |

| AVDD1, AVDD2                                            | 3.0    |              | 3.6  |     | V     |                                            |

| DVDD                                                    | 3.0    |              | 3.6  | 3   | V     |                                            |

| I <sub>DD</sub> <sup>10</sup>                           |        |              |      |     |       | See Table I                                |

AD73511

NOTES <sup>1</sup> Operating temperature range is as follows: -20°C to +85°C. Therefore, T<sub>MIN</sub> = -20°C and T<sub>MAX</sub> = +85°C. <sup>2</sup> Test conditions: Input PGA set for 0 dB gain, Output PGA set for 6 dB gain, no load on analog outputs (unless otherwise noted). <sup>3</sup> At input to sigma-delta modulator of ADC. <sup>4</sup> Guaranteed by design. <sup>5</sup> Overall group delay will be affected by the sample rate and the external digital filtering. <sup>6</sup> The AC is input improvement input here are input to the DMCL K and improvement to the (2.2.4.10) DMCL K

<sup>6</sup> The ADC's input impedance is inversely proportional to DMCLK and is approximated by: (3.3 \* 10<sup>11</sup>)/DMCLK.

<sup>7</sup> Between VOUTP1 and VOUTN1 or between VOUTP2 and VOUTN2.

<sup>8</sup> At VOUT output.

<sup>9</sup> Frequency responses of ADC and DAC measured with input at audio reference level (the input level that produces an output level of -10 dBm0), with 38 dB preamplifier bypassed and input gain of 0 dB.

<sup>10</sup> Test Conditions: no load on digital inputs, analog inputs ac coupled to ground, no load on analog outputs.

Specifications subject to change without notice.

| PARAMETH                        | ER                                                 | <b>Test Conditions</b>                                             | Min                 | Тур | Max | Uni |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------------------|---------------------|-----|-----|-----|

| <b>DSP SECTI</b>                | ION                                                |                                                                    |                     |     |     |     |

| / <sub>IН</sub>                 | Hi-Level Input Voltage <sup>1, 2</sup>             | $@V_{DD} = max$                                                    | 2.0                 |     |     | V   |

| / <sub>IH</sub>                 | Hi-Level CLKIN Voltage                             | $@V_{DD} = max$                                                    | 2.2                 |     |     | V   |

| / <sub>IL</sub>                 | Lo-Level Input Voltage <sup>1, 3</sup>             | @ V <sub>DD</sub> = min                                            |                     |     | 0.8 | V   |

| он                              | Hi-Level Output Voltage <sup>1, 4, 5</sup>         | @ V <sub>DD</sub> = min                                            |                     |     |     |     |

|                                 |                                                    | I <sub>он</sub> = - <b>0.5 mA</b>                                  | 2.4                 |     |     | V   |

|                                 |                                                    | $@ V_{DD} = min$                                                   |                     |     |     |     |

|                                 |                                                    | $I_{OH} = -100 \ \mu A^6$                                          | V <sub>DD</sub> - 0 | ).3 |     | V   |

| OL                              | Lo-Level Output Voltage <sup>1, 4, 5</sup>         | $@ V_{DD} = min$                                                   |                     |     |     |     |

|                                 |                                                    | $I_{OL} = 2 \text{ mA}$                                            |                     |     | 0.4 | V   |

| н                               | Hi-Level Input Current <sup>3</sup>                | $@ V_{DD} = max$                                                   |                     |     |     |     |

|                                 |                                                    | $\mathbf{V}_{\mathbf{IN}} = \mathbf{V}_{\mathbf{DD}} \mathbf{max}$ |                     |     | 10  | μA  |

| L                               | Lo-Level Input Current <sup>3</sup>                | $@ V_{DD} = max$                                                   |                     |     |     |     |

|                                 |                                                    | $\mathbf{V}_{\mathbf{IN}} = 0 \mathbf{V}$                          |                     |     | 10  | μA  |

| ZH                              | Three-State Leakage Current <sup>7</sup>           | $@ V_{DD} = max$                                                   |                     |     |     |     |

|                                 |                                                    | $V_{IN} = V_{DD} max^8$                                            |                     |     | 10  | μA  |

| ZL                              | Three-State Leakage Current <sup>7</sup>           | @ V <sub>DD</sub> = max                                            |                     |     |     |     |

|                                 |                                                    | $\mathbf{V_{IN}}=0\ \mathbf{V^8}$                                  |                     |     | 10  | μA  |

| D                               | Supply Current (Idle) <sup>9</sup>                 | $@V_{DD} = 3.3$                                                    |                     |     |     |     |

|                                 |                                                    | $t_{CK} = 19 \text{ ns}^{10}$                                      |                     | 10  |     | mA  |

|                                 | $\mathbf{t}_{\mathrm{CK}} = 25 \ \mathbf{ns}^{10}$ |                                                                    | 8                   |     | mA  |     |

| $_{\rm K} = 30 \ {\rm ns}^{10}$ |                                                    | 7                                                                  |                     | mA  |     |     |

| D                               | Supply Current (Dynamic) <sup>11</sup>             | @ $V_{DD} = 3.3$                                                   |                     |     |     |     |

|                                 |                                                    | $T_{AMB} = +25^{\circ}C$                                           |                     |     |     |     |

|                                 |                                                    | $t_{CK} = 19 \text{ ns}^{10}$                                      |                     | 51  |     | mA  |

|                                 | $t_{CK} = 25 \text{ ns}^{10}$                      |                                                                    | 41                  |     | mA  |     |

| $_{\rm K} = 30 \ {\rm ns}^{10}$ |                                                    | 34                                                                 |                     | mA  |     |     |

| [                               | Input Pin Capacitance <sup>3, 6, 12</sup>          | @ V <sub>IN</sub> = 2.5 V                                          |                     |     |     |     |

|                                 |                                                    | $f_{IN} = 1.0 \text{ MHz}$                                         |                     |     |     |     |

|                                 |                                                    | $T_{AMB} = +25^{\circ}C$                                           |                     |     | 8   | pF  |

| 0                               | Output Pin Capacitance <sup>6, 7, 12, 13</sup>     | @ $V_{IN} = 2.5 V$                                                 |                     |     |     | -   |

|                                 |                                                    | $f_{IN} = 1.0 MHz$                                                 |                     |     |     |     |

|                                 |                                                    | $T_{AMB} = +25^{\circ}C$                                           |                     |     | 8   | pF  |

NOTES

<sup>1</sup>Bidirectional pins: D0-D23, RFS0, RFS1, SCLK0, SCLK1, TFS0, TFS1, A1-A13, PF0-PF7.

<sup>2</sup>Input only pins: RESET, BR, DR0, DR1, PWD.

<sup>3</sup>Input only pins: CLKIN, RESET, BR, DR0, DR1, PWD.

<sup>4</sup>Output pins: BG, PMS, DMS, BMS, IOMS, CMS, RD, WR, PWDACK, A0, DT0, DT1, CLKOUT, FL2-0, BGH.

<sup>5</sup>Although specified for TTL outputs, all AD73511 outputs are CMOS-compatible and will drive to V<sub>DD</sub> and GND, assuming no dc loads.

<sup>6</sup>Guaranteed but not tested.

<sup>7</sup>Three-statable pins: A0-A13, D0-D23, PMS, DMS, BMS, IOMS, CMS, RD, WR, DT0, DT1, SCLK0, SCLK1, TFS0, TFS1, RFS0, RFS1, PF0-PF7. <sup>8</sup>0 V on BR.

<sup>9</sup>Idle refers to AD73511 state of operation during execution of IDLE instruction. Deasserted pins are driven to either V<sub>DD</sub> or GND.

$^{10}V_{\rm IN}$  = 0 V and 3 V. For typical figures for supply currents, refer to Power Dissipation section.

<sup>11</sup>I<sub>DD</sub> measurement taken with all instructions executing from internal memory. 50% of the instructions are multifunction (types 1, 4, 5, 12, 13, 14), 30% are type 2 and type 6, and 20% are idle instructions.

<sup>12</sup>Applies to PBGA package type.

<sup>13</sup>Output pin capacitance is the capacitive load for any three-stated output pin.

Specifications subject to change without notice.

## POWER CONSUMPTION

| CONDITIONS           | Тур. | Max.  | SE | MCLK On | Test Conditions                                |

|----------------------|------|-------|----|---------|------------------------------------------------|

| AFE SECTION          |      |       |    |         |                                                |

| ADC On Only          | 7    | 7.2   | 1  | YES     | REFOUT Disabled                                |

| ADC and DAC On       | 11   | 12    | 1  | YES     | REFOUT Disabled                                |

| REFCAP On Only       | 0.65 | 1.00  | 0  | NO      | REFOUT Disabled                                |

| REFCAP and           | 2.7  | 3.8   | 0  | NO      |                                                |

| REFOUT On Only       |      |       |    |         |                                                |

| All AFE Sections Off | 0.6  | 0.65  | 0  | YES     | MCLK Active Levels Equal to 0V and DVDD        |

| All AFE Sections Off | 2 μΑ | 10 µA | 0  | NO      | Digital Inputs Static and Equal to 0 V or DVDD |

| DSP SECTION          |      |       |    |         |                                                |

| Idle Mode            | 6.4  |       | -  | -       |                                                |

| Dynamic              | 43   |       | -  | -       |                                                |

## TIMING CHARACTERISTICS - AFE SECTION

| 43                                           |                                                                                                                                                   |                                                                                                                  |                                                                                                                                                                                                                                                         |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and are typical values unless otherwise note | d.                                                                                                                                                |                                                                                                                  | NR'                                                                                                                                                                                                                                                     |

| CTERISTICS - AFE SEC                         | rion                                                                                                                                              |                                                                                                                  |                                                                                                                                                                                                                                                         |

| Li                                           | mit                                                                                                                                               | Units                                                                                                            | Description                                                                                                                                                                                                                                             |

|                                              |                                                                                                                                                   |                                                                                                                  | See Figure 1                                                                                                                                                                                                                                            |

| 61                                           |                                                                                                                                                   | ns min                                                                                                           | 16.384 MHz MCLK Period                                                                                                                                                                                                                                  |

| 24                                           | .4                                                                                                                                                | ns min                                                                                                           | MCLK Width High                                                                                                                                                                                                                                         |

| 24                                           | .4                                                                                                                                                | ns min                                                                                                           | MCLK Width Low                                                                                                                                                                                                                                          |

|                                              | ] ]                                                                                                                                               |                                                                                                                  | See Figures 3 and 4                                                                                                                                                                                                                                     |

| t <sub>1</sub>                               |                                                                                                                                                   | ns min                                                                                                           | SCLK Period (SCLK = MCLK)                                                                                                                                                                                                                               |

| 0.4                                          | * t <sub>1</sub>                                                                                                                                  | ns min                                                                                                           | SCLK Width High                                                                                                                                                                                                                                         |

| 0.4                                          | * t <sub>1</sub>                                                                                                                                  | ns min                                                                                                           | SCLK Width Low                                                                                                                                                                                                                                          |

| 20                                           |                                                                                                                                                   | ns min                                                                                                           | SDI/SDIFS Setup Before SCLK Low                                                                                                                                                                                                                         |

| 0                                            |                                                                                                                                                   | ns min                                                                                                           | SDI/SDIFS Hold After SCLK Low                                                                                                                                                                                                                           |

| 10                                           |                                                                                                                                                   |                                                                                                                  | SDOFS Delay From SCLK High                                                                                                                                                                                                                              |

| 10                                           |                                                                                                                                                   |                                                                                                                  | SDOFS Hold After SCLK High                                                                                                                                                                                                                              |

| 10                                           |                                                                                                                                                   |                                                                                                                  | SDO Hold After SCLK High                                                                                                                                                                                                                                |

| 10                                           |                                                                                                                                                   |                                                                                                                  | SDO Delay From SCLK High                                                                                                                                                                                                                                |

| 30                                           |                                                                                                                                                   | ns max                                                                                                           | SCLK Delay from MCLK                                                                                                                                                                                                                                    |

|                                              | and are typical values unless otherwise note<br>CTERISTICS - AFE SECT<br>Lin<br>61<br>24<br>24<br>1<br>1<br>0.4<br>0<br>0<br>10<br>10<br>10<br>10 | $\begin{array}{c} \text{Limit} \\ 61 \\ 24.4 \\ 24.4 \\ 24.4 \\ t_1 \\ 0.4 * t_1 \\ 0.4 * t_1 \\ 20 \end{array}$ | and are typical values unless otherwise noted.<br>CTERISTICS - AFE SECTION<br>Limit Units<br>61 ns min<br>24.4 ns min<br>24.4 ns min<br>24.4 ns min<br>0.4 * t <sub>1</sub> ns min<br>0.4 * t <sub>1</sub> ns min<br>0 ns min<br>10 ns max<br>10 ns max |

## AD73511

## **Preliminary Technical Data**

| Model        | Temperature    | Package                          | Package |

|--------------|----------------|----------------------------------|---------|

|              | Range          | Description                      | Option  |

| AD73511BB-80 | -20 C to +85 C | 119-Ball Plastic Ball Grid Array | B-119   |

| AD73511BB-40 | -20 C to +85 C | 119-Ball Plastic Ball Grid Array | B-119   |

#### **ORDERING GUIDE**

# MNARY

#### CAUTION -

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD73511 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

|   | 1         | 2         | 3         | 4         | 5         | 6          | 7          |

|---|-----------|-----------|-----------|-----------|-----------|------------|------------|

| Α | IRQE/PF4  | DMS       | VDD (INT) | CLKIN     | A11/IAD10 | A7/IAD6    | A4/IAD3    |

| в | IRQL0/PF5 | PMS       | WR        | XTAL      | A12/IAD11 | A8/IAD7    | A5/IAD4    |

| С | IRQL1/PF6 | IOMS      | RD        | VDD (EXT) | A13/IAD12 | A9/IAD8    | GND        |

| D | IRQ2/PF7  | CMS       | BMS       | CLKOUT    | GND       | A10/IAD9   | A6/IAD5    |

| E | DT0       | TFS0      | RFS0      | A3/IAD2   | A2/IAD1   | A1/IAD0    | A0         |

| F | DR0       | SCLK0     | DT1/F0    | PWDACK    | BGH       | MODE A/PF0 | MODE B/PF1 |

| G | TFS1/IRQ1 | RFS1/IRQ0 | DR1/FI    | GND       | PWD       | VDD (EXT)  | MODE C/PF2 |

| н | SCLK1     | ERESET    | RESET     | PF3       | FL0       | FL1        | FL2        |

| J | EMS       | EE        | ECLK      | D23       | D22       | D21        | D20        |

| к | ELOUT     | ELIN      | EINT      | D19       | D18       | D17        | D16        |

| L | BG        | D3/IACK   | D5/IAL    | D8        | D9        | D12        | D15        |

| м | EBG       | D2/IAD15  | D4/IS     | D7/IWR    | VDD (EXT) | D11        | D14        |

| Ν | BR        | D1/IAD14  | VDD (INT) | D6/IRD    | GND       | D10        | D13        |

| Р | EBR       | D0/IAD13  | DVDD      | DGND      | ARESET    | SCLK2      | AMCLK      |

| R | SDO       | SDOFS     | SDIFS     | SDI       | SE        | REFCAP     | REFOUT     |

| т | VINP      | NC        | VINN      | NC        | NC        | NC         | NC         |

| U | AGND      | AVDD      | NC        | NC        | VOUTP     | VOUTN      | NC         |

#### **PBGA BALL CONFIGURATION**

NOTES:

VDD (INT) > DSP CORE SUPPLY VDD (EXT) > DSP I/O DRIVER SUPPLY BOTH VDD (INT) AND VDD (EXT) SHOULD BE POWERED FROM THE SAME SUPPLY.

TOP VIEW

AD73511

#### PIN FUNCTION DESCRIPTION **Mnemonic** Function VINP Analog Input to the positive terminal of the input Channel. VINN Analog Input to the negative terminal of the input Channel. REFOUT Buffered Reference Output, which has a nominal value of 1.2 V. REFCAP A Bypass Capacitor to AGND2 of 0.1 µF is required for the on-chip reference. The capacitor should be fixed to this pin. AVDD2 Analog Power Supply Connection for Codec 2. AGND2 Analog Ground/Substrate Connection for Codec 2. DGND Digital Ground/Substrate Connection. DVDD Digital Power Supply Connection. ARESET Active Low Reset Signal. This input resets the entire chip, resetting the control registers and clearing the digital circuitry. SCLK Output Serial Clock whose rate determines the serial transfer rate to/from the codec. It is used to clock data or control information to and from the serial port (SPORT). The frequency of SCLK is equal to the frequency of the master clock (MCLK) divided by an integer number—this integer number being the product of the external master clock rate divider and the serial clock rate divider. MCLK Master Clock Input. MCLK is driven from an external clock signal. **SDO** Serial Data Output of the Codec. Both data and control information may be output on this pin and is clocked on the positive edge of SCLK. SDO is in three-state when no information is being transmitted and when SE is low. **SDOFS** Framing Signal Output for SDO Serial Transfers. The frame sync is one-bit wide and it is active one SCLK period before the first bit (MSB) of each output word. SDOFS is referenced to the positive edge of SCLK. SDOFS is in three-state when SE is low. Framing Signal Input for SDI Serial Transfers. The frame sync is one-bit wide and it is valid one SCLK period SDIFS before the first bit (MSB) of each input word. SDIFS is sampled on the negative edge of SCLK and is ignored when SE is low. Serial Data Input of the Codec. Both data and control information may be input on this pin and are clocked on the negative edge of SCLK. SDI is ignored when SE is low. SPORT Enable. Asynchronous input enable pin for the SPORT. When SE is set low by the DSP, the output pins of the SPORT are three-stated and the input pins are ignored. SCLK is also disabled internally in order to decrease power dissipation. When SE is brought high, the control and data registers of the SPORT are at their original values (before SE was brought low), however the timing counters and other internal registers are at their reset values. AGND1 Analog Ground/Substrate Connection for Codec 1. AVDD1 Analog Power Supply Connection for Codec 1. RESET (Input) Processor Reset Input (Input) Bus Request Input (Output) Bus Grant Output BGH (Output) Bus Grant Hung Output (Output) Data Memory Select Output DMS PMS (Output) Program Memory Select Output IOMS (Output) Memory Select Output BMS (Output) Byte Memory Select Output **CMS** (Output) Combined Memory Select Output (Output) Memory Read Enable Output (Output) Memory Write Enable Output IRO2/ (Input) Edge- or Level-Sensitive Interrupt (Input/Output) Request.<sup>1</sup> Programmable I/O Pin (Input) Level-Sensitive Interrupt Requests<sup>1</sup> **IROL**0/ (Input/Output) Programmable I/O Pin IRQL1/ (Input) Level-Sensitive Interrupt Requests<sup>1</sup> (Input/Output) Programmable I/O Pin **IROE**/ (Input) Edge-Sensitive Interrupt Requests<sup>1</sup> (Input/Output) Programmable I/O Pin Mode D/ (Input) Mode Select Input—Checked Only During RESET

(Input/Output) Programmable I/O Pin During Normal Operation PF3

Mode C/ (Input) Mode Select Input-Checked Only During RESET

(Input/Output) Programmable I/O Pin During Normal Operation PF2 (Input) Mode Select Input-Checked Only During RESET Mode B/

PF1 (Input/Output) Programmable I/O Pin During Normal Operation

SDI

SE

BR

BG

RD

WR

PF7

PF6

PF5

PF4

## AD73511

| Mode A/<br>PF0<br>CLKIN                                                                                        | (Input) Mode Select Input—Checked Only During RESET<br>(Input/Output) Programmable I/O Pin During Normal Operation                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKIN,<br>XTAL<br>CLKOUT<br>SPORT0<br><u>SPORT1</u><br>IRQ1:0<br>FI<br>FO<br><u>PWD</u><br>PWDACK<br>FL0, FL1, | (Inputs) Clock or Quartz Crystal Input<br>(Output) Processor Clock Output<br>(Inputs/Outputs) Serial Port I/O Pins<br>(Inputs/Outputs) Serial Port I/O Pins<br>(Inputs) Edge- or Level-Sensitive Interrupts,<br>(Input) Flag In <sup>2</sup><br>(Output) Flag Out <sup>2</sup><br>(Input) Power-Down Control Input<br>(Output) Power-Down Control Output |

| FL2<br>VDD and                                                                                                 | (Outputs) Output Flags                                                                                                                                                                                                                                                                                                                                   |

| GND<br>EZ-Port                                                                                                 | Power and Ground<br>(Inputs/Outputs) For Emulation Use                                                                                                                                                                                                                                                                                                   |

|                                                                                                                | PRECHNAK                                                                                                                                                                                                                                                                                                                                                 |

#### AD73511

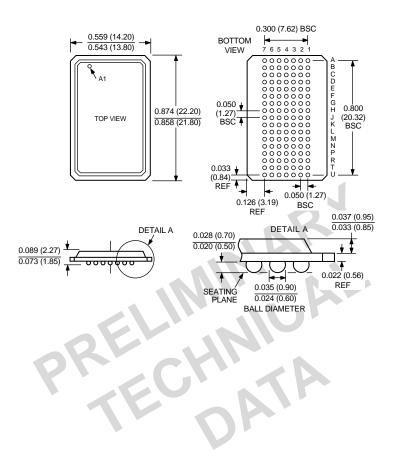

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

00000000