# DI CMOS Protected Analog Switches

# AD7510DI/AD7511DI/AD7512D

#### FEATURES

$\label{eq:last} \begin{array}{l} \mbox{Latch-Proof} \\ \mbox{Overvoltage-Proof: $\pm$25V$ \\ \mbox{Low $R_{ON}$: 75$$\Omega$ \\ \mbox{Low Dissipation: $3mW$ \\ \mbox{TTL/CMOS Direct Interface} \\ \mbox{Silicon-Nitride Passivated} \\ \mbox{Monolithic Dielectrically-Isolated CMOS} \\ \mbox{Standard 14-/16-Pin DIPs and} \\ \mbox{20-Terminal Surface Mount Packages} \end{array}$

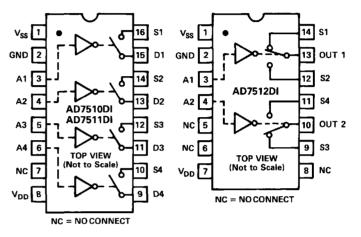

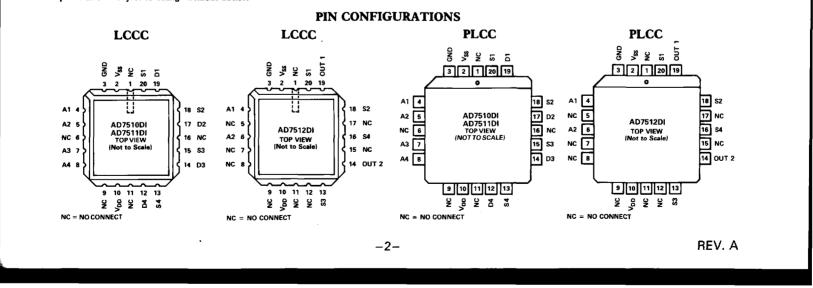

#### **DIP FUNCTIONAL DIAGRAMS**

#### **GENERAL DESCRIPTION**

The AD7510DI, AD7511DI and AD7512DI are a family of latch proof dielectrically isolated CMOS switches featuring overvoltage protection up to  $\pm 25V$  above the power supplies. These benefits are obtained without sacrificing the low "ON" resistance (75 $\Omega$ ) or low leakage current (500pA), the main features of an analog switch.

The AD7510DI and AD7511DI consist of four independent SPST analog switches packaged in either a 16-pin DIP or a 20terminal surface mount package. They differ only in that the digital control logic is inverted. The AD7512DI has two independent SPDT switches packaged either in a 14-pin DIP or a 20-terminal surface mount package.

Very low power dissipation, overvoltage protection and TTL/ CMOS direct interfacing are achieved by combining a unique circuit design and a dielectrically isolated CMOS process. Silicon nitride passivation ensures long term stability while monolithic construction provides reliability.

#### **CONTROL LOGIC**

- AD7510DI: Switch "ON" for Address "HIGH"

- AD7511DI: Switch "ON" for Address "LOW"

- AD7512DI: Address "HIGH" makes S1 to Out 1 and S3 to Out 2

#### **ORDERING GUIDE**

| Model <sup>1</sup>                                                               | Temperature<br>Range                                                                     | Package<br>Option <sup>2</sup>         |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------|

| AD7510DIKN                                                                       | 0 to + 70°C                                                                              | N-16                                   |

| AD7510DIKP                                                                       | 0 to + 70°C                                                                              | P-20A                                  |

| AD7510DIKQ                                                                       | - 25°C to + 85°C                                                                         | Q-16                                   |

| AD7510DISQ                                                                       | - 55°C to + 125°C                                                                        | Q-16                                   |

| AD7510DISE                                                                       | - 55°C to + 125°C                                                                        | E-20A                                  |

| AD7511DIKN                                                                       | 0 to + 70°C                                                                              | N-16                                   |

| AD7511DIKP                                                                       | 0 to + 70°C                                                                              | P-20A                                  |

| AD7511DIKQ                                                                       | - 25°C to + 85°C                                                                         | Q-16                                   |

| AD7511DISQ                                                                       | - 55°C to + 125°C                                                                        | Q-16                                   |

| AD7511DITE                                                                       | - 55°C to + 125°C                                                                        | E-20A                                  |

| AD7512DIKN<br>AD7512DIKP<br>AD7512DIKQ<br>AD7512DIKQ<br>AD7512DITQ<br>AD7512DITE | 0 to + 70°C<br>0 to + 70°C<br>- 25°C to + 85°C<br>- 55°C to + 125°C<br>- 55°C to + 125°C | N-14<br>P-20A<br>Q-14<br>Q-14<br>E-20A |

NOTES

<sup>1</sup>To order MIL-STD-883, Class B, processed parts, add/883B to part number. See Analog Devices Military Products Databook (1990) for military data sheet.

$^{2}E = Leadless Ceramic Chip Carrier (LCCC); N = Plastic DIP;$

$\mathbf{P} = \mathbf{Plastic Leaded Chip Carrier (PLCC); Q} = \mathbf{Cerdip.}$

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

617/329-4700

Fax:

617/326-8703

Twx:

710/394-6577

Telex:

924491

Cable:

ANALOG NORWOODMASS

## AD7510DI/AD7511DI/AD7512DI — SPECIFICATIONS

| INDUSTRIAL VERSION (K)                                      |            |         |                        |                                         |                                                                                                                                        |

|-------------------------------------------------------------|------------|---------|------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                   | MODEL      | VERSION | +25°C<br>(N, P, Q)     | 0 to +70°C (N, P)<br>-25°C to +85°C (Q) | TEST CONDITIONS                                                                                                                        |

| ANALOG SWITCH                                               |            |         |                        | <b></b>                                 |                                                                                                                                        |

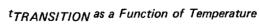

| R <sub>ON</sub> <sup>1</sup>                                | All        | к       | 75Ω typ, 100Ω max      | 175 $\Omega$ max                        | $-10V \le V_D \le +10V$                                                                                                                |

| $R_{ON} vs V_D (V_S)$                                       | All        | к       | 20% typ                |                                         | $l_{\rm DS} = 1.0 {\rm mA}$                                                                                                            |

| R <sub>ON</sub> Drift                                       | All        | к       | +0.5%/°C typ           |                                         |                                                                                                                                        |

| R <sub>ON</sub> Match                                       | All        | к       | 1% typ                 |                                         | $V_{D} = 0, I_{DS} = 1.0 mA$                                                                                                           |

| R <sub>ON</sub> Drift<br>Match                              | All        | к       | 0.01%/°C typ           |                                         | D , DS                                                                                                                                 |

| I <sub>D</sub> (I <sub>S</sub> ) <sub>OFF<sup>1</sup></sub> | All        | К       | 0.5nA typ, 5nA max     | 500nA max                               | $V_D = -10V$ , $V_S = +10V$ and<br>$V_D = +10V$ , $V_S = -10V$                                                                         |

|                                                             | All        | к       | 10nA max               |                                         | $\frac{V_{S} = V_{D} = +10V}{V_{S} = V_{D} = +10V}$                                                                                    |

| 1D (15)ON                                                   | All        | ĸ       | TonA max               |                                         | $V_{\rm S} = V_{\rm D} = -10V$                                                                                                         |

| <sup>I</sup> our <sup>1</sup>                               | AD7512DI   | К       | 15nA max               | 1500nA max                              | $V_{S1} = V_{OUT} = \pm 10V, V_{S2} = \mp 10V$<br>and $V_{S2} = V_{OUT} = \pm 10V, V_{S1} = \mp 10V$                                   |

| DIGITAL CONTROL                                             |            |         |                        |                                         |                                                                                                                                        |

| V <sub>INL</sub> <sup>1</sup>                               | All        | К       |                        | 0.8V max                                |                                                                                                                                        |

| V <sub>INH</sub> 1                                          | All        |         |                        | 2.4V min                                |                                                                                                                                        |

| C <sub>IN</sub>                                             | All        | к       | 7pF typ                |                                         |                                                                                                                                        |

| I <sub>INH</sub> <sup>1</sup>                               | All        | к       | 10nA max               |                                         | $V_{IN} = V_{DD}$                                                                                                                      |

| Int. I                                                      | All        | к       | 10nA max               |                                         | $V_{IN} = 0$                                                                                                                           |

| DYNAMIC<br>CHARACTERISTICS                                  |            |         |                        |                                         |                                                                                                                                        |

| <sup>t</sup> on                                             | AD7510DI   | К       | 180ns typ              |                                         |                                                                                                                                        |

|                                                             | AD7511DI   | к       | 350ns typ              |                                         | $V_{IN} = 0$ to +3.0V                                                                                                                  |

| <sup>t</sup> off                                            | AD7510DI   | ĸ       | 350ns typ              |                                         |                                                                                                                                        |

| t                                                           | AD7511DI   | K       | 180ns typ              |                                         |                                                                                                                                        |

| <sup>t</sup> TRANSITION                                     | AD7512DI   | K       | 300ns typ              |                                         |                                                                                                                                        |

| C <sub>S</sub> (C <sub>D</sub> )OFF                         | All        | к       | 8pF typ                |                                         |                                                                                                                                        |

| C <sub>S</sub> (C <sub>D</sub> )ON                          | All        | K       | 17pF typ               |                                         | $V_{D}(V_{S}) = 0V$                                                                                                                    |

| $C_{DS} (C_{S-OUT})$<br>$C_{DD} (C_{SS})$                   | All<br>All | K<br>K  | 1pF typ<br>0.5pF typ   |                                         | $\mathbf{D}(\mathbf{r}\mathbf{s}) = \mathbf{v}\mathbf{r}$                                                                              |

| $C_{OUT}$                                                   | AD7512DI   | ĸ       | 17pF typ               |                                         |                                                                                                                                        |

| ~OUT                                                        |            |         |                        |                                         |                                                                                                                                        |

| Q <sub>INJ</sub>                                            | All        | к       | 30pC typ               |                                         | Measured at S or D terminal.<br>$C_L = 1000 \text{pF}, V_{IN} = 0 \text{ to } 3\text{V},$<br>$V_D (V_S) = +10\text{V to } -10\text{V}$ |

| POWER SUPPLY                                                |            | .,      |                        | 202.1                                   |                                                                                                                                        |

|                                                             | All<br>All | K<br>K  | 800μA max<br>800μA max | 800μΑ max<br>800μΑ max                  | All digital inputs = V <sub>INH</sub>                                                                                                  |

|                                                             | All        | к       | 500µA max              | <br>500μA max                           | All digital inputs = V <sub>INL</sub>                                                                                                  |

| L <sub>SS</sub> <sup>1</sup>                                | All        | ĸ       | 500µA max              | 500µA max                               | INL                                                                                                                                    |

NOTES 100% tested.

Specifications subject to change without notice.

## AD7510DI/AD7511DI/AD7512DI

| <b>EXTENDED VERSIONS (S, T)</b>                              |                      |              |                        |                        |                                                                                                             |

|--------------------------------------------------------------|----------------------|--------------|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                    | MODEL                | VERSION      | +25°C                  | -55°C to +125°C        | TEST CONDITIONS                                                                                             |

| ANALOG SWITCH                                                | All                  | S, T         | 100Ω max               | 175Ω max               | $-10V \leq V_D \leq +10V$<br>$I_{DS} = 1mA$                                                                 |

| I <sub>D</sub> (I <sub>S</sub> ) <sub>OFF</sub> <sup>1</sup> | All                  | <b>S</b> , T | 3nA max                | 200nA max              | $V_D = -10V, V_S = +10V$ and<br>$V_D = +10V, V_S = -10V$                                                    |

| I <sub>D</sub> (I <sub>S</sub> )ON <sup>1</sup>              | All                  | S, T         | 10                     |                        | $V_S = V_D = +10V$ and<br>$V_S = V_D = -10V$                                                                |

| I <sub>OUT</sub> <sup>1</sup>                                | AD7512DI             | I S, T       | 9nA max                | 600nA max              | $V_{S1} = V_{OUT} = \pm 10V$ $V_{S2} = \pm 10V \text{ and}$ $V_{S2} = V_{OUT} = \pm 10V$ $V_{S1} = \pm 10V$ |

| DIGITAL CONTROL                                              | All                  | S, T         |                        | 0.8V max               |                                                                                                             |

| $\frac{V_{INL}^{1}}{V_{INH}^{1,2}}$                          | AD7510DI             |              |                        | 2.4V min               |                                                                                                             |

|                                                              | AD7511DI             | Т            |                        | 2.4V min               |                                                                                                             |

|                                                              | AD7512DI             | -            |                        | 2.4V min               |                                                                                                             |

|                                                              | AD7511DI<br>AD7512DI |              |                        | 3.0V min<br>3.0V min   |                                                                                                             |

|                                                              | All<br>All           | S, T<br>S, T | 10nA max<br>10nA max   |                        | $V_{IN} = V_{DD}$ $V_{IN} = 0$                                                                              |

| DYNAMIC<br>CHARACTERISTICS                                   |                      |              |                        | <u></u>                |                                                                                                             |

| ton <sup>3</sup>                                             | AD7510DI<br>AD7511DI | ,            | 1.0µs max<br>1.0µs max |                        | $V_{IN} = 0$ to $+3V$                                                                                       |

| -                                                            | AD7510DI             | ,            | 1.0µs max              |                        |                                                                                                             |

|                                                              | AD7511DI             |              | 1.0µs max              |                        |                                                                                                             |

| tTRANSITION <sup>3</sup>                                     | AD7512DI             | S, T         | 1.0µs max              |                        |                                                                                                             |

| OWER SUPPLY                                                  | A 11                 | 0.7          |                        | 800                    | All digital increases 17                                                                                    |

|                                                              | All<br>All           | s, т<br>s, т |                        | 800μA max<br>800μA max | All digital inputs = $V_{INH}$                                                                              |

|                                                              | All<br>All           | S, T<br>S, T |                        | 500μA max<br>500μA max | All digital inputs = V <sub>INL</sub>                                                                       |

NOTES 100% tested. <sup>3</sup> A pullup resistor, typically 1-2kΩ is required to make AD7511DISQ and AD7512DISQ TTL compatible. <sup>3</sup> Guaranteed, not production tested.

Specifications subject to change without notice.

| ABSOLUTE MAXIMUM RATINGS*                                                                  |                                                                                                                                                  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$ to GND                                                                            | Lead Temperature (Soldering, 10sec) + 300°C                                                                                                      |

| $V_{SS}$ to GND                                                                            | Storage Temperature $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots -65^{\circ}$ C to $+150^{\circ}$ C                           |

| Overvoltage at $V_D(V_S)$                                                                  | Operating Temperature                                                                                                                            |

| (1 second surge) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots V_{DD} + 25V$    | Commercial (KN, KP Versions) $\dots \dots \dots$ |

| or V <sub>SS</sub> – 25V                                                                   | Industrial (KQ Versions) $\ldots \ldots \ldots \ldots \ldots -25^{\circ}$ C to $+85^{\circ}$ C                                                   |

| (Continuous) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots V_{DD} + 20V$ | Extended (SQ, TQ, SE, TE Versions)55°C to +125°C                                                                                                 |

| or $V_{SS} - 20V$                                                                          |                                                                                                                                                  |

| or 20mA, Whichever Occurs First                                                            | *Stresses above those listed under "Absolute Maximum Ratings" may                                                                                |

| Switch Current (I <sub>DS</sub> , Continuous)                                              | cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above |

| Switch Current (I <sub>DS</sub> , Surge)                                                   | those indicated in the operational sections of this specification is not                                                                         |

| Ims Duration, 10% Duty Cycle 150mA                                                         | implied. Exposure to absolute maximum rating conditions for extended                                                                             |

| Digital Input Voltage Range                                                                | periods may affect device reliability.                                                                                                           |

| Power Dissipation (Any Package)                                                            |                                                                                                                                                  |

| Up to $+75^{\circ}C$                                                                       |                                                                                                                                                  |

| Derates above +75°C by 6mW/°C                                                              |                                                                                                                                                  |

|                                                                                            |                                                                                                                                                  |

CAUTION .

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

REV. A

-3-

## AD7510DI/AD7511DI/AD7512DI — Circuit Description -O V<sub>DD</sub> +15V (in-) LEVEL SHIFTER/ DRIVER $\sim$ R1 (in+) 08 R2 O D ΟV<sub>SS</sub>−15\

NOTE: CIRCLED DEVICES IN SEPARATE ISOLATED POCKETS.

#### **CIRCUIT DESCRIPTION**

CMOS devices make excellent analog switches; however, problems with overvoltage and latch-up phenomenon necessitated protection circuitry. These protection circuits, however, either caused degradation of important switch parameters such as R<sub>ON</sub> or leakage, or provided only limited protection in the event of overvoltage.

The AD7510DI series switches utilize a dielectrically isolated CMOS fabrication process to eliminate the four-layer substrate found in junction-isolated CMOS, thus providing latch-free operation.

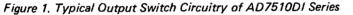

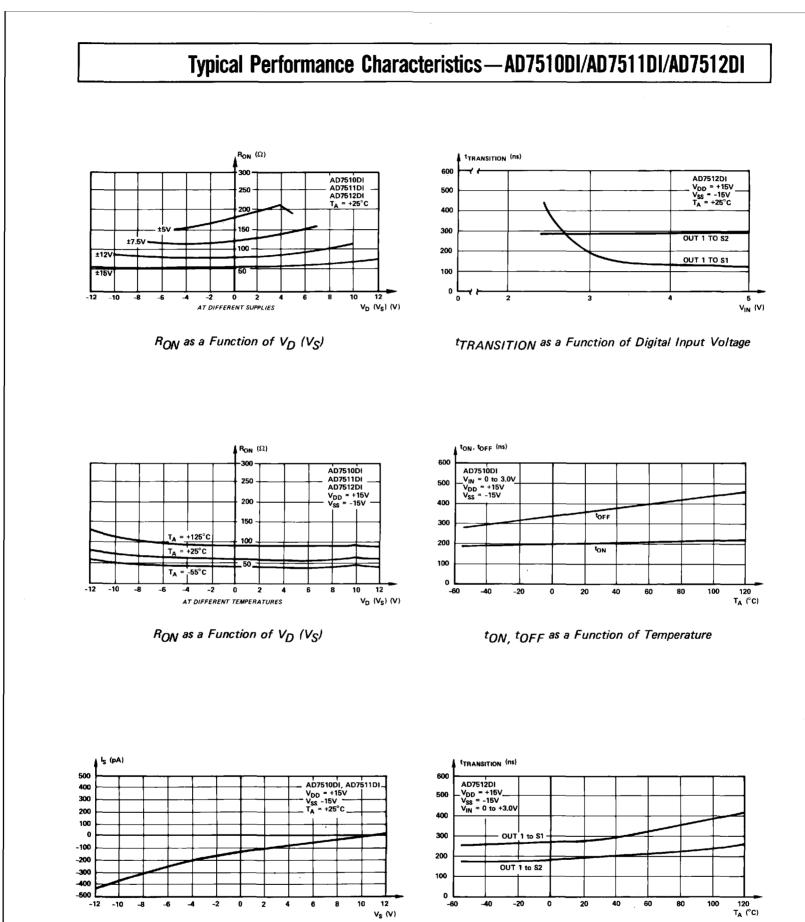

A typical switch channel is shown in Figure 2. The output switching element is comprised of device numbers 4 and 5. Operation is as follows: for an "ON" switch, (in +) is  $V_{DD}$  and (in-) is V<sub>SS</sub> from the driver circuits. Device numbers 1 and 2 are "OFF" and number 3 in "ON". Hence, the backgates of the P- and N-channel output devices (numbers 4 and 5) are tied together and floating. The circled devices are located in separate dielectrically isolated pockets. Floating the output switch backgates with the signal input increases the effective threshold voltage for an applied analog signal, thus providing a flatter R<sub>ON</sub> versus V<sub>S</sub> response.

For an "OFF" switch, device number 3 is "OFF," and the backgates of devices 4 and 5 are tied through  $1k\Omega$  resistors (R1 and R2) to the respective supply voltages through the "ON" devices 1 and 2.

If a voltage is applied to the S or D (OUT) terminal which exceeds  $V_{DD}$  or  $V_{SS}$ , the S- or D-to-backgate diode is forward biased; however, R1 and R2 provide current limiting action to the supplies.

An equivalent circuit of the output switch element in Figure 3

It is possible to turn on an "OFF" switch by applying a voltage in excess of  $V_{DD}$  or  $V_{SS}$  to the S or D terminal. If a positive stress voltage is applied to the S or D terminal which exceeds  $V_{DD}$  by a threshold, then the P-channel (device 5) will turn on creating a low impedance path between the S and D terminals. A similar situation exists for negative stress voltages which exceed V<sub>SS</sub>. In this case the N-channel provides the low impedance path between the S and D terminals. The limiting factor on the overvoltage protection is the power dissipation of the package and is  $\pm 20V$  continuous (or 20mA whichever occurs first) above the supply voltages.

IS, (ID)OFF VS VS

## AD7510DI/AD7511DI/AD7512DI

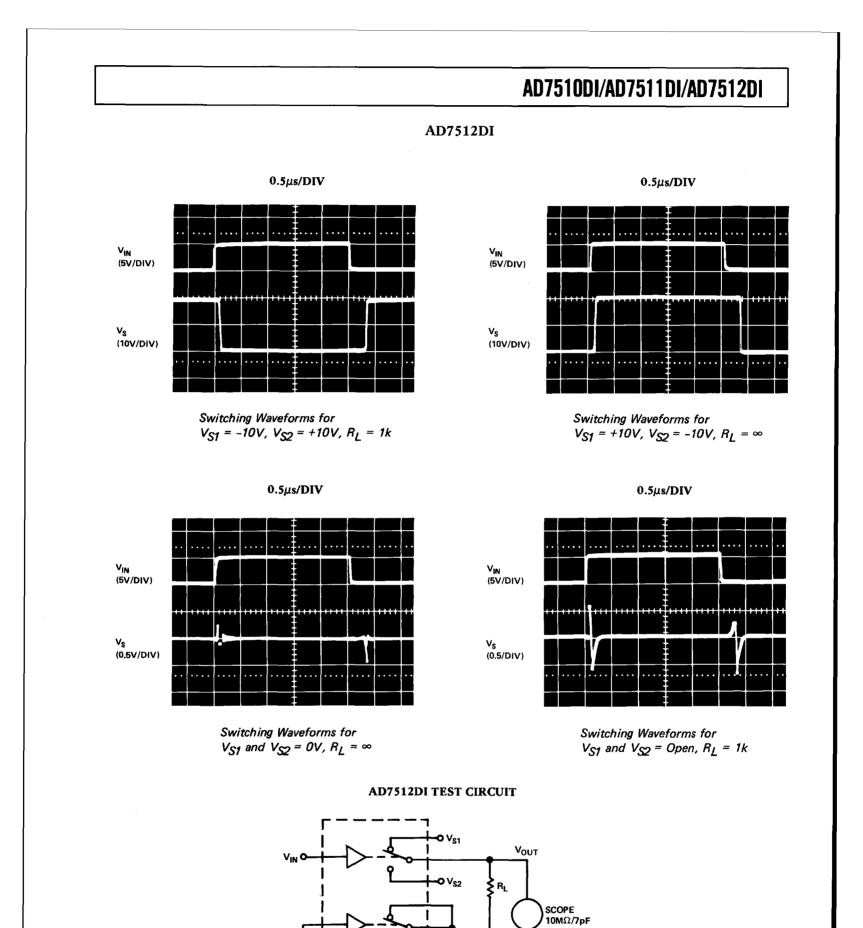

#### **TYPICAL SWITCHING CHARACTERISTICS**

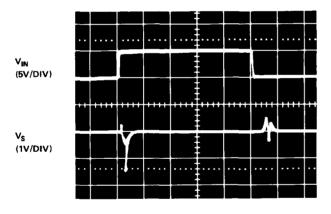

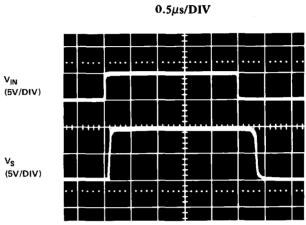

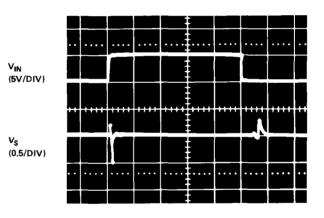

# 0.5µs/DIV

Switching Waveforms for  $V_D = -10V$

0.5µs/DIV

Switching Waveforms for  $V_D = Open$

AD7510DI, AD7511DI

Switching Waveforms for  $V_D = +10V$

Switching Waveforms for  $V_D = 0V$

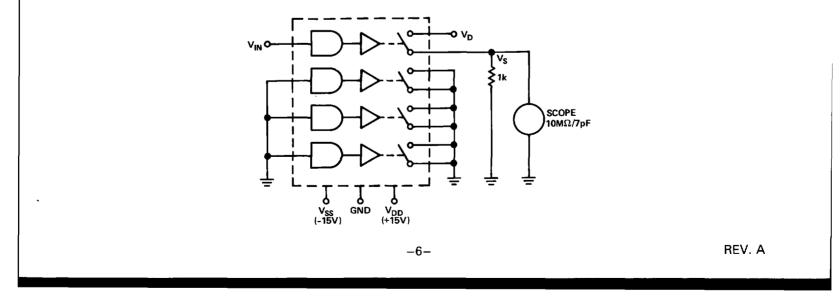

### AD7510DI, AD7511DI TEST CIRCUIT

# 0.546/DIV

## AD7510DI/AD7511DI/AD7512DI

#### TERMINOLOGY

| R <sub>ON</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ohmic resistance between terminals D and S.                                         | $C_{DD}(C_{SS})$        | Capacitance between terminals D(S) of any                                              |           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|-----------|--|

| R <sub>ON</sub> Drift<br>Match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Difference between the R <sub>ON</sub> drift of any two switches.                   |                         | two switches. (This will determine the cross coupling between switches vs. frequency.) |           |  |

| R <sub>ON</sub> Match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Difference between the R <sub>ON</sub> of any two switches.                         | t <sub>ON</sub>         | Delay time between the 50% points of the digital input and switch "ON" condition.      |           |  |

| $I_{D}(I_{S})_{\rm OFF}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Current at terminals D or S. This is a leakage current when the switch is "OFF".    | t <sub>OFF</sub>        | Delay time between the 50% points of the digital input and switch "OFF" condition.     | 3-5/92    |  |

| $I_D(I_S)_{ON} \qquad \begin{array}{l} \text{Leakage current that flows from} \\ \text{switch into the body. (This leakage show up as the difference between current } I_D going into the switch a swit$ | Leakage current that flows from the closed                                          | t <sub>TRANSITION</sub> | Delay time when switching from one address state to another.                           | C393c-3-f |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | show up as the difference between the                                               | V <sub>INL</sub>        | Maximum input voltage for a logic low.                                                 | ŝ         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | current $I_D$ going into the switch and the                                         | VINH                    | Minimum input voltage for a logic high.                                                |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | outgoing current $I_{S.}$                                                           | $I_{INL}(I_{INH})$      | Input current of the digital input.                                                    |           |  |

| $\mathbf{V}_{\mathbf{D}}(\mathbf{V}_{\mathbf{S}})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Analog voltage on terminal D (S).                                                   | CIN                     | Input capacitance to ground of the digital                                             |           |  |

| g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Capacitance between terminal $S(D)$ and                                             |                         | input.                                                                                 |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ground. (This capacitance is specified<br>for the switch open and closed.)          | $V_{DD}$                | Most positive voltage supply.                                                          |           |  |

| C <sub>DS</sub> Cap<br>(Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Capacitance between terminals D and S.<br>(This will determine the switch isolation | V <sub>ss</sub>         | Most negative voltage supply.                                                          |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     | I <sub>DD</sub>         | Positive supply current.                                                               |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | over frequency.)                                                                    | I <sub>ss</sub>         | Negative supply current.                                                               |           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                         |                                                                                        |           |  |

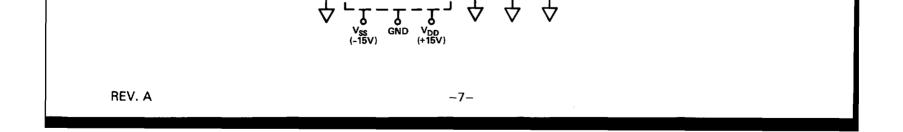

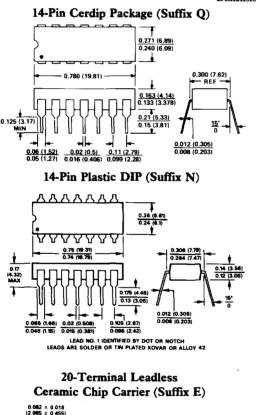

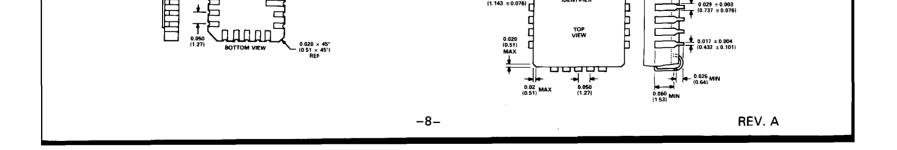

#### **OUTLINE DIMENSIONS**

#### Dimensions shown in inches and (mm).

0000

F

H

┢╾

Þ

Ŧ

0.045 ±0.003 (1.143 ±0.076)

NO.1 PIN

h

C