# 16-BIT ADC in µS08

# **Preliminary Technical Data**

AD7683

### **FEATURES**

16 Bits No Missing Codes (B Grade) INL:  $\pm$  1LSB Typ,  $\pm$  3LSB Max (B Grade) Pseudo-Differential Analog input range: 0V to V<sub>REF</sub> with V<sub>REF</sub> up to VDD No Pipeline Delay Single Supply Operation 5V and 2.7V

Serial Interface SPI/QSPI/μWire/DSP compatible Power Dissipation : 4.5 mW Typ @ 3V/100ksps, 0.45 mW @ 10 kSPS

Stand-by current ( acquisition phase ): 1  $\mu A$  Max  $\mu$ -SO8 Package Improved 2nd Source to ADS8320 and ADS8325

Battery Powered Equipment

Data Acquisition

Instrumentation

Medical Instruments

Process Control

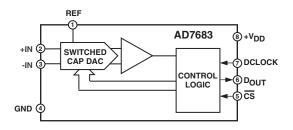

### FUNCTIONAL BLOCK DIAGRAM

## μSO/SOT23 16 Bit ADC

| Type / kSPS  | 100 kSPS      | 250 kSPS      | 380 - 550 kSPS |

|--------------|---------------|---------------|----------------|

| True         | <u>AD7684</u> | <u>AD7687</u> | <u>AD7688</u>  |

| Differential |               |               |                |

| Pseudo       | AD7683        | AD7685        | <u>AD7686</u>  |

| Differential |               |               |                |

| Unipolar     | <u>AD7680</u> |               |                |

## GENERAL DESCRIPTION

The AD7683 is a 16-bit charge redistribution successive-approximation, Analog-to-Digital Converter which operates from a single power supply from 2.7V to 5.5V. It contains a high-speed 16-Bit sampling ADC without any missing codes and a flexible serial interface port. The part also contains a low noise, wide bandwidth, very short aperture delay track/hold circuit which can sample an analog input range from 0V to REF. The reference voltage REF is applied externally and can be set up to the supply voltage.

The AD7683 is fabricated using a CMOS process and is housed in an 8-lead  $\mu$ SOIC package with operation specified from -40°C to +85°C.

## PRODUCT HIGHLIGHTS

1. Superior INL and DNL

The AD7683 has a maximum integral non linearity error of 3 LSBs and 1 LSB typical with no missing 16-bit code.

- 2. 2.7V or 5V Single Supply Operation The AD7683 operates from a single supply. Its power dissipation decreases with the throughput rate ( for instance, 450  $\mu W$  at 10 kHz data rate ). It consumes 1  $\mu A$  maximum during the acquisition phase.

- 3. Serial Interface compatible with SPI and DSP host.

REV. Pr E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: <a href="http://www.analog.com">http://www.analog.com</a>

Fax: 781/326-8703 © Analog Devices, Inc., 2003

# **AD7683—SPECIFICATIONS**

(T\_A = -40°C to +85°C, V\_{REF} = V\_{DD}, V\_{DD} = 2.7V to 5.5 V, 100 kSPS unless otherwise noted.)

|                                                                                                                 | AD7683 All Grades                                                                                                                                                                                                                                                   |                          |                                        |                                  |                                      |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------|----------------------------------|--------------------------------------|

| Parameter                                                                                                       | Conditions                                                                                                                                                                                                                                                          | Min                      | Тур                                    | Max                              | Unit                                 |

| RESOLUTION                                                                                                      |                                                                                                                                                                                                                                                                     | 16                       |                                        |                                  | Bits                                 |

| ANALOG INPUT Voltage Range Absolute Input Voltage  Analog Input CMRR Leakage Current at 25 °C Input Impedance   | +IN+ - (-IN) IN+ IN- f <sub>IN</sub> = TBD kHz 100kSPS Throughput                                                                                                                                                                                                   | 0<br>-0.3<br>-0.3        | TBD<br>TBD<br>See Analog Input Section | $V_{REF}$ $V_{DD} + 0.3$ $0.5$   | V<br>V<br>V<br>dB<br>nA              |

| THROUGHPUT SPEED Complete Cycle Throughput Rate DCLOCK Frequency                                                |                                                                                                                                                                                                                                                                     | 0 0                      |                                        | 10<br>100<br>2.9                 | μs<br>kSPS<br>MHz                    |

| REFERENCE External Reference Voltage Range External Reference Current Drain                                     | 100kSPS Throughput                                                                                                                                                                                                                                                  | 0.5                      | TBD                                    | $V_{\mathrm{DD}}$ + 0.3          | V<br>μ A                             |

| DIGITAL INPUTS  Logic Levels  V <sub>IH</sub> V <sub>IL</sub> I <sub>IH</sub> I <sub>IL</sub> Input Capacitance |                                                                                                                                                                                                                                                                     | +2.0<br>-0.3<br>-1<br>-1 | 5                                      | $V_{\rm DD} + 0.3 + 0.8 + 1 + 1$ | V<br>V<br>μ Α<br>μ Α<br>p F          |

| $\begin{array}{ccc} \overline{DIGITAL} & OUTPUTS \\ Data & Format \\ V_{OH} \\ V_{OL} \end{array}$              | I <sub>SOURCE</sub> = -500 μA<br>I <sub>SINK</sub> = 500 μA                                                                                                                                                                                                         | Se<br>V <sub>DD</sub> -  | rial 16-Bits Straight Bina             | 0.4                              | V<br>V                               |

| POWER SUPPLIES  V <sub>DD</sub> Operating Current  V <sub>DD</sub> Power Dissipation <sup>1</sup>               | Specified Performance 100 kSPS Throughput $V_{\rm DD} = 5V$ $V_{\rm DD} = 3V$ During acquisition phase $V_{\rm DD} = 5V$ , 100 kSPS Throughput $V_{\rm DD} = 5V$ , 10 kSPS Throughput $V_{\rm DD} = 3V$ , 10 kSPS Throughput $V_{\rm DD} = 3V$ , 10 kSPS Throughput | 2.7                      | TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>450 | 5.5<br>1000<br>TBD<br>TBD<br>TBD | V<br>m A<br>m A<br>n A<br>m W<br>m W |

| Power-Down Power <sup>1</sup> TEMPERATURE RANGE <sup>2</sup> Specified Performance                              | $T_{MIN}$ to $T_{MAX}$                                                                                                                                                                                                                                              | -40                      | TBD                                    | +85                              | n W<br>° C                           |

## NOTES

Specifications subject to change without notice.

$<sup>^{1}</sup>$ With all digital inputs forced to  $V_{\mathrm{DD}}$  or GND respectively.

<sup>&</sup>lt;sup>2</sup>Contact factory for extended temperature range.

<sup>&</sup>lt;sup>3</sup>LSB means Least Significant Bit. With the 5 V input range, one LSB is 76.3 µV. With the 2.5 V input range, one LSB is 38.15 µV.

<sup>&</sup>lt;sup>4</sup>See Definition of Specifications section. These specifications do not include the error contribution from the external reference.

<sup>&</sup>lt;sup>5</sup>All specifications in dB are referred to a full-scale input FS. Tested with an input signal at 0.5 dB below full-scale unless otherwise specified.

# $V_{DD} = 5 V$

# (T\_A = -40°C to +85°C, $V_{REF} = 5 V,\, 100$ kSPS unless otherwise noted.)

|                           |                                | AD7683A |           |         | AD7683B |           |         |                  |  |

|---------------------------|--------------------------------|---------|-----------|---------|---------|-----------|---------|------------------|--|

| Parameter                 | Conditions                     | Min     | Typ       | Max     | Min     | Typ       | Max     | Unit             |  |

| DC ACCURACY               |                                |         |           |         |         |           |         |                  |  |

| No Missing Codes          |                                | 15      |           |         | 16      |           |         | Bits             |  |

| Integral Linearity Error  |                                | -6      | ± 3       | + 6     | - 3     | ± 1       | + 3     | LSB <sup>3</sup> |  |

| Offset Error <sup>4</sup> |                                |         | $\pm TBD$ | ± T B D |         | $\pm TBD$ | ± T B D | LSB              |  |

| Offset Temperature Drift  |                                |         | ±ΤΒD      |         |         | ±ΤΒD      |         | ppm/°C           |  |

| Gain Error <sup>4</sup>   | REF = 5 V                      |         |           | ±ΤΒD    |         |           | ±ΤΒD    | % of FSR         |  |

| Gain Error                |                                |         | ±TBD      |         |         | ±TBD      |         | ppm/°C           |  |

| Temperature Drift         |                                |         |           |         |         |           |         |                  |  |

| Transition Noise          |                                |         | 0.7       |         |         | 0.65      |         | LSB              |  |

| Power Supply Sensitivity  | $V_{DD} = 5 \text{ V} \pm 5\%$ |         | ± T B D   |         |         | ± T B D   |         | LSB              |  |

| AC ACCURACY               |                                |         |           |         |         |           |         |                  |  |

| Signal-to-Noise           | $f_{IN} = 1 \text{ kHz}$       |         | 90        |         | 88      | 91        |         | dB <sup>5</sup>  |  |

| SFDR                      | $f_{IN} = 1 \text{ kHz}$       |         | 100       |         |         | 108       |         | d B              |  |

| THD                       | $f_{IN} = 1 \text{ kHz}$       |         | -100      |         |         | -106      |         | d B              |  |

| S/[N+D]                   | $f_{IN} = 1 \text{ kHz}$       |         | 90        |         | 88      | 91        |         | d B              |  |

|                           | $f_{IN} = 1 \text{ kHz},$      |         |           |         |         |           |         |                  |  |

|                           | -60 dB Input                   |         | 30        |         |         | 3 1       |         | d B              |  |

| Effective Number of Bits  | $f_{IN} = 1 \text{ kHz}$       |         | 14.7      |         |         | 14.8      |         | Bits             |  |

| -3 dB Input Bandwidth     |                                |         | 9         |         |         | 9         |         | MHz              |  |

| Full-Power Bandwidth      | $f_{IN}$ , SINAD at -3dB       |         | TBD       |         |         | TBD       |         | kHz              |  |

# $V_{DD} = 2.7 V$

# $(T_A = -40$ °C to +85°C, $V_{REF} = 2.5V$ , 100 kSPS unless otherwise noted.)

|                           |                                 | AD7683A |           | AD7683B |     |         |      |                  |

|---------------------------|---------------------------------|---------|-----------|---------|-----|---------|------|------------------|

| Parameter                 | Conditions                      | Min     | Typ       | Max     | Min | Typ     | Max  | Unit             |

| DC ACCURACY               |                                 |         |           |         |     |         |      |                  |

| No Missing Codes          |                                 | 15      |           |         | 16  |         |      | Bits             |

| Integral Linearity Error  |                                 | -6      | ± 3       | + 6     | -3  | ± 1     | + 3  | LSB <sup>3</sup> |

| Offset Error <sup>4</sup> |                                 |         | $\pm TBD$ | ±ΤΒD    |     | ±ΤΒD    | ±ΤΒD | LSB              |

| Offset Temperature Drift  |                                 |         | ± T B D   |         |     | ±ΤΒD    |      | ppm/°C           |

| Gain Error <sup>4</sup>   | REF = 5 V                       |         |           | ± TBD   |     |         | ±ΤΒD | % of FSR         |

| Gain Error                |                                 |         | ±ΤΒD      |         |     | ±TBD    |      | ppm/°C           |

| Temperature Drift         |                                 |         |           |         |     |         |      |                  |

| Transition Noise          |                                 |         | 0.7       |         |     | 0.65    |      | LSB              |

| Power Supply Sensitivity  | $V_{DD} = 5 \text{ V} \pm 5\%$  |         | ±TBD      |         |     | ± T B D |      | LSB              |

| AC ACCURACY               |                                 |         |           |         |     |         |      |                  |

| Signal-to-Noise           | $f_{IN} = 1 \text{ kHz}$        |         | 85        |         |     | 86      |      | dB <sup>5</sup>  |

| SFDR                      | $f_{IN} = 1 \text{ kHz}$        |         | 96        |         |     | 100     |      | d B              |

| THD                       | $f_{IN} = 1 \text{ kHz}$        |         | -94       |         |     | -98     |      | d B              |

| S/[N+D]                   | $f_{IN} = 1 \text{ kHz}$        |         | 85        |         |     | 86      |      | d B              |

|                           | $f_{IN} = 1 \text{ kHz},$       |         |           |         |     |         |      |                  |

|                           | −60 dB Input                    |         | 25        |         |     | 26      |      | d B              |

| Effective Number of Bits  | $f_{IN} = 1 \text{ kHz}$        |         | 13.8      |         |     | 14      |      | Bits             |

| -3 dB Input Bandwidth     |                                 |         | 9         |         |     | 9       |      | MHz              |

| Full-Power Bandwidth      | f <sub>IN</sub> , SINAD at -3dB |         | TBD       |         |     | TBD     |      | kHz              |

# NOTES

$<sup>^{1}</sup>$ With all digital inputs forced to  $V_{\mathrm{DD}}$  or GND respectively.

<sup>&</sup>lt;sup>2</sup>Contact factory for extended temperature range.

<sup>&</sup>lt;sup>3</sup>LSB means Least Significant Bit. With the 5 V input range, one LSB is 76.3 µV. With the 2.5 V input range, one LSB is 38.15 µV.

<sup>&</sup>lt;sup>4</sup>See Definition of Specifications section. These specifications do not include the error contribution from the external reference.

<sup>&</sup>lt;sup>5</sup>All specifications in dB are referred to a full-scale input FS. Tested with an input signal at 0.5 dB below full-scale unless otherwise specified.

# **AD7683—SPECIFICATIONS**

# TIMING SPECIFICATIONS ( $-40^{\circ}$ C to $+85^{\circ}$ C, $V_{DD}$ = 2.7 V to 5.5V, unless otherwise stated)

|                                                                   | Symbol            | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|-------------------|-----|-----|-----|------|

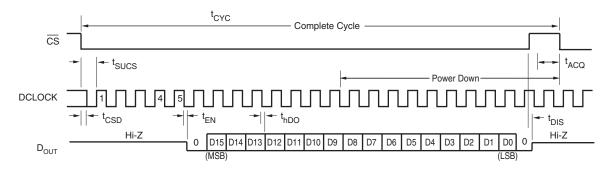

| Refer to Figure 3                                                 |                   |     |     |     |      |

| Throughput rate                                                   | t <sub>CYC</sub>  |     |     | 100 | kHz  |

| CS Falling to DCLOCK Low                                          | t <sub>CSD</sub>  |     |     | 0   | ns   |

| CS Falling to DCLOCK Rising                                       | t <sub>SUCS</sub> | 20  |     |     | ns   |

| DCLOCK Falling to Data remains Valid                              | $t_{ m hDO}$      | 5   | TBD |     | ns   |

| $\overline{\text{CS}}$ Rising edge to $\text{D}_{\text{OUT}}$ HiZ | t <sub>DIS</sub>  |     | TBD | 100 | ns   |

| DCLOCK Falling to Data Valid                                      | t <sub>EN</sub>   |     | TBD | 50  | ns   |

| Acquisition Time                                                  | $t_{ACQ}$         | 400 |     |     | ns   |

| D <sub>OUT</sub> Fall Time                                        | $t_{\mathrm{F}}$  |     | TBD | 25  | ns   |

| D <sub>OUT</sub> Rise Time                                        | t <sub>R</sub>    |     | TBD | 25  | ns   |

Specifications subject to change without notice.

NOTE: A minimum of 22 clock cycles are required for 16-bit conversion. Shown are 24 clock cycles.  $D_{\mbox{OUT}}$  goes low on the DCLOCK falling edge following the LSB reading.

Figure 3. Serial Interface Timing.

REV. Pr E \_\_4\_

# AD7683

# ABSOLUTE MAXIMUM RATINGS1

Analog Inputs

$+\text{IN}^2$ ,  $-\text{IN}^2$ , REF, ..... GND -0.3 V to  $V_{DD}$  + 0.3 V

Supply Voltages  $V_{DD}$  to GND . . . . . -0.3 V to 6 V

Digital Inputs to GND . . . . . . . . -0.3 V to  $V_{DD}$  + 0.3 V

Digital Outputs to GND ......-0.3 V to  $V_{DD}$  + 0.3 V

| Internal Power Dissipation <sup>3</sup>             | 325 mW         |

|-----------------------------------------------------|----------------|

| Junction Temperature                                |                |

| Storage Temperature Range                           | 65°C to +150°C |

| Lead Temperature Range                              |                |

| (Soldering 10 sec)                                  | 300°C          |

| Storage Temperature Range<br>Lead Temperature Range | 65°C to +150°C |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ORDERING GUIDE

| Model                                                                                                                                               | Maximum<br>INL                       | No Missing<br>Code                   | Temperature<br>Range                                                 | Package<br>Description | Package<br>Option | Brand                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------------------------------|------------------------|-------------------|--------------------------|

| AD7683ARM AD7683ARMRL7 AD7683BRM AD7683BRMRL7 EVAL-AD7683CB <sup>1</sup> EVAL-CONTROL EVAL-CONTROL BRD2 <sup>2</sup> EVAL-CONTROL BRD3 <sup>2</sup> | ±6 LSB<br>±6 LSB<br>±3 LSB<br>±3 LSB | 15bits<br>15bits<br>16bits<br>16bits | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C | μSOIC-8<br>μSOIC-8     | oard              | C1L<br>C1L<br>C1C<br>C1C |

#### NOTES

<sup>&</sup>lt;sup>2</sup>These boards allow a PC to control and communicate with all Analog Devices evaluation boards ending in the CB designators.

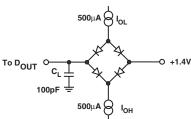

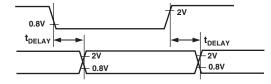

Figure 1. Load Circuit for Digital Interface Timing.

Figure 2. Voltage Reference Levels for Timing.

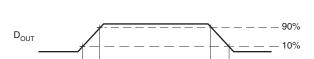

Figure 3.  $D_{OUT}$  rise and fall timing.

## **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7683 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup>See Analog Input section.

<sup>&</sup>lt;sup>3</sup>Specification is for device in free air:  $\mu$ SOIC-8:  $\theta_{JA} = 200^{\circ}$ C/W.

<sup>&</sup>lt;sup>1</sup>This board can be used as a standalone evaluation board or in conjunction with the EVAL-CONTROL BRDx for evaluation/demonstration purposes.

# **AD7683**

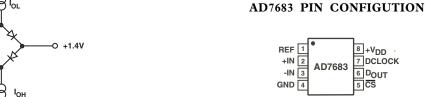

# PIN FUNCTION DESCRIPTIONS

| Pin # | Mnemonic                                     |    | Function                                                                                                                                                                                                                                                       |

|-------|----------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | REF                                          | ΑI | Reference Input Voltage. The REF range is from TBD to VDD. It is referred to the GND ground. This pin should be decoupled closely to the pin with a TBD µFcapacitor.                                                                                           |

| 2     | + I N                                        | ΑI | Analog Input. It is referred to -IN. The voltage difference between +IN and -IN range is $0V$ to $V_{\rm RFF}$ .                                                                                                                                               |

| 3     | -I N                                         | ΑI | Sense Analog Input Ground. To be connected to the analog ground plane or to a remote sense ground.                                                                                                                                                             |

| 4     | $\frac{G N D}{C S}$                          | P  | Power Supply Ground.                                                                                                                                                                                                                                           |

| 5     | $\overline{\mathtt{C}}\overline{\mathtt{S}}$ | DΙ | Chip Select Input. This input has multiple functions. It initiates a complete conversion process on its falling edge. The part returns in shutdown mode as soon as the conversion is done. It also enables $D_{OUT}$ . When high, $D_{OUT}$ is high impedance. |

| 6     | $\mathrm{D}_{\mathrm{OUT}}$                  | DΟ | Serial Data Output.                                                                                                                                                                                                                                            |

| 7     | DCLOCK                                       | DΙ | Serial Data Clock Input. It synchronizes the serial data transfer.                                                                                                                                                                                             |

| 8     | $V_{\mathrm{DD}}$                            | P  | Power Supply.                                                                                                                                                                                                                                                  |

NOTES

AI = Analog Input

DI = Digital Input

DO = Digital Output

DO = Digital Output

P = Power

REV. Pr E -6-

AD7683

### **DEFINITION OF SPECIFICATIONS**

# INTEGRAL NONLINEARITY ERROR (INL)

Linearity error refers to the deviation of each individual code from a line drawn from "negative full scale" through "positive full scale". The point used as "negative full scale" occurs 1/2 LSB before the first code transition. "Positive full scale" is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line.

## DIFFERENTIAL NONLINEARITY ERROR (DNL)

In an ideal ADC, code transitions are 1 LSB apart. Differential nonlinearity is the maximum deviation from this ideal value. It is often specified in terms of resolution for which no missing codes are guaranteed.

## **GAIN ERROR**

The last transition (from 111...10 to 111...11) should occur for an analog voltage 1 1/2 LSB below the nominal full scale (4.999886 V for the 0 V to 5 V range). The gain error is the deviation of the actual level of the last transition from the ideal level after the offset has been adjusted out.

### OFFSET ERROR

The first transition should occur at a level 1/2 LSB above analog ground (38.1  $\mu$ V for the 0 V to 5 V range). The offset error is the deviation of the actual transition from that point.

# SPURIOUS FREE DYNAMIC RANGE (SFDR)

The difference, in decibels (dB), between the rms amplitude of the input signal and the peak spurious signal.

# EFFECTIVE NUMBER OF BITS (ENOB)

ENOB is a measurement of the resolution with a sine wave input. It is related to S/(N+D) by the following formula:

ENOB =

$$(S/[N+D]_{dB} - 1.76)/6.02)$$

and is expressed in bits.

## TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first five harmonic components to the rms value of a full-scale input signal and is expressed in decibels.

### SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

# SIGNAL TO (NOISE + DISTORTION) RATIO (S/[N+D])

S/(N+D) is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/(N+D) is expressed in decibels

\_7\_ REV. Pr E

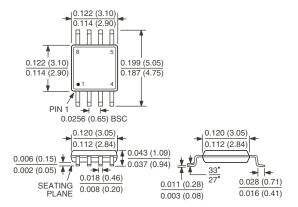

## **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

# 8-Lead μSOIC (RM-8)

REV. Pr E \_\_8\_