## Aبر 270 MHz, 400 A Current Feedback Amplifier

## AD8005

#### FEATURES

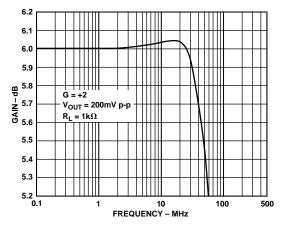

**Ultralow Power** 400  $\mu$ A Power Supply Current (4 mW on ±5 V<sub>s</sub>) **Specified for Single Supply Operation High Speed** 270 MHz, -3 dB Bandwidth (G = +1) 170 MHz, -3 dB Bandwidth (G = +2) 280 V/µs Slew Rate (G = +2) 28 ns Settling Time to 0.1%, 2 V Step (G = +2) Low Distortion/Noise -63 dBc @ 1 MHz, V<sub>0</sub> = 2 V p-p –50 dBc @ 10 MHz, V<sub>o</sub> = 2 V p-p 4.0 nV/<del>VHz</del> Input Voltage Noise @ 10 MHz Good Video Specifications ( $R_1 = 1 k\Omega$ , G = +2) Gain Flatness 0.1 dB to 30 MHz 0.11% Differential Gain Error 0.4° Differential Phase Error

APPLICATIONS Signal Conditioning A/D Buffer Power-Sensitive, High-Speed Systems Battery Powered Equipment Loop/Remote Power Systems Communication or Video Test Systems Portable Medical Instruments

#### **PRODUCT DESCRIPTION**

The AD8005 is an ultralow power, high-speed amplifier with a wide signal bandwidth of 170 MHz and slew rate of 280 V/ $\mu$ s. This performance is achieved while consuming only 400  $\mu$ A of quiescent supply current. These features increase the operating time of high-speed battery-powered systems without reducing dynamic performance.

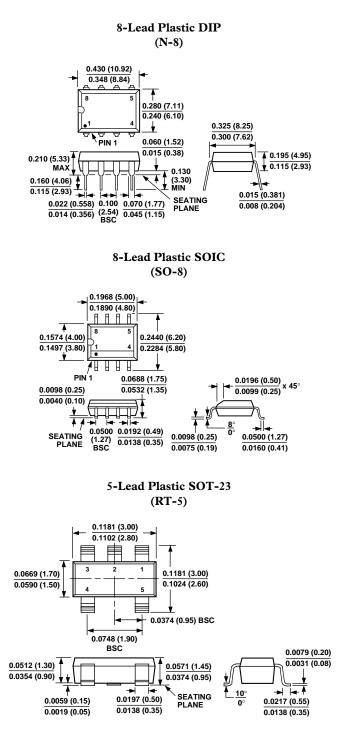

Figure 1. Frequency Response; G = +2,  $V_S = +5$  V or  $\pm 5$  V

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

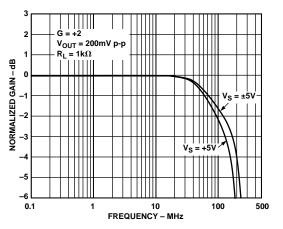

### FUNCTIONAL BLOCK DIAGRAM 8-Lead Plastic DIP and SOIC

The current feedback design results in gain flatness of 0.1 dB to 30 MHz while offering differential gain and phase errors of 0.11% and  $0.4^{\circ}$ . Harmonic distortion is low over a wide bandwidth with THDs of -63 dBc at 1 MHz and -50 dBc at 10 MHz. Ideal features for a signal conditioning amplifier or buffer to a high-speed A-to-D converter in portable video, medical or communication systems.

The AD8005 is characterized for +5 V and  $\pm 5$  V supplies and will operate over the industrial temperature range of  $-40^{\circ}$ C to +85°C. The amplifier is supplied in 8-lead plastic DIP, 8-lead SOIC and 5-lead SOT-23 packages.

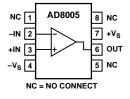

Figure 2. Distortion vs. Frequency;  $V_S = \pm 5 V$

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1999

# AD8005–SPECIFICATIONS

## $\pm 5 \text{ V SUPPLIES}$ (@ T<sub>A</sub> = +25°C, V<sub>S</sub> = ±5 V, R<sub>L</sub> = 1 k $\Omega$ unless otherwise noted)

| Parameter                                 | Conditions                                                                                                                                                                     | Min        | AD8005A<br>Typ                            | Max        | Units                  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------|------------|------------------------|

| DYNAMIC PERFORMANCE                       | $R_F$ = 3.01 kΩ for "N" Package or<br>$R_F$ = 2.49 kΩ for "R" Package or<br>$R_F$ = 2.1010 f "R" Package or                                                                    |            |                                           |            |                        |

| -3 dB Small Signal Bandwidth              | $ \begin{array}{c} R_{\rm F} = 2.10 \ \rm k\Omega \ for \ ``RT'' \ Package \\ G = +1, \ V_{\rm O} = 0.2 \ \rm V \ p-p \\ G = +2, \ V_{\rm O} = 0.2 \ \rm V \ p-p \end{array} $ | 225<br>140 | 270<br>170                                |            | MHz<br>MHz             |

| Bandwidth for 0.1 dB Flatness             | $G = +2, V_0 = 0.2 V p-p$<br>$G = +2, V_0 = 0.2 V p-p$                                                                                                                         | 10         | 30                                        |            | MHz                    |

| Large Signal Bandwidth                    | $G = +10, V_0 = 4 V p-p, R_F = 499 Ω$                                                                                                                                          |            | 40                                        |            | MHz                    |

| Slew Rate (Rising Edge)                   | $G = +2, V_0 = 4 V$ Step<br>$G = -1, V_0 = 4 V$ Step, $R_F = 1.5 k\Omega$                                                                                                      |            | 280<br>1500                               |            | V/µs<br>V/µs           |

| Settling Time to 0.1%                     | $G = -1, v_0 = 4 v$ Step, $R_F = 1.5 R_2^2$<br>$G = +2, V_0 = 2 V$ Step                                                                                                        |            | 28                                        |            | ns                     |

| DISTORTION/NOISE PERFORMANCE              | $R_F$ = 3.01 kΩ for "N" Package or<br>$R_F$ = 2.49 kΩ for "R" Package or<br>$R_F$ = 2.10 kΩ for "RT" Package                                                                   |            |                                           |            |                        |

| Total Harmonic Distortion                 | $K_F = 2.10 \text{ K}_2$ for K1 Fackage<br>$f_C = 1 \text{ MHz}, V_O = 2 \text{ V p-p}, G = +2$                                                                                |            | -63                                       |            | dBc                    |

|                                           | $f_{C} = 10 \text{ MHz}, V_{O} = 2 \text{ V p-p}, G = +2$                                                                                                                      |            | -50                                       |            | dBc                    |

| Differential Gain                         | NTSC, $G = +2$                                                                                                                                                                 |            | 0.11                                      |            | %                      |

| Differential Phase<br>Input Voltage Noise | NTSC, $G = +2$<br>f = 10 MHz                                                                                                                                                   |            | $\begin{array}{c} 0.4 \\ 4.0 \end{array}$ |            | Degrees $nV/\sqrt{Hz}$ |

| Input Current Noise                       | $f = 10 \text{ MHz}, +I_{IN}$                                                                                                                                                  |            | 1.1                                       |            | $pA/\sqrt{Hz}$         |

|                                           | -I <sub>IN</sub>                                                                                                                                                               |            | 9.1                                       |            | pA/√Hz                 |

| DC PERFORMANCE                            |                                                                                                                                                                                |            | _                                         | 20         |                        |

| Input Offset Voltage                      | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                           |            | 5                                         | 30<br>50   | $\pm mV$<br>$\pm mV$   |

| Offset Drift                              |                                                                                                                                                                                |            | 40                                        | 50         | μV/°C                  |

| +Input Bias Current                       |                                                                                                                                                                                |            | 0.5                                       | 1          | ±μΑ                    |

| Levent Disc Comment                       | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                           |            | _                                         | 2          | ±μΑ                    |

| –Input Bias Current                       | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                           |            | 5                                         | 10<br>12   | ±μA<br>±μA             |

| Input Bias Current Drift (±)              |                                                                                                                                                                                |            | 6                                         | 12         | nA/°C                  |

| Open-Loop Transimpedance                  |                                                                                                                                                                                | 400        | 1000                                      |            | kΩ                     |

| INPUT CHARACTERISTICS                     |                                                                                                                                                                                |            | 0.0                                       |            | NO                     |

| Input Resistance                          | +Input<br>–Input                                                                                                                                                               |            | 90<br>260                                 |            | MΩ<br>Ω                |

| Input Capacitance                         | +Input                                                                                                                                                                         |            | 1.6                                       |            | pF                     |

| Input Common-Mode Voltage Range           | -                                                                                                                                                                              |            | 3.8                                       |            | ±V                     |

| Common-Mode Rejection Ratio               | $V_{CM} = \pm 2.5 V$                                                                                                                                                           | 46         | 54                                        |            | dB                     |

| OUTPUT CHARACTERISTICS                    |                                                                                                                                                                                |            |                                           |            |                        |

| Output Voltage Swing                      | Positive<br>Negative                                                                                                                                                           | +3.7       | +3.90<br>-3.90                            | -3.7       |                        |

| Output Current                            | $R_{\rm I} = 50 \ \Omega$                                                                                                                                                      |            | -3.90<br>10                               | -5.1       | mA                     |

| Short Circuit Current                     |                                                                                                                                                                                |            | 60                                        |            | mA                     |

| POWER SUPPLY                              |                                                                                                                                                                                |            | 400                                       | 4775       |                        |

| Quiescent Current                         | $T_{MIN}$ to $T_{MAX}$                                                                                                                                                         |            | 400                                       | 475<br>560 | μΑ                     |

| Power Supply Rejection Ratio              | $V_{\rm MIN}$ to $T_{\rm MAX}$<br>$V_{\rm S} = \pm 4$ V to $\pm 6$ V                                                                                                           | 56         | 66                                        | 000        | μA<br>dB               |

| OPERATING TEMPERATURE RANGE               |                                                                                                                                                                                | -40        |                                           | +85        | °C                     |

Specifications subject to change without notice.

## +5 V SUPPLY (@ $T_A$ = +25°C, $V_S$ = +5 V, $R_L$ = 1 k $\Omega$ to 2.5 V unless otherwise noted)

| Parameter                                                                                                          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min        | AD8005A<br>Typ                                  | Max        | Units                                                    |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|------------|----------------------------------------------------------|

| DYNAMIC PERFORMANCE                                                                                                | $R_F$ = 3.01 kΩ for "N" Package or<br>$R_F$ = 2.49 kΩ for "R" Package or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                 |            |                                                          |

| -3 dB Small Signal Bandwidth                                                                                       | $R_{F} = 2.10 \text{ k}\Omega \text{ for "RT" Package} \\ G = +1, V_{O} = 0.2 \text{ V p-p} \\ G = +2, V_{O} = 0.2 \text{ V p-p} $                                                                                                                                                                                                                                                                                                                                                                                                                      | 190<br>110 | 225<br>130                                      |            | MHz<br>MHz                                               |

| Bandwidth for 0.1 dB Flatness<br>Large Signal Bandwidth<br>Slew Rate (Rising Edge)<br>Settling Time to 0.1%        | $G = +2, V_0 = 0.2 V p p$ $G = +2, V_0 = 0.2 V p - p$ $G = +10, V_0 = 2 V p - p, R_F = 499 \Omega$ $G = +2, V_0 = 2 V Step$ $G = -1, V_0 = 2 V Step, R_F = 1.5 k\Omega$ $G = +2, V_0 = 2 V Step$                                                                                                                                                                                                                                                                                                                                                        | 10         | 30<br>45<br>260<br>775<br>30                    |            | MHZ<br>MHZ<br>V/µs<br>V/µs<br>ns                         |

| DISTORTION/NOISE PERFORMANCE                                                                                       | $R_F$ = 3.01 kΩ for "N" Package or<br>$R_F$ = 2.49 kΩ for "R" Package or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                 |            |                                                          |

| Total Harmonic Distortion<br>Differential Gain<br>Differential Phase<br>Input Voltage Noise<br>Input Current Noise | $ \begin{array}{l} R_{\rm F} = 2.10 \; {\rm k\Omega} \; {\rm for} \; "{\rm RT}" \; {\rm Package} \\ f_{\rm C} = 1 \; {\rm MHz}, V_{\rm O} = 2 \; {\rm V} \; {\rm p-p}, \; {\rm G} = +2 \\ f_{\rm C} = 10 \; {\rm MHz}, \; {\rm V}_{\rm O} = 2 \; {\rm V} \; {\rm p-p}, \; {\rm G} = +2 \\ {\rm NTSC}, \; {\rm G} = +2, \; {\rm R_L} \; {\rm to} \; 1.5 \; {\rm V} \\ {\rm NTSC}, \; {\rm G} = +2, \; {\rm R_L} \; {\rm to} \; 1.5 \; {\rm V} \\ {\rm f} = 10 \; {\rm MHz} \\ {\rm f} = 10 \; {\rm MHz}, \; {\rm H_{IN}} \\ - {\rm I_{IN}} \end{array} $ |            | -60<br>-50<br>0.14<br>0.70<br>4.0<br>1.1<br>9.1 |            | dBc<br>dBc<br>%<br>Degrees<br>nV/√Hz<br>pA/√Hz<br>pA/√Hz |

| DC PERFORMANCE<br>Input Offset Voltage                                                                             | T to T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | 5                                               | 35<br>50   | $\pm mV$<br>$\pm mV$                                     |

| Offset Drift<br>+Input Bias Current                                                                                | $T_{\rm MIN}$ to $T_{\rm MAX}$ $T_{\rm MIN}$ to $T_{\rm MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 40<br>0.5                                       | 1<br>2     | μV/°C<br>±μA<br>±μA                                      |

| –Input Bias Current<br>Input Bias Current Drift (±)<br>Open-Loop Transimpedance                                    | $T_{MIN}$ to $T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50         | 5<br>8<br>500                                   | 10<br>11   | ±μA<br>±μA<br>nA/°C<br>kΩ                                |

| INPUT CHARACTERISTICS<br>Input Resistance                                                                          | +Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | 120                                             |            | ΜΩ                                                       |

| Input Capacitance<br>Input Common-Mode Voltage Range<br>Common-Mode Rejection Ratio                                | -Input<br>+Input<br>V <sub>CM</sub> = 1.5 V to 3.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48         | 300<br>1.6<br>1.5 to 3.5<br>54                  |            | Ω<br>pF<br>V<br>dB                                       |

| OUTPUT CHARACTERISTICS<br>Output Voltage Swing<br>Output Current<br>Short Circuit Current                          | $R_{\rm L} = 50 \ \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.1 to 3.9 | 0.95 to 4.05<br>10<br>30                        |            | V<br>mA<br>mA                                            |

| POWER SUPPLY<br>Quiescent Current                                                                                  | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | 350                                             | 425<br>475 | μΑ<br>μΑ                                                 |

| Power Supply Rejection Ratio                                                                                       | $V_{\rm MIN}$ to $T_{\rm MAX}$<br>$V_{\rm S} = +4$ V to +6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56         | 66                                              | נוד        | dB                                                       |

| OPERATING TEMPERATURE RANGE                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -40        |                                                 | +85        | °C                                                       |

Specifications subject to change without notice.

### AD8005

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage 12.6 V                               |

|-----------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>             |

| Plastic DIP Package (N)1.3 Watts                    |

| Small Outline Package (R)0.75 Watts                 |

| SOT-23-5 Package (RT) 0.5 Watts                     |

| Input Voltage (Common Mode) $\dots \pm V_S \pm 1 V$ |

| Differential Input Voltage±3.5 V                    |

| Output Short Circuit Duration                       |

| Observe Power Derating Curves                       |

Storage Temperature Range

| N, R & RT Package $\dots \dots \dots$ |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Operating Temperature Range (A Grade)40°C to +85°C                                                                                    |

| Lead Temperature Range (Soldering 10 sec) +300°C                                                                                      |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Specification is for device in free air:

8-Lead Plastic DIP Package:  $\theta_{JA}$  = 90°C/W

8-Lead SOIC Package:  $\theta_{IA} = 155^{\circ}C/W$

5-Lead SOT-23 Package:  $\theta_{JA} = 240^{\circ}C/W$

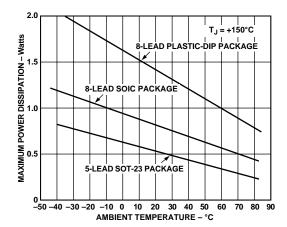

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8005 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately  $+150^{\circ}$ C. Exceeding this limit temporarily may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of  $+175^{\circ}$ C for an extended period can result in device failure.

While the AD8005 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (+150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves shown in Figure 3.

Figure 3. Maximum Power Dissipation vs. Temperature

| Model                                                                                        | Temperature                                                                                                                | Package                                                                                                                     | Package                                     | Brand      |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|

|                                                                                              | Range                                                                                                                      | Description                                                                                                                 | Option                                      | Code       |

| AD8005AN<br>AD8005AR<br>AD8005AR-REEL<br>AD8005ART-REEL<br>AD8005AR-REEL7<br>AD8005ART-REEL7 | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C | 8-Lead Plastic DIP<br>8-Lead Plastic SOIC<br>13" Tape and Reel<br>13" Tape and Reel<br>7" Tape and Reel<br>7" Tape and Reel | N-8<br>SO-8<br>SO-8<br>RT-5<br>SO-8<br>RT-5 | H1A<br>H1A |

#### **ORDERING GUIDE**

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8005 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

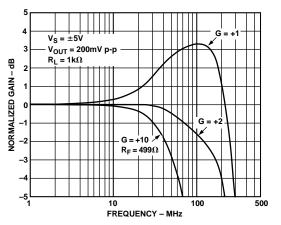

Figure 4. Frequency Response;  $G = +1, +2, +10; V_S = \pm 5 V$

Figure 5. Gain Flatness; G = +2;  $V_S = \pm 5 V \text{ or } +5 V$

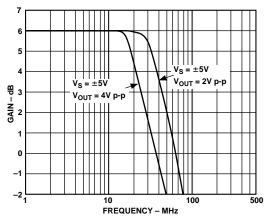

Figure 6. Large Signal Frequency Response; G = +2,  $R_L = 1 \ k\Omega$

### **Typical Characteristics-AD8005**

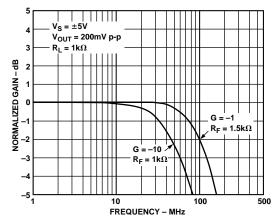

Figure 7. Frequency Response; G = -1, -10;  $V_S = \pm 5 V$

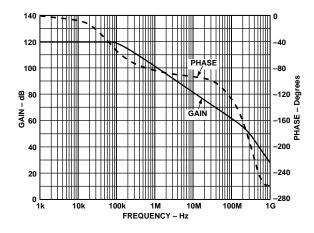

Figure 8. Transimpedance Gain and Phase vs. Frequency

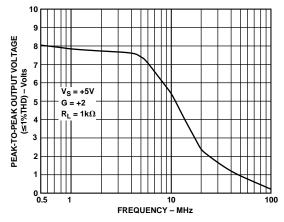

Figure 9. Output Swing vs. Frequency;  $V_S = \pm 5 V$

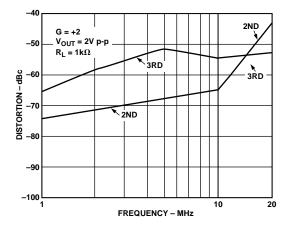

### **AD8005–Typical Characteristics**

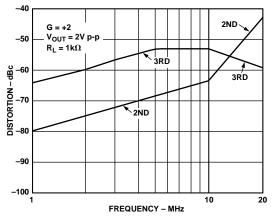

Figure 10. Distortion vs. Frequency;  $V_S = \pm 5 V$

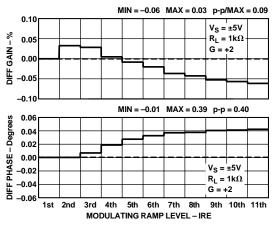

Figure 11. Differential Gain and Phase,  $V_S = \pm 5 V$

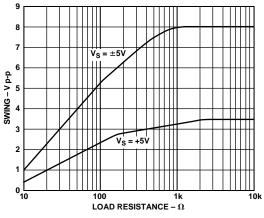

Figure 12. Output Voltage Swing vs. Load

Figure 13. Distortion vs. Frequency  $V_S = +5 V$

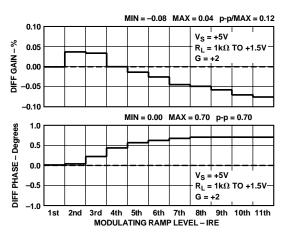

Figure 14. Differential Gain and Phase,  $V_S = +5 V$

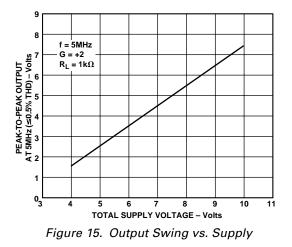

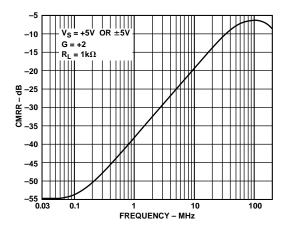

Figure 16. CMRR vs. Frequency;  $V_S = +5 V \text{ or } \pm 5 V$

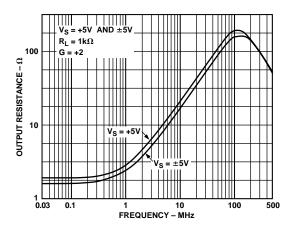

Figure 17. Output Resistance vs. Frequency;  $V_S = \pm 5 V$  and  $\pm 5 V$

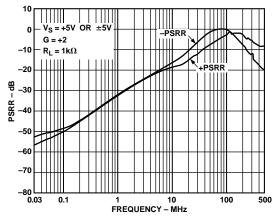

Figure 18. PSRR vs. Frequency;  $V_S = +5 V \text{ or } \pm 5 V$

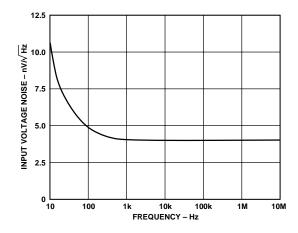

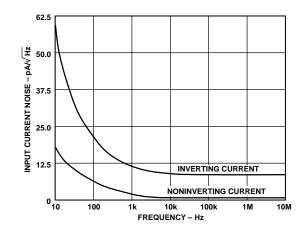

Figure 19. Noise vs. Frequency;  $V_S = +5 V \text{ or } \pm 5 V$

Figure 20. Noise vs. Frequency;  $V_S = +5 V \text{ or } \pm 5 V$

Figure 21.  $\pm$ Overdrive Recovery,  $V_S = \pm 5 V$ ,  $V_{IN} = 2 V$  Step

### **AD8005–Typical Characteristics**

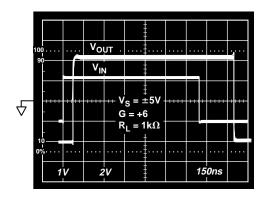

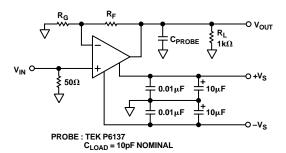

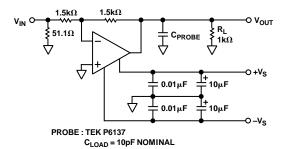

Figure 22. Test Circuit; G = +2;  $R_F = R_G = 3.01 \text{ k}\Omega$  for N Package;  $R_F = R_G = 2.49 \text{ k}\Omega$  for R and RT Packages

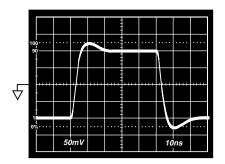

Figure 23. 200 mV Step Response; G = +2, V\_S =  $\pm 2.5$  V or  $\pm 5$  V

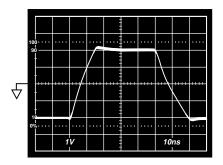

Figure 24. Step Response; G = +2,  $V_S = \pm 5 V$

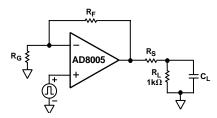

Figure 25. Test Circuit; G = -1,  $R_F = R_G = 1.5 k\Omega$  for N, R and RT Packages

| 100···· |      |      |      |  |

|---------|------|------|------|--|

| Ĩ       |      |      |      |  |

|         |      | <br> | N. I |  |

| 7       |      |      |      |  |

| 10      |      |      |      |  |

| 0%····  |      | <br> | V/-  |  |

|         | 50mV |      | 10ns |  |

Figure 26. 200 mV Step Response; G = –1,  $V_S$  = ±2.5 V or ±5 V

| 1 | 00···· | <br> | <br> | <br> |    |    |  |

|---|--------|------|------|------|----|----|--|

|   | 1      |      |      |      |    |    |  |

|   |        |      | <br> |      |    |    |  |

| 7 | -      |      |      |      |    |    |  |

|   | 10     |      |      |      |    |    |  |

|   | 0%     | <br> | <br> | <br> |    |    |  |

|   |        | 1V   |      |      | 10 | ns |  |

Figure 27. Step Response; G = -1,  $V_S = \pm 5 V$

#### APPLICATIONS

#### **Driving Capacitive Loads**

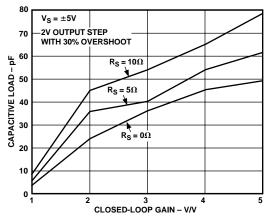

Capacitive loads interact with an op amp's output impedance to create an extra delay in the feedback path. This reduces circuit stability, and can cause unwanted ringing and oscillation. A given value of capacitance causes much less ringing when the amplifier is used with a higher noise gain.

The capacitive load drive of the AD8005 can be increased by adding a low valued resistor in series with the capacitive load. Introducing a series resistor tends to isolate the capacitive load from the feedback loop thereby diminishing its influence. Figure 29 shows the effects of a series resistor on capacitive drive for varying voltage gains. As the closed-loop gain is increased, the larger phase margin allows for larger capacitive loads with less overshoot. Adding a series resistor at lower closed-loop gains accomplishes the same effect. For large capacitive loads, the frequency response of the amplifier will be dominated by the roll-off of the series resistor and capacitive load.

Figure 28. Driving Capacitive Loads

Figure 29. Capacitive Load Drive vs. Closed-Loop Gain

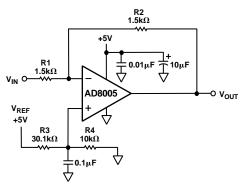

#### Single-Supply Level Shifter

In addition to providing buffering, many systems require that an op amp provide level shifting. A common example is the level shifting that is required to move a bipolar signal into the unipolar range of many modern analog-to-digital converters (ADCs). In general, single supply ADCs have input ranges that are referenced neither to ground nor supply. Instead the reference level is some point in between, usually halfway between ground and supply (+2.5 V for a single supply 5 V ADC). Because highspeed ADCs typically have input voltage ranges of 1 V to 2 V, the op amp driving it must be single supply but not necessarily rail-to-rail.

Figure 30. Bipolar to Unipolar Level Shifter

Figure 30 shows a level shifter circuit that can move a bipolar signal into a unipolar range. A positive reference voltage, derived from the +5 V supply, sets a bias level of +1.25 V at the noninverting terminal of the op amp. In ac applications, the accuracy of this voltage level is not important. Noise is however a serious consideration. A 0.1  $\mu$ F capacitor provides useful decoupling of this noise.

The bias level on the noninverting terminal sets the input commonmode voltage to +1.25 V. Because the output will always be positive, the op amp may therefore be powered with a single +5 V power supply.

The overall gain function is given by the equation:

$$V_{OUT} = -\left(\frac{R2}{R1}\right)V_{IN} + \left(\frac{R4}{R3 + R4}\right)\left(1 + \frac{R2}{R1}\right)V_{REF}$$

In the above example, the equation simplifies to

$$V_{OUT} = -V_{IN} + 2.5 V$$

### AD8005

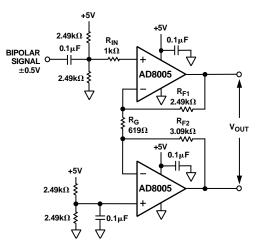

#### Single-Ended-to-Differential Conversion

Many single supply ADCs have differential inputs. In such cases, the ideal common-mode operating point is usually halfway between supply and ground. Figure 31 shows how to convert a single-ended bipolar signal into a differential signal with a common-mode level of 2.5 V.

Figure 31. Single-Ended-to-Differential Converter

Amp 1 has its +input driven with the ac-coupled input signal while the +input of Amp 2 is connected to a bias level of +2.5 V. Thus the –input of Amp 2 is driven to virtual +2.5 V by its output. Therefore, Amp 1 is configured for a noninverting gain of five,  $(1 + R_{F1}/R_G)$ , because RG is connected to the virtual +2.5 V of Amp 2's –input.

When the +input of Amp 1 is driven with a signal, the same signal appears at the –input of Amp 1. This signal serves as an input to Amp 2 configured for a gain of -5,  $(-R_{F2}/R_G)$ . Thus the two outputs move in opposite directions with the same gain and create a balanced differential signal.

This circuit can be simplified to create a bipolar in/bipolar out single-ended to differential converter. Obviously, a single supply is no longer adequate and the  $-V_S$  pins must now be powered with -5 V. The +input to Amp 2 is tied to ground. The ac coupling on the +input of Amp 1 is removed and the signal can be fed directly into Amp 1.

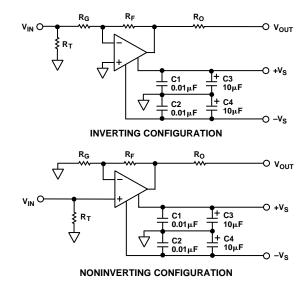

#### Layout Considerations

In order to achieve the specified high-speed performance of the AD8005 you must be attentive to board layout and component selection. Proper  $R_F$  design techniques and selection of components with low parasitics are necessary.

The PCB should have a ground plane that covers all unused portions of the component side of the board. This will provide a low impedance path for signals flowing to ground. The ground plane should be removed from the area under and around the chip (leave about 2 mm between the pin contacts and the ground plane). This helps to reduce stray capacitance. If both signal tracks and the ground plane are on the same side of the PCB, also leave a 2 mm gap between ground plane and track.

Figure 32. Inverting and Noninverting Configurations

Chip capacitors have low parasitic resistance and inductance and are suitable for supply bypassing (see Figure 32). Make sure that one end of the capacitor is within 1/8 inch of each power pin with the other end connected to the ground plane. An additional large (0.47  $\mu$ F–10  $\mu$ F) tantalum electrolytic capacitor should also be connected in parallel. This capacitor supplies current for fast, large signal changes at the output. It must not necessarily be as close to the power pin as the smaller capacitor.

Locate the feedback resistor close to the inverting input pin in order to keep the stray capacitance at this node to a minimum. Capacitance variations of less than 1.5 pF at the inverting input will significantly affect high-speed performance.

Use stripline design techniques for long signal traces (i.e., greater than about 1 inch). Striplines should have a characteristic impedance of either 50  $\Omega$  or 75  $\Omega$ . For the Stripline to be effective, correct termination at both ends of the line is necessary.

| Table I. | Typical Bandwidth vs | . Gain Setting Resistors |

|----------|----------------------|--------------------------|

|----------|----------------------|--------------------------|

| Gain | R <sub>F</sub> | R <sub>G</sub> | R <sub>T</sub> | Small Signal -3 dB<br>BW (MHz),<br>$V_S = \pm 5 V$ |

|------|----------------|----------------|----------------|----------------------------------------------------|

| -1   | 1.49 kΩ        | 1.49 kΩ        | 52.3           | 120 MHz                                            |

| -10  | 1 kΩ           | 100 Ω          | 100 Ω          | 60 MHz                                             |

| +1   | 2.49 kΩ        | œ              | 49.9 Ω         | 270 MHz                                            |

| +2   | 2.49 kΩ        | 2.49 kΩ        | 49.9 Ω         | 170 MHz                                            |

| +10  | 499 Ω          | 56.2 Ω         | 49.9 Ω         | 40 MHz                                             |

## AD8005

#### **Increasing Feedback Resistors**

Unlike conventional voltage feedback op amps, the choice of feedback resistor has a direct impact on the closed-loop bandwidth and stability of a current feedback op amp circuit. Reducing the resistance below the recommended value makes the amplifier more unstable. Increasing the size of the feedback resistor reduces the closed-loop bandwidth.

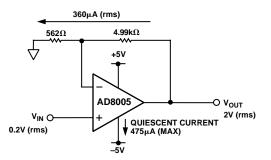

In power-critical applications where some bandwidth can be sacrificed, increasing the size of the feedback resistor will yield significant power savings. A good example of this is the gain of +10 case. Operating from a bipolar supply ( $\pm 5$  V), the quiescent current is 475  $\mu$ A (excluding the feedback network). The recommended feedback and gain resistors are 499  $\Omega$  and 56.2  $\Omega$  respectively. In order to drive an rms output voltage of 2 V, the output must deliver a current of 3.6 mA to the feedback network. Increasing the size of the resistor network by a factor of 10 as shown in Figure 33 will reduce this current to 360  $\mu$ A. The closed loop bandwidth will however decrease to 20 MHz.

Figure 33. Saving Power by Increasing Feedback Resistor Network

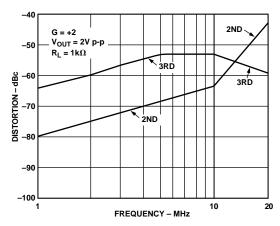

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).