## Quad 8-Bit, 65 MSPS Serial LVDS 3V A/D Converter

AD9289

## **Preliminary Technical Data**

### FEATURES

- Four ADCs in one package

- Serial LVDS digital output data rates up to 520 MHz (ANSI-644)

- Data clock output provided

- SNR = 47 dB (to Nyquist)

- Excellent Linearity:

- DNL =  $\pm 0.25$  LSB (Typical)

- $INL = \pm 0.5 LSB (Typical)$

- 400 MHz full power analog bandwidth

- Power dissipation = 330 mW at 65 MSPS

- 1 Vpp 2 Vpp input voltage range

- +3.0 V supply operation

- Power down mode

#### **APPLICATIONS**

- Tape drives

- Medical imaging

#### **PRODUCT DESCRIPTION**

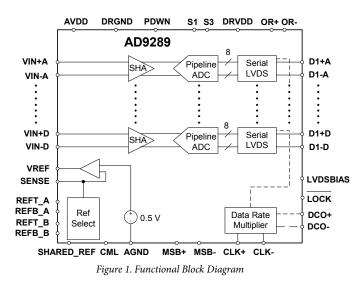

The AD9289 is a quad 8-bit, 65 MSPS analog-to-digital converter with an on-chip track-and-hold circuit and is designed for low cost, low power, small size and ease of use. The product operates up to 65 MSPS conversion rate and is optimized for outstanding dynamic performance where a small package size is critical.

The ADC requires a single+3V power supply and LVDS, TTL, or PECL-compatible sample rate clock for full performance operation. No external reference or driver components are required for many applications. A separate output power supply pin supports LVDS compatible serial digital output levels.

The ADC automatically multiplies up the sample rate clock for the appropriate LVDS serial data rate. An MSB trigger is provided to signal a new output byte. Power down is supported, and the ADC consumes less than 10mW when enabled.

Fabricated on an advanced CMOS process, the AD9289 is available in a 64-ball mini-BGA package (64 CSP\_BGA) specified over the industrial temperature range (–40°C to +85°C).

#### FUNCTIONAL BLOCK DIAGRAM

#### **PRODUCT HIGHLIGHTS**

- 1. Four analog-to-digital converters are contained in one small, space saving package.

- 2. A Data Clock Out (DCO) is provided which operates up to 260 MHz.

- 3. The outputs of each ADC are serialized and provided on the rising and falling edge of DCO (rising edge only is also an option). Output data rates up to 520 MHz (8 bits x 65 MSPS) are available.

- 4. The AD9289 operates from a single 3V power supply.

#### Rev. PrD 2/20/2003

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

# Preliminary Technical Data

## TABLE OF CONTENTS

| AD9289—Specifications  | 3 |

|------------------------|---|

| DIGITAL SPECIFICATIONS | 4 |

| AC SPECIFICATIONS      | 4 |

| SWITCHING SPECIFICATIONS   | 5 |

|----------------------------|---|

| EXPLANATION OF TEST LEVELS | 5 |

| Ordering Guide             | 6 |

## AD9289—SPECIFICATIONS<sup>1</sup>

### AVDD = 3.0V, DRVDD = 3.0V; EXT REF; DIFFERENTIAL ANALOG AND CLOCK INPUTS

| Parameter         |                                     | Temp | Test Level | Min | Тур        | Max | Unit   |

|-------------------|-------------------------------------|------|------------|-----|------------|-----|--------|

| RESOLUTION        |                                     |      |            |     | 8          |     | Bits   |

|                   | No Missing Codes                    | Full | VI         |     | Guaranteed |     |        |

|                   | Offset Matching                     | 25°C | I          |     | ± 25       |     | mV     |

|                   | Gain Matching <sup>2</sup>          | 25°C | I          |     | ± 2        |     | % FS   |

| ACCURACY          | Differential Nonlinearity (DNL)     | 25°C | I          |     | ± 0.25     |     | LSB    |

|                   |                                     | Full | VI         |     |            |     | LSB    |

|                   | Integral Nonlinearity (INL)         | 25°C | I          |     | ± 0.5      |     | LSB    |

|                   |                                     | Full | VI         |     |            |     | LSB    |

|                   | Offset Error                        | Full | V          |     | ± 16       |     | ppm/°C |

| TEMPERATURE DRIFT | Gain Error <sup>2</sup>             | Full | V          |     | ± 150      |     | ppm/°C |

|                   | Reference                           | Full | V          |     |            |     | ppm/°C |

| REFERENCE         | Internal Reference Voltage          | 25°C | I          |     | 0.5        |     | V      |

|                   | Output Current                      | Full | V          |     |            |     | uA     |

|                   | Input Current                       | Full | V          |     |            |     | uA     |

|                   | Input Resistance                    | Full | V          |     | 7          |     | kΩ     |

|                   | Differential Input Voltage Range    |      |            |     | 1 –2       |     | Vpp    |

|                   | Common Mode Voltage                 | Full | V          |     | 1.5        |     | V      |

| ANALOG INPUTS     | Input Resistance                    | Full | V          |     | tbd        |     | kΩ     |

|                   | Input Capacitance                   | Full | V          |     | 5          |     | pF     |

|                   | Analog Bandwidth, Full Power        | Full | V          |     | 400        |     | MHz    |

|                   | AVDD                                | Full | IV         | 2.7 | 3.0        | 3.6 | V      |

|                   | DRVDD                               | Full | IV         | 2.7 | 3.0        | 3.6 | V      |

| POWER SUPPLY      | Power Dissipation <sup>3</sup>      | Full | VI         |     | 330        |     | mW     |

|                   | Power Down Dissipation              | Full | VI         |     | <10        |     | mW     |

|                   | Power Supply Rejection Ratio (PSRR) | 25°C | I          |     |            |     | mV/V   |

|                   | IAVDD <sup>3</sup>                  | Full | VI         |     | 110        |     | mA     |

|                   | DRVDD <sup>3</sup>                  | Full | VI         |     | 27         |     | mA     |

| CROSSTALK         | Crosstalk                           | Full | V          |     | 70         |     | dB     |

Table 1

<sup>3</sup> Power dissipation measured with rated encode and a dc analog input (Outputs Static, Ivpp = 0.). Ivcc and Ivpp measured with TBD MHz analog input @ 0.5dBFS.

<sup>&</sup>lt;sup>1</sup> Specifications subject to change without notice <sup>2</sup> Gain error and gain temperature coefficients are based on the ADC only (with a fixed 0.5 V external reference and a 1 V p-p differential analog input).

### **DIGITAL SPECIFICATIONS**

#### AVDD = 3.0V, DRVDD = 3.0V

| Parameter                      |                                                | Temp | Test Level | Min    | Тур    | Max           | Unit |

|--------------------------------|------------------------------------------------|------|------------|--------|--------|---------------|------|

|                                | Differential Input                             | Full | IV         | 100    | 350    |               | mV   |

|                                | VIH                                            | Full | IV         |        |        |               | V    |

| DIGITAL INPUTS (CLK+,<br>CLK-) | VIL                                            | Full | IV         |        |        |               | V    |

| CLK-)                          | Input Resistance                               | Full | IV         |        |        |               | kΩ   |

|                                | Input Capacitance                              | 25°C | IV         |        |        |               | pF   |

| LOGIC INPUTS                   | Logic '1' Voltage                              | Full | IV         | 2.0    |        |               | V    |

|                                | Logic '0' Voltage                              | Full | IV         |        |        | 0.8           | V    |

|                                | Input Resistance                               | Full | IV         |        | 30     |               | kΩ   |

|                                | Input Capacitance                              | Full | IV         |        | 4      |               | PF   |

| DIGITAL OUTPUTS<br>(LVDS Mode) | Differential Output Voltage (V <sub>OD</sub> ) | Full | IV         | 247    |        | 454           | mV   |

|                                | Output Offset Voltage (Vos)                    | Full | IV         | 1.125  |        | 1.375         | V    |

|                                | Output Coding                                  | Full | IV         | Twos C | omplem | ent or Binary |      |

Table 2: Digital Specifications

### **AC SPECIFICATIONS<sup>1</sup>**

#### AVDD = 3.0 V, DRVDD = 3.0 V; INTERNAL REF; DIFFERENTIAL ANALOG AND CLOCK INPUT, LVDS OUTPUT MODE

| Parameter                          |                                         | Temp | Test Level | Min | Тур  | Max | Unit |

|------------------------------------|-----------------------------------------|------|------------|-----|------|-----|------|

|                                    | f <sub>IN</sub> = 10.3 MHz              | 25°C | V          |     | 47.5 |     | dB   |

| SIGNAL TO NOISE                    | f <sub>IN</sub> = 19.6 MHz              | 25°C | V          |     |      |     | dB   |

| RATIO (SNR) – Without<br>Harmonics | f <sub>IN</sub> = 32.5 MHz              | 25°C | I          |     | 47.5 |     | dB   |

|                                    | f <sub>IN</sub> = 51 MHz                | 25°C | V          |     |      |     | dB   |

|                                    | f <sub>IN</sub> = 10.3 MHz              | 25°C | V          |     | 47   |     | dB   |

| SIGNAL TO NOISE                    | f <sub>IN</sub> = 19.6 MHz              | 25°C | V          |     |      |     | dB   |

| RATIO (SINAD) – With<br>Harmonics  | f <sub>IN</sub> = 32.5 MHz              | 25°C | I          |     | 47   |     | dB   |

|                                    | f <sub>IN</sub> = 51 MHz                | 25°C | V          |     |      |     | dB   |

|                                    | f <sub>IN</sub> = 10.3 MHz              | 25°C | V          |     | 7.5  |     | Bits |

| EFFECTIVE NUMBER OF                | f <sub>IN</sub> = 19.6 MHz              | 25°C | V          |     |      |     | Bits |

| BITS (ENOB)                        | f <sub>IN</sub> = 32.5 MHz              | 25°C | I          |     | 7.5  |     | Bits |

|                                    | f <sub>IN</sub> = 51 MHz                | 25°C | V          |     |      |     | Bits |

|                                    | f <sub>IN</sub> = 10.3 MHz              | 25°C | V          |     | 62   |     | dB   |

| SPURIOUS FREE                      | f <sub>IN</sub> = 19.6 MHz              | 25°C | V          |     |      |     | dB   |

| DYNAMIC RANGE<br>(SFDR)            | f <sub>IN</sub> = 32.5 MHz              | 25°C | I          |     | 59   |     | dB   |

|                                    | f <sub>IN</sub> = 51 MHz                | 25°C | V          |     |      |     | dB   |

|                                    | f <sub>IN</sub> = 10.3 MHz              | 25°C | V          |     | 62   |     | dBc  |

| SECOND AND THIRD                   | f <sub>IN</sub> = 19.6 MHz              | 25°C | V          |     |      |     | dBc  |

| HARMONIC<br>DISTORTION             | f <sub>IN</sub> = 32.5 MHz              | 25°C | I          |     | 59   |     | dBc  |

|                                    | f <sub>IN</sub> = 51 MHz                | 25°C | V          |     |      |     | dBc  |

|                                    | f <sub>IN</sub> = 10.3 MHz              | 25°C | V          |     | 60   |     | dBc  |

| TOTAL HARMONIC                     | f <sub>IN</sub> = 19.6 MHz              | 25°C | V          |     |      |     | dBc  |

| DISTORTION (THD)                   | f <sub>IN</sub> = 32.5 MHz              | 25°C | I          |     | 58   |     | dBc  |

|                                    | f <sub>IN</sub> = 51 MHz                | 25°C | V          |     |      |     | dBc  |

| TWO TONE INTERMOD                  | $f_{IN1}$ = 19 MHz, $f_{IN2}$ = 20 MHz  | 25°C | V          |     |      |     | dBc  |

| DISTORTION (IMD)                   | $f_{IN1} = xx MHz$ , $f_{IN2} = xx MHz$ | 25°C | V          |     |      |     | dBc  |

Table 3: AC Specifications

<sup>1</sup> SNR/harmonics based on an analog input voltage of -0.5 dBFS referenced to a 1 Vpp full-scale input range.

### SWITCHING SPECIFICATIONS

#### AVDD = 3.0 V, DRVDD = 3.0 V; DIFFERENTIAL ENCODE INPUT

| Parameter                         |                                                        | Temp | Test Level | Min | Тур | Max | Unit   |

|-----------------------------------|--------------------------------------------------------|------|------------|-----|-----|-----|--------|

|                                   | Clock Rate                                             | Full | VI         | 65  |     |     | MSPS   |

| CLOCK                             | Clock Pulse Width High (t <sub>EH</sub> )              | Full | IV         | 6.9 |     |     | ns     |

|                                   | Clock Pulse Width Low (t <sub>EL</sub> )               | Full | IV         | 6.9 |     |     | ns     |

|                                   | Valid Time (t <sub>v</sub> ) <sup>1</sup>              | Full | VI         | 1.5 |     |     | ns     |

|                                   | Propagation Delay (t <sub>PD</sub> ) <sup>1</sup>      | Full | VI         |     | 3.5 |     | ns     |

| OUTPUT PARAMETERS<br>IN LVDS MODE | MSB Propagation Delay (t <sub>MSB</sub> ) <sup>1</sup> | Full | VI         |     |     |     | ns     |

|                                   | Rise Time (t <sub>R</sub> ) (20% to 80%)               | Full | V          |     | 0.7 |     | ns     |

|                                   | Fall Time (t <sub>F</sub> ) (20% to 80%)               | Full | V          |     | 0.7 |     | ns     |

|                                   | DCO Propagation Delay (t <sub>CPD</sub> )              | Full | VI         |     | 3   |     | ns     |

|                                   | Data to DCO Skew (t <sub>PD</sub> – t <sub>CPD</sub> ) | Full | IV         |     | 0.5 |     | ns     |

|                                   | Pipeline Latency                                       | Full | VI         |     | 6   |     | cycles |

| APERTURE                          | Aperture Delay (t <sub>A</sub> )                       | 25°C | V          |     |     |     | ps     |

|                                   | Aperture Uncertainty (Jitter)                          | 25°C | V          | 1   | <1  |     | ps rms |

Table 4: Switching Specifications

### **EXPLANATION OF TEST LEVELS**

#### TEST LEVEL

- I 100% production tested.

- II 100% production tested at +25°C and guaranteed by design and characterization at specified temperatures.

- III Sample Tested Only

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI 100% production tested at +25°C and guaranteed by design and characterization for industrial temperature range.

$<sup>^{1}</sup>$  t<sub>V</sub> and t<sub>PD</sub> are measured from the transition points of the CLK input to the 50%/50% levels of the digital outputs swing. The digital output load during test is not to exceed an ac load of 5 pF or a dc current of ±40  $\mu$ A. Rise and fall times measured from 20% to 80%.

## AD9289

### **OUTLINE DIMENSIONS**

Figure 2:

Figure 3:

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **Ordering Guide**

| Model      | Temperature Range        | Description      |

|------------|--------------------------|------------------|

| AD9289BBC  | -40°C to +85°C (Ambient) | 64 CSP_BGA       |

| AD9289/PCB | 25°C (Ambient)           | Evaluation Board |

Table 5: Ordering Guide

www.analog.com