# ANALOG DEVICES

# +2.5 V to +5.5 V, 25 MHz Low Power CMOS Complete DDS

# **Preliminary Technical Information**

## AD9833

#### FEATURES

+2.5 V to +5.5 V Power Supply 25 MHz Speed Serial Loading Sinusoidal/Triangular DAC Output Power-Down Option Narrowband SFDR > 72 dB 20 mW Power Consumption at 3 V 10-Pin mSOIC

APPLICATIONS Digital Modulation Portable Equipment Test Equipment DDS Tuning Clock rates up to 25 MHz are supported with a power supply from +2.5 V to +5.5 V. Frequency accuracy can be controlled to one part in 0.25 billion. Modulation is effected by loading registers through the serial interface. The digital section is internally operated at +2.5 V, irrespective of the value of VDD, by an on board regulator which steps down VDD to +2.5 V. The ROM can be bypassed so that a linear up/down ramp is output from the DAC. Also, if a clock output is required, the signal data bit can be output.

A power-down pin allows external control of a powerdown mode. In addition, sections of the device which are not being used can be powered down to minimise the current consumption. For example, the DAC can be powered down when the MSB is required. The part is available in a 10pin mSOIC package.

### **GENERAL DESCRIPTION**

This low power DDS device is a numerically controlled oscillator employing a phase accumulator, a sine lookup table and a D/A converter integrated on a single CMOS chip. Modulation capabilities are provided for phase modulation and frequency modulation.

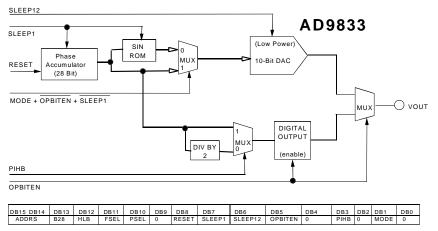

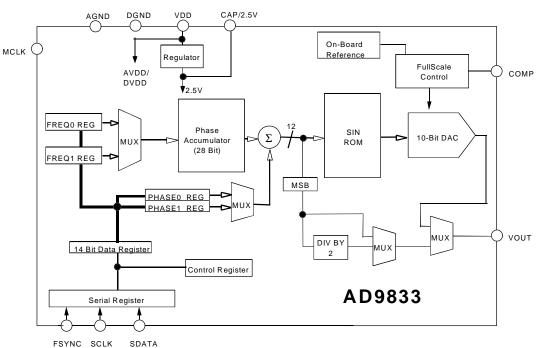

### FUNCTIONAL BLOCK DIAGRAM

#### REV PrE 04/01

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## AD9833

# SPECIFICATIONS<sup>1</sup>

## PRELIMINARY TECHNICAL DATA

$(V_{DD}$  = +2.5 V to +5.5 V; AGND = DGND = 0 V;  $T_A$  =  $T_{MIN}$  to  $T_{MAX};\,R_{SET}$  = 3.9 kW ;  $R_{LOAD}$  = 200W  $\,$  for VOUT unless otherwise noted)

| Parameter                             | AD9833B              | Units       | Test Conditions/Comments                        |

|---------------------------------------|----------------------|-------------|-------------------------------------------------|

| SIGNAL DAC SPECIFICATIONS             |                      |             |                                                 |

| Resolution                            | 10                   | Bits        |                                                 |

| Update Rate (f <sub>MAX</sub> )       | 25                   | MSPS max    |                                                 |

| I <sub>OUT</sub> Full Scale           | 3                    | mA max      |                                                 |

| Output Compliance                     | 1                    | V max       |                                                 |

| DC Accuracy                           | 1                    | v max       |                                                 |

| Integral Nonlinearity                 | ±1                   | LSB typ     |                                                 |

| Differential Nonlinearity             | $\pm 0.5$            | LSB typ     |                                                 |

| · · ·                                 | ±0.0                 | Lob typ     |                                                 |

| DDS SPECIFICATIONS                    |                      |             |                                                 |

| Dynamic Specifications                |                      |             |                                                 |

| Signal to Noise Ratio                 | 50                   | dB min      | $f_{MCLK} = f_{MAX}, f_{OUT} = 1.5 \text{ kHz}$ |

| Total Harmonic Distortion             | -53                  | dBc max     | $f_{MCLK} = f_{MAX}, f_{OUT} = 1.5 \text{ kHz}$ |

| Spurious Free Dynamic Range (SFDR)    |                      |             |                                                 |

| Wideband (± 2 MHz)                    | 50                   | dBc min     | $f_{MCLK} = f_{MAX}, f_{OUT} = f_{MCLK}/3$      |

|                                       | 55                   | dBc min     | $f_{MCLK} = f_{MAX}, f_{OUT} = 0.5 MHz$         |

| NarrowBand (± 50 kHz)                 | 72                   | dBc min     | $f_{MCLK} = f_{MAX}, f_{OUT} = f_{MCLK}/3$      |

|                                       | 75                   | dBc min     | $f_{MCLK} = f_{MAX}, f_{OUT} = 0.5 \text{ MHz}$ |

| Clock Feedthrough                     | -55                  | dBc typ     |                                                 |

| Wake Up Time                          | 1                    | ms typ      |                                                 |

| Power-Down Option                     | Yes                  |             |                                                 |

| VOLTAGE REFERENCE                     |                      |             |                                                 |

| Internal Reference @ +25°C            | 1.23                 | Volts typ   |                                                 |

| $T_{MIN}$ to $T_{MAX}$                | $1.23 \pm 7\%$       | Volts typ   |                                                 |

| REFIN Input Impedance                 | 10                   | Mw typ      |                                                 |

| Reference TC                          | 100                  | ppm/°C typ  |                                                 |

|                                       | 100                  | ppin/ C typ |                                                 |

| LOGIC INPUTS                          |                      |             |                                                 |

| V <sub>INH</sub> , Input High Voltage | V <sub>DD</sub> -0.9 | V min       | +3.6 V to +5.5 V Power Supply                   |

|                                       | VDD - 0.5            | V min       | +2.7 V to $+$ 3.6 V Power Supply                |

|                                       | 2                    | V min       | +2.5 V to $+2.7$ V Power Supply                 |

| V <sub>INL</sub> , Input Low Voltage  | 0.9                  | V max       | +3.6 V to +5.5 V Power Supply                   |

|                                       | 0.5                  | V max       | +2.5 V to $+$ 3.6 V Power Supply                |

| I <sub>INH</sub> , Input Current      | 10                   | µA max      |                                                 |

| C <sub>IN</sub> , Input Capacitance   | 10                   | pF max      |                                                 |

| POWER SUPPLIES                        |                      |             | $f_{OUT} = f_{MCLK}/3$                          |

| AVDD                                  | 2.5/5.5              | V min/V max | 100T - 1MCLK/3                                  |

| DVDD                                  | 2.5/5.5              | V min/V max |                                                 |

|                                       |                      |             |                                                 |

| I <sub>AA</sub>                       | 5<br>1 · 0.04/MHz    | mA max      |                                                 |

| $I_{DD}$                              | 1 + 0.04/MHz         | mA typ      | 2 V Dowon Supply                                |

| $I_{AA} + I_{DD}^2$                   | 7                    | mA typ      | 3 V Power Supply                                |

|                                       | 10                   | mA max      | F M Derror Come l                               |

|                                       | 10                   | mA typ      | 5 V Power Supply                                |

|                                       | 15                   | mA max      |                                                 |

| Low Power Sleep Mode                  | 0.25                 | mA typ      |                                                 |

NOTES

<sup>1</sup>Operating temperature range is as follows: B Version:  $-40^{\circ}$ C to  $+85^{\circ}$ C.

<sup>2</sup>Measured with the digital inputs static and equal to 0 V or DVDD.

Specifications subject to change without notice.

AD9833

## PRELIMINARY TECHNICAL INFORMATION

# TIMING CHARACTERISTICS ( $V_{DD}$ = +2.5 V to +5.5 V; AGND = DGND = 0 V, unless otherwise noted)

|                 | Limit at<br>T <sub>MIN</sub> to T <sub>MAX</sub> |        |                                       |

|-----------------|--------------------------------------------------|--------|---------------------------------------|

| Parameter       | (B Version)                                      | Units  | Test Conditions/Comments              |

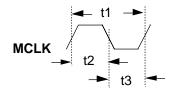

| t <sub>1</sub>  | 40                                               | ns min | MCLK Period                           |

| t <sub>2</sub>  | 16                                               | ns min | MCLK High Duration                    |

| t <sub>3</sub>  | 16                                               | ns min | MCLK Low Duration                     |

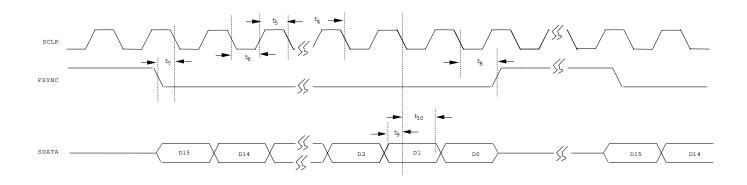

| t <sub>4</sub>  | 25                                               | ns min | SCLK Period                           |

| t <sub>5</sub>  | 10                                               | ns min | SCLK High Duration                    |

| t <sub>6</sub>  | 10                                               | ns min | SCLK Low Duration                     |

| t <sub>7</sub>  | 5                                                | ns min | FSYNC to SCLK Falling Edge Setup Time |

| t <sub>8</sub>  | 10                                               | ns min | FSYNC to SCLK Hold Time               |

|                 | SCLK - 5                                         | ns max |                                       |

| t <sub>9</sub>  | 5                                                | ns min | Data Setup Time                       |

| t <sub>10</sub> | 3                                                | ns min | Data Hold Time                        |

Guaranteed by design but not production tested.

Figure 2. Master Clock

Figure 3. Serial Timing

## AD9833

#### **ABSOLUTE MAXIMUM RATINGS\***

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| AVDD to AGND0.3 V to +7 V                          |

|----------------------------------------------------|

| DVDD to DGND0.3 V to +7 V                          |

| AVDD to DVDD                                       |

| AGND to DGND                                       |

| Digital I/O Voltage to DGND -0.3 V to DVDD + 0.3 V |

| Analog I/O Voltage to AGND -0.3 V to AVDD + 0.3 V  |

| Operating Temperature Range                        |

| Industrial (B Version)40°C to +85°C                |

| Storage Temperature Range65°C to +150°C            |

| Maximum Junction Temperature+150°C                 |

| mSOIC q <sub>JA</sub> Thermal Impedance158°C/W     |

| Lead Temperature, Soldering                        |

| Vapor Phase (60 sec)+215°C                         |

| Infrared (15 sec)+220°C                            |

| ESD Rating                                         |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**ORDERING GUIDE**

| Model     |                | Package<br>Description | Package<br>Option* |

|-----------|----------------|------------------------|--------------------|

| AD9833BRM | -40°C to +85°C | 10-Pin mSOIC           | RM-10              |

\*RM = Micro Small Outline IC (mSOIC).

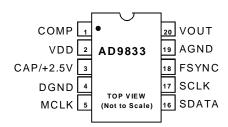

#### PIN CONFIGURATION

### PRELIMINARY TECHNICAL DATA

#### TERMINOLOGY

Integral Nonlinearity

This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale, a point 0.5 LSB below the first code transition  $(000\ldots00 \text{ to } 000\ldots01)$  and full scale, a point 0.5 LSB above the last code transition  $(111\ldots10 \text{ to } 111\ldots11)$ . The error is expressed in LSBs.

#### **Differential Nonlinearity**

This is the difference between the measured and ideal 1 LSB change between two adjacent codes in the DAC.

#### **Output Compliance**

The output compliance refers to the maximum voltage which can be generated at the output of the DAC to meet the specifications. When voltages greater than that specified for the output compliance are generated, the AD9833 may not meet the specifications listed in the data sheet.

#### **Spurious Free Dynamic Range**

Along with the frequency of interest, harmonics of the fundamental frequency and images of the MCLK frequency are present at the output of a DDS device. The spurious free dynamic range (SFDR) refers to the largest spur or harmonic which is present in the band of interest. The wide band SFDR gives the magnitude of the largest harmonic or spur relative to the magnitude of the fundamental frequency in the bandwidth

$\pm 2$  MHz about the fundamental frequency. The narrow band SFDR gives the attenuation of the largest spur or harmonic in a bandwidth of  $\pm 50$  kHz about the fundamental frequency.

#### **Clock Feedthrough**

There will be feedthrough from the MCLK input to the analog output. Clock feedthrough refers to the magnitude of the MCLK signal relative to the fundamental frequency in the AD9833's output spectrum.

## PRELIMINARY TECHNICAL INFORMATION

### **PIN DESCRIPTION**

| Pin Number    | Mnemonic    | Function                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| POWER SUPPLY  | ľ           |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| VDD           | 2           | Positive power supply for the analog section and the digital interface sections. The on board 2.5 V regulator is also supplied from VDD. A 0.1 $\mu$ F and 10 $\mu$ F decoupling capacitor should be connected between VDD and AGND. VDD can have a value from +2.5 V to +5.5 V.                                                                                                |  |  |

| AGND          | 9           | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| DGND          | 4           | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| CAP/2.5 v     | 3           | The digital circuitry operates from a +2.5 V power supply. This +2.5 V is generated from VDD using an on board regulator. The regulator requires a decoupling capacitor which is connected from CAP/2.5V to DGND. A 1 $\mu$ F and 0.1 mF capacitor should be connected from CAP/+2.5V to AGND. If the user has a power supply of 2.5V, CAP/2.5V should be tied directly to VDD. |  |  |

| ANALOG SIGNA  | L AND REFER | RENCE                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| VOUT          | 10          | Voltage Output. An on-chip resistor is connected between VOUT and AGND.                                                                                                                                                                                                                                                                                                         |  |  |

| СОМР          | 1           | Compensation pin. This is a compensation pin for the internal reference amplifier. A 10 nF typical decoupling ceramic capacitor should be connected between COMP and VDD.                                                                                                                                                                                                       |  |  |

| DIGITAL INTER | FACE AND CO | ONTROL                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| MCLK          | 5           | Digital Clock Input. DDS output frequencies are expressed as a binary fraction of the frequency of MCLK. The output frequency accuracy and phase noise are determined by this clock.                                                                                                                                                                                            |  |  |

| SCLK          | 7           | Serial Clock, Logic Input. Data is clocked into the AD9834 on each falling SCLK edge.                                                                                                                                                                                                                                                                                           |  |  |

| SDATA         | 6           | Serial Data In, Logic Input. The 16-bit serial data word is applied to this input.                                                                                                                                                                                                                                                                                              |  |  |

| FSYNC         | 8           | Data Synchronisation Signal, Logic Input. When this input is taken low, the internal logic is informed that a new word is being loaded into the device.                                                                                                                                                                                                                         |  |  |

| Register   | Size    | Description                                                                                                                      |

|------------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| FREQ0 REG  | 28 Bits | Frequency Register 0. This de-<br>fines the output frequency,<br>when $FSELECT = 0$ , as a frac-<br>tion of the MCLK frequency.  |

| FREQ1 REG  | 28 Bits | Frequency Register 1. This de-<br>fines the output frequency,<br>when $FSELECT = 1$ , as a frac-<br>tion of the MCLK frequency.  |

| PHASE0 REG | 12 Bits | Phase Offset Register 0. When $PSEL = 0$ , the contents of this register are added to the output of the phase accumulator.       |

| PHASE1 REG | 12 Bits | Phase Offset Register 1. When<br>PSEL = 1, the contents of this<br>register are added to the output<br>of the phase accumulator. |

#### Table I. Frequency/Phase Registers

Table 3. Phase Register Bits

| D15 | D14 | D13 | D12 | D11 |                    | D0  |

|-----|-----|-----|-----|-----|--------------------|-----|

| 1   | 1   | 0   | Х   | MSB | 12 PHASE0 REG BITS | LSB |

| 1   | 1   | 1   | Х   | MSB | 12 PHASE1 REG BITS | LSB |

### Table 4. Control Register

| D15 | D14 | D13          | D0 |

|-----|-----|--------------|----|

| 0   | 0   | CONTROL BITS |    |

#### Table 2. Frequency Register Bits

| D15 | D14 | D13 |                   | D0  |

|-----|-----|-----|-------------------|-----|

| 0   | 1   | MSB | 14 FREQ0 REG BITS | LSB |

| 1   | 0   | MSB | 14 FREQ1 REG BITS | LSB |

## **PRELIMINARY TECHNICAL DATA**

PRELIMINARY TECHNICAL DATA

### AD9833

| BitNameFunctionD13B28Two write operations are required to<br>load a new word into the FREQ regis-<br>ters. When B28 is set to 1, two con-<br>secutive writes to the same frequency<br>register are required to load the comp-<br>plete new 28-bit word into that regis-<br>ter. The first write to address 01 or 10<br>contains the 14 LSBs. of the frequency<br>word. The next write to this address<br>contains the 14 LSBs of the frequency<br>word. The next write to this address<br>contains the 14 LSBs of the frequency<br>word. The next write to this address<br>contains the 14 LSBs of the frequency<br>word. The next write to this address<br>contains the 14 LSBs of the frequency register oper-<br>ates as 2 registers. one containing the<br>14 LSBs and the other containing the<br>14 LSBs at the other containing the<br>14 LSBs at the other containing the<br>14 LSBs at the other containing the<br>the FREQ address while D12 of the<br>control register infroms the AD9833 is useful when<br>the FREQ address while D12 of the<br>control register infroms the AD9833 the VEC When this bit sevent is made to<br>the FREQ address while<br>the HLB bit indicates whether the 14 LSBs and vice<br>weresta. A singe write is made to<br>the frequency word can be altered in-<br>dependent of the 14 LSBs of the regus<br>ister. This allows the user to continu-<br>ously load the MSBs or LSBs while<br>ignoring the remaining 14 bits. This<br>is useful if the complete 28 bit resolu-<br>tion is not required. When HLB<br>equals 0, the BAE is avered to the 14 LSBs of the frequency register<br>are loaded.D4<br>PREVEN This is the SELECT bit.<br>D10 PSELD4<br>D8 RESETReserved<br>D11 FSELECT<br>This is the SELECT bit.<br>D10 PSEL<br>D11 FSELECTD11 is tress the phase accumulator<br>to zero which corresponds to an analog<br>output of midscale. The bit is set to 0.<br>D2 ReservedD2<br>D2 ReservedD4 <br< th=""><th>Т</th><th>Cable 5. Control Register Bits</th><th></th><th></th><th>to perform a reset. The accumulator</th></br<>                                                                                                                                                                       | Т                       | Cable 5. Control Register Bits                                                                                                                                                                                                                                                                                                                                   |    |          | to perform a reset. The accumulator                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>D13 B28 Iwo write operations are required to load a new word into the FREQ registers. When B28 is set to 1. two consecutive writes to the same frequency register are required to load the complete new 28-bit word into that register. The first write to address 01 or 10 contains the 14 LSBs of the frequency register operates as 2 registers, one containing the 14 LSBs, ro alter the 14 MSBs or 14 LSBs or the FREQ address while D12 of the control register informs the AD9833 whether the bits are MSBs or LSBs, while B28 is such 10 the HASBs or 14 LSBs or 0, the 14 MSBs or 14 LSBs or 0 the frequency word can be altered in dependent of the 14 LSBs and vice versa. A single write is made to the appropriate frequency address while the 14 bits being loaded are being transferred to the 14 MSBs or 14 LSBs of the reguest. When B28 is stet to 0, the 14 MSBs or 14 LSBs of the reguest or the 14 MSBs or 14 LSBs of the reguest. This allows the user to continuously load the MSBs of the frequency register. This allows the user to continuously load the MSBs of the frequency register. This allows the user to continuously load the MSBs of the frequency register. This is the PSEL bit. This bit resets the phase accumulator to pervent the phase information which results in a ramo output. When MODE is set to 1 and SLEEP1 and OPBITEN equal 0, the ROM is used to convert the phase information which results in a ramo output. The MSB is set to 1 and SLEEP1 and OPBITEN equal 0, the ROM is used to convert the phase information which results in a ramo output.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |                                                                                                                                                                                                                                                                                                                                                                  |    |          |                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>register are required to load the complete new 28-bit word into that register. The first write to address 01 or 10 contains the 14 LSBs of the frequency word. The next write to this address contains the 14 LSBs. To alter the 14 MSBs or the 14 LSBs and the other containing the 14 LSBs and the other control register informs the AD9833 whether the bits are MSBs or LSBs. When B28 is set to 0, the 14 MSBs or the frequency word can be altered in dependent of the 14 LSBs and vice versa. A single write is made to the appropriate frequency address while bits being loaded are being transferred to the 14 MSBs or the 14 MSBs of the reguency register. This allows the user to continuously load the MSBs or 14 LSBs of the frequency register are loaded.</li> <li>D11 FSELECT This is the FSELECT bit. D10 PSEL</li> <li>D11 FSELECT This is the FSELECT This is the FSELECT This bit such a first the FSELECT This bit should be set to 0. This bit must be set to 0. This bit must be set to 0. This bit should be set to 0. This bit must be set to 0. This bit should be set to 0. This bit must be set to 0. This bit must</li></ul>                                                                                                                 | D13 B28                 | load a new word into the FREQ regis-<br>ters. When B28 is set to 1, two con-                                                                                                                                                                                                                                                                                     | D7 | SLEEP1   | When this bit is set to 1, the internal clock is disabled. The DAC output will remain at its present value as the                                                                                                                                                                                                                                                         |

| <ul> <li>b) the frequency word. The next write to this address contains the 14 MSBs. When B28 is set to 0, the frequency register operates as 2 registers, one containing the 14 MSBs and the other containing the 14 LSBs. To alter the 14 MSBs or the 14 LSBs, a single write is made to the frequency word can be altered in dependent of the 14 LSBs and vice versa. A single write is made to the frequency word can be altered in dependent of the 14 LSBs of the frequency word can be altered in dependent of the 14 LSBs and vice versa. A single write is made to the 4MSBs or 14 LSBs and vice versa. A single write is made to the 4MSBs or 14 LSBs and vice versa. A single write is made to the 14 MSBs or 14 LSBs of the frequency word can be altered in dependent of the 14 LSBs of the register. This allows the user to continuously load the MSBs or LSBs while ignoring the remaining 14 bits. This is useful if the complete 28 bit resolution is not required. When HLB equals 0, the 14 LSBs of the frequency register. When HLB equals 0, the 14 LSBs of the frequency register. When HLB equals 0, the 14 LSBs of the frequency register. When HLB equals 0, the 14 LSBs of the frequency register. When HLB equals 0, the SIB is passed directly to the output.</li> <li>D11 FSELECT This is the FSELE Dtit.</li> <li>D10 PSEL This bit should be set to 0.</li> <li>D11 FSELECT This is the orgen to continuo output of midscale. The bit is set to 1</li> <li>D11 FSELECT This is the orgen to continuo to zero which corresponds to an analog output of midscale. The bit is set to 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | register are required to load the com-<br>plete new 28-bit word into that regis-<br>ter. The first write to address 01 or 10                                                                                                                                                                                                                                     | D6 | SLEEP12  | When this bit equals 1, the DAC is powered down. This is useful when                                                                                                                                                                                                                                                                                                      |

| <ul> <li>D12 HLB</li> <li>D12 HLB</li> <li>When B28 is set to 0, the 14 MSBs of the frequency word can be altered in-dependent of the 14 LSBs and vice versa. A single write is made to the appropriate frequency address while the HLB bit indicates whether the 14 bits being loaded are being transferred to the 14 MSBs or 14 LSBs of the register. This allows the user to continuously load the MSBs or LSBs while ignoring the remaining 14 bits. This is useful if the complete 28 bit resolution is not required. When HLB equals 0, the 14 LSBs of the frequency register are loaded.</li> <li>D11 FSELECT D11 FSELECT D11 FSELECT This is the FSELECT bit. TD10 PSEL D9 Reserved D1 RESET</li> <li>D11 FSELECT This bit should be set to 0.</li> <li>D11 FSELECT This is the FSELECT bit. TD10 PSEL D9 Reserved This bit resets the phase accumulator to zero which corresponds to an analog output of midscale. The bit is set to 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         | word. The next write to this address<br>contains the 14 MSBs. When B28 is<br>set to 0, the frequency register oper-<br>ates as 2 registers, one containing the<br>14 MSBs and the other containing the<br>14 LSBs. To alter the 14 MSBs or<br>the 14 LSBs, a single write is made to<br>the FREQ address while D12 of the<br>control register informs the AD9833 | D5 | OPBITEN  | NCO's MSB only. In this case, the<br>DAC is not required so, it can be<br>powered down to reduce the power<br>consumption.<br>When this bit is set to 1, the MSB<br>from the phase accumulator is routed<br>to pin VOUT. It can be sent directly<br>to the pin or, it can be divided by 2<br>prior to being output. Bit PIHB de-<br>termines whether the square wave gen- |

| <ul> <li>the HLB bit indicates whether the 14<br/>bits being loaded are being transferred<br/>to the 14 MSBs or 14 LSBs of the reg-<br/>ister. This allows the user to continu-<br/>ously load the MSBs or LSBs while<br/>ignoring the remaining 14 bits. This<br/>is useful if the complete 28 bit resolu-<br/>tion is not required. When HLB<br/>equals 1, the 14 bits of data are trans-<br/>ferred into the 14 MSBs of the fre-<br/>quency register. When HLB equals 0,<br/>the 14 LSBs of the frequency register<br/>are loaded.</li> <li>D11 FSELECT<br/>D10 PSEL<br/>D1 RESET</li> <li>D11 FSELECT<br/>D10 PSEL<br/>D3 RESET</li> <li>D11 FSELECT<br/>D3 RESET</li> <li>D11 FSELECT<br/>D3 RESET</li> <li>D12 Reserved<br/>D4 MCDE</li> <li>D2 Reserved<br/>D5 MITB</li> <li>D2 Reserved<br/>D1 MODE</li> <li>D3 MODE</li> <li>D4 MODE is set to 0.<br/>When MODE is set to 0.<br/>When MODE is set to 1</li> <li>D4 MODE is set to 1</li> <li>D5 MITB</li> <li>D2 Reserved<br/>D1 MODE</li> <li>D4 MODE</li> <li>D4 MODE is set to 1</li> <li>D5 MITB</li> <li>D5 MITB</li> <li>D5 MITB</li> <li>D6 Mits Used in association with<br/>OPBITEN. equals</li> <li>D1 MODE</li> <li>D2 Reserved<br/>D1 MODE</li> <li>D3 MODE</li> <li>D4 MODE is set to 0.<br/>When MODE is set to 1</li> <li>D4 MODE is set to 1</li> <li>D5 MITB</li> <li>D4 MODE</li> <li>D5 MITB</li> <li>D5 MITB&lt;</li></ul> | D12 HLB                 | the frequency word can be altered in-<br>dependent of the 14 LSBs and vice<br>versa. A single write is made to the                                                                                                                                                                                                                                               |    |          | before being output. When<br>OPBITEN equals 0, the DAC is con-<br>nected to VOUT.<br>This bit must be set to 0.                                                                                                                                                                                                                                                           |

| <ul> <li>tion is not required. When HLB equals 1, the 14 bits of data are transferred into the 14 MSBs of the frequency register. When HLB equals 0, the 14 LSBs of the frequency register are loaded.</li> <li>D11 FSELECT This is the FSELECT bit.</li> <li>D9 Reserved D1 RESET This bit should be set to 0.</li> <li>D8 RESET This bit resets the phase accumulator to zero which corresponds to an analog output of midscale. The bit is set to 1</li> <li>D2 Reserved D1 MODE</li> <li>D2 Reserved D1 MODE</li> <li>D3 RESET This bit should be set to 0.</li> <li>D4 RESET This bit resets the phase accumulator to zero which corresponds to an analog output of midscale. The bit is set to 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         | the HLB bit indicates whether the 14<br>bits being loaded are being transferred<br>to the 14 MSBs or 14 LSBs of the reg-<br>ister. This allows the user to continu-<br>ously load the MSBs or LSBs while<br>ignoring the remaining 14 bits. This                                                                                                                 | D3 | PIHB     | OPBITEN. When OPBITEN equals<br>1, the MSB is output on pin VOUT to<br>generate a square wave. When PIHB<br>equals 0, the square wave is divided by<br>2 before being output. When PIHB<br>equals 1, the MSB is passed directly to                                                                                                                                        |

| D11 FSELECTThis is the FSELECT bit.output.D10 PSELThis is the PSEL bit.output.D9 ReservedThis bit should be set to 0.SLEEP1 and OPBITEN equal 0, the<br>ROM is bypassed and the phase<br>information from the phase<br>accumulator is sent directly to the<br>DAC which results in a ramp output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         | tion is not required. When HLB<br>equals 1, the 14 bits of data are trans-<br>ferred into the 14 MSBs of the fre-<br>quency register. When HLB equals 0,<br>the 14 LSBs of the frequency register<br>are loaded.                                                                                                                                                 |    |          | This bit must be set to 0.<br>When MODE is set to 0 and SLEEP1<br>and OPBITEN equal 0, the ROM is<br>used to convert the phase information<br>into amplitude information which                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D10 PSEL<br>D9 Reserved | This is the PSEL bit.<br>This bit should be set to 0.<br>This bit resets the phase accumulator<br>to zero which corresponds to an analog                                                                                                                                                                                                                         |    |          | output. When MODE is set to 1 and<br>SLEEP1 and OPBITEN equal 0, the<br>ROM is bypassed and the phase<br>information from the phase<br>accumulator is sent directly to the                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |                                                                                                                                                                                                                                                                                                                                                                  | D0 | Reserved |                                                                                                                                                                                                                                                                                                                                                                           |