# ADS7833

# 10-Channel, 12-Bit DATA ACQUISITION SYSTEM

## FEATURES

- 3 SIMULTANEOUS SAMPLED CHANNELS

- 3 SYNCHRONIZED 12-BIT ADCs

- 6.6µs THROUGHPUT RATE

- FULLY DIFFERENTIAL MUX INPUTS

- DIGITALLY SELECTABLE INPUT RANGES

- ±5V POWER SUPPLIES

- SERIAL DIGITAL INPUT/OUTPUTS

- 2 SIMULTANEOUS SAMPLED AUXILIARY CHANNELS

- DIRECT INTERFACE TO MOTOROLA'S DSP56004/7

# DESCRIPTION

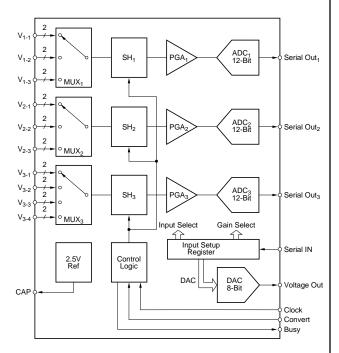

The ADS7833 consists of three 12-bit analog-to-digital converters preceded by three simultaneously operating sample-hold amplifiers, and multiplexers for 10 differential inputs. The ADCs have simultaneous serial outputs for high speed data transfer and data processing.

The ADS7833 also offers a programmable gain amplifier with programmable gains of 1.0V/V, 1.25V/V, 2.5V/V, and 5.0V/V. Channel selection and gain selection are selectable through the serial input control word. The high through put rate is maintained by simultaneously clocking in the 13-bit input control word for the next conversion while the present conversions are clocked out.

The part also contains an 8-bit digital-to-analog converter whose digital input is supplied as part of the input control word.

## APPLICATIONS

- AC MOTOR SPEED CONTROLS

- THREE PHASE POWER CONTROL

- UNINTERRUPTABLE POWER SUPPLIES

- VIBRATION ANALYSIS

- PC DATA ACQUISITION

- MEDICAL INSTRUMENTATION

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1994 Burr-Brown Corporation

## **SPECIFICATIONS**

At  $V_{ANA+} = +5V$ ,  $V_{ANA-} = -5V$ ,  $V_{DIG+} = +5V$ ,  $V_{DIG-} = -5V$ , and  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , using internal reference,  $f_{CLOCK} = 2.1 MHz$ .

## ANALOG-TO-DIGITAL CONVERTER CHANNELS

|                                                                                                                                                                                                                                                                                   |                                                                                        |           | ADS7833N                                             |                                  |                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------|------------------------------------------------------|----------------------------------|------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                         | CONDITIONS                                                                             | MIN       | ТҮР                                                  | МАХ                              | UNITS                                                      |

| RESOLUTION                                                                                                                                                                                                                                                                        |                                                                                        | 12        |                                                      |                                  | Bit                                                        |

| ANALOG INPUT<br>Full Scale Voltage, Differential                                                                                                                                                                                                                                  | G = 1.0V/V<br>G = 1.25V/V<br>G = 2.5V/V<br>G = 5.0V/V                                  | 10.5      | ±2.5<br>±2.0<br>±1.0<br>±0.5                         |                                  |                                                            |

| Common-Mode Voltage<br>Impedance<br>Capacitance                                                                                                                                                                                                                                   |                                                                                        | ±0.5      | See Table VII<br>10 <sup>12</sup><br>20              |                                  | V<br>Ω<br>pF                                               |

| THROUGHPUT SPEED                                                                                                                                                                                                                                                                  |                                                                                        |           |                                                      |                                  |                                                            |

| Conversion Time<br>Complete Cycle<br>Throughput Rate                                                                                                                                                                                                                              | CLK = 2.1MHz<br>Acquire and Convert                                                    | 150       | 200                                                  | 6.1<br>6.6                       | μs<br>μs<br>kHz                                            |

| SAMPLING DYNAMICS<br>S/H Droop Rate<br>S/H Acquisition Time<br>S/H Aperture Delay<br>S/H Aperture Jitter<br>Sampling Skew, Channel-to-Channel                                                                                                                                     |                                                                                        |           | 0.1<br>0.5<br>50<br>50<br>3                          |                                  | μV/μs<br>μs<br>ns<br>ps<br>ns                              |

| DC ACCURACY<br>Integral Linearity - ADC<br>Differential Linearity - ADC<br>No Missing Codes<br>Integral Linearity - Asynchronous, Synchronous<br>Differential Linearity - Asynchronous, Synchronous<br>Full Scale Error<br>Full Scale Error Other Gains<br>Full Scale Error Drift | G = 1.0V/V<br>G = 1.0V/V                                                               | 12        | ±0.5<br>±0.5<br>0.5<br>0.5<br>±10                    | ±2<br>±3<br>±3<br>2<br>4<br>±100 | LSB<br>LSB<br>LSB<br>LSB<br>% of FSR<br>% of FSR<br>ppm/°C |

| Zero Error - ADC<br>Zero Error - Asynchronous, Synchronous<br>Zero Error Drift                                                                                                                                                                                                    | G = 2.5V/V<br>G = 1.0V/V<br>G = 1.0V/V<br>G = 1.0V/V                                   |           | $\pm 10 \\ \pm 0.5 \\ \pm 0.5 \\ \pm 0.5 \\ \pm 0.5$ | ±100<br>±15<br>±20               | ppm/°C<br>LSB<br>LSB<br>ppm/°C                             |

| AC ACCURACY<br>Total Harmonic Distortion<br>$f_{IN} = 1 \text{kHz}$<br>$f_{IN} = 1 \text{MHz}$<br>CMR                                                                                                                                                                             | V <sub>CM</sub> = 1V, f <sub>CM</sub> = 1MHz                                           |           | 92<br>72<br>40                                       |                                  | dB<br>dB<br>dB                                             |

| REFERENCE<br>Internal Reference Voltage<br>Internal Reference Accuracy<br>Internal Reference Drift<br>Internal Reference Source Current<br>External Reference Voltage Range<br>for Specified Linearity<br>External Reference Current Drain                                        |                                                                                        | 2.25      | 2.5<br>±0.25<br>±10<br>10<br>2.5                     | 2.75                             | ∨<br>%<br>ppm/°C<br>μΑ<br>∨<br>μΑ                          |

| DIGITAL INPUTS<br>Logic Levels<br>V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub>                                                                                                                                                                        |                                                                                        | 0<br>+3.5 |                                                      | 1.5<br>+5<br>±10<br>±10          | V<br>V<br>μΑ<br>μΑ                                         |

| Input Capacitance DIGITAL OUTPUTS Data Format Data Coding                                                                                                                                                                                                                         | At All Digital Input Pins                                                              |           | 12-Bit Serial<br>BTC                                 | 15                               | pF                                                         |

| V <sub>OL</sub><br>V <sub>OH</sub><br>Leakage Current<br>Output Capacitance                                                                                                                                                                                                       | I <sub>SINK</sub> = 1.6mA<br>I <sub>SOURCE</sub> = 500μA<br>At All Digital Output Pins | 0<br>4.2  |                                                      | 0.4<br>5<br>±5<br>15             | V<br>V<br>μΑ<br>pF                                         |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **SPECIFICATIONS** (CONT)

At  $V_{ANA+} = +5V$ ,  $V_{ANA-} = -5V$ ,  $V_{DIG+} = +5V$ ,  $V_{DIG-} = -5V$ , and  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , using internal reference,  $f_{CLOCK} = 2.1MHz$ .

## ANALOG-TO-DIGITAL CONVERTER CHANNELS

|                       |                       | ADS7833N |      |       |       |

|-----------------------|-----------------------|----------|------|-------|-------|

| PARAMETER             | CONDITIONS            | MIN      | ТҮР  | МАХ   | UNITS |

| POWER SUPPLIES        | Specified Performance |          |      |       |       |

| V <sub>ANA+</sub>     |                       | +4.75    | +5.0 | +5.25 | V     |

| V <sub>ANA-</sub>     |                       | -4.75    | -5.0 | -5.25 | V     |

| V <sub>DIG+</sub>     |                       | +4.75    | +5.0 | +5.25 | V     |

| V <sub>DIG-</sub>     |                       | -4.75    | -5.0 | -5.25 | V     |

| I <sub>ANA+</sub>     |                       |          | 15   | 25    | mA    |

| I <sub>ANA</sub>      |                       |          | 8    | 10    | mA    |

| I <sub>DIG+</sub>     |                       |          | 3    | 5     | mA    |

| I <sub>DIG</sub> _    |                       |          | 1    | 2     | mA    |

| Power Dissipation     |                       |          | 125  |       | mW    |

| TEMPERATURE RANGE     |                       |          |      |       |       |

| Specified Performance |                       | -40      |      | +85   | °C    |

| Derated Performance   |                       | -55      |      | +125  | °C    |

| Storage               |                       | -65      |      | +150  | °C    |

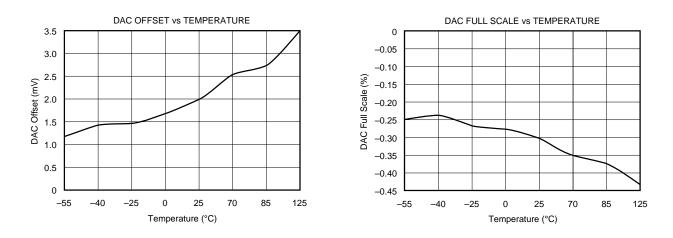

### DIGITAL-TO-ANALOG CONVERTER

|                        |            |        | ADS7833N |      |       |

|------------------------|------------|--------|----------|------|-------|

| PARAMETER              | CONDITIONS | MIN    | ТҮР      | МАХ  | UNITS |

| RESOLUTION             |            | 8-Bits |          |      |       |

| Output Range           |            | 0      |          | +2.5 | V     |

| Output Settling Time   | To 0.5LSB  |        |          | 1    | μs    |

| Linearity Error        |            |        |          | ±1   | LSB   |

| Differential Linearity |            |        |          | ±1   | LSB   |

| Output Current         |            | 200    |          |      | μA    |

| Offset Error           |            |        | ±1       | 10   | mV    |

| Full Scale Error       |            |        |          | 2    | %     |

## **ABSOLUTE MAXIMUM RATINGS**

| Analog Input Voltage ±25V                      |

|------------------------------------------------|

| Ground Voltage Difference: AGND and DGND ±0.3V |

| Power Supply Voltages:                         |

| V <sub>ANA+</sub> +7V                          |

| V <sub>ANA-</sub>                              |

| V <sub>DIG+</sub> +7V                          |

| V <sub>DIG</sub> 7V                            |

| Digital Inputs0.3V to V <sub>DIG</sub> +0.3V   |

| Maximum Junction Temperature+165°C             |

| Internal Power Dissipation 825mW               |

| Lead Temperature (soldering, 10s) +300°C       |

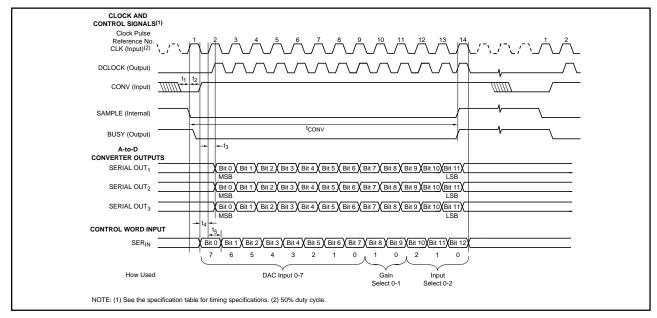

## **CONVERSION AND DATA TIMING**

| SYMBOL            | DESCRIPTION                                              | MIN | TYP | MAX | UNITS |

|-------------------|----------------------------------------------------------|-----|-----|-----|-------|

| t <sub>CONV</sub> | A/D Conversion Time                                      | 6.6 | 4.0 |     | μs    |

| CLK               | A/D Conversion Clock                                     | 2.1 | 2.8 |     | MHz   |

| t <sub>1</sub>    | Setup Time for Conversion<br>Before Rising Edge of Clock | 50  |     |     | ns    |

| t <sub>2</sub>    | Hold Time for Conversion<br>After Rising Edge of Clock   | 50  |     |     | ns    |

| t <sub>3</sub>    | Setup Time for Serial Out                                |     |     | 25  | ns    |

| t <sub>4</sub>    | Setup Time for Serial Input                              | 30  |     |     | ns    |

| t <sub>5</sub>    | Hold Time for Serial Input                               | 30  |     |     | ns    |

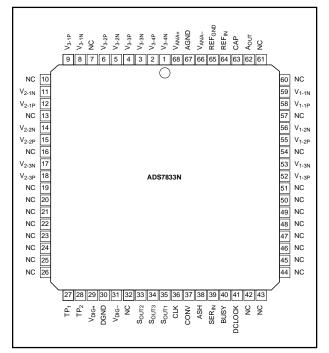

## PACKAGE INFORMATION

| PRODUCT  | PACKAGE      | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------|------------------------------------------|

| ADS7833N | 68-Lead PLCC | 312                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

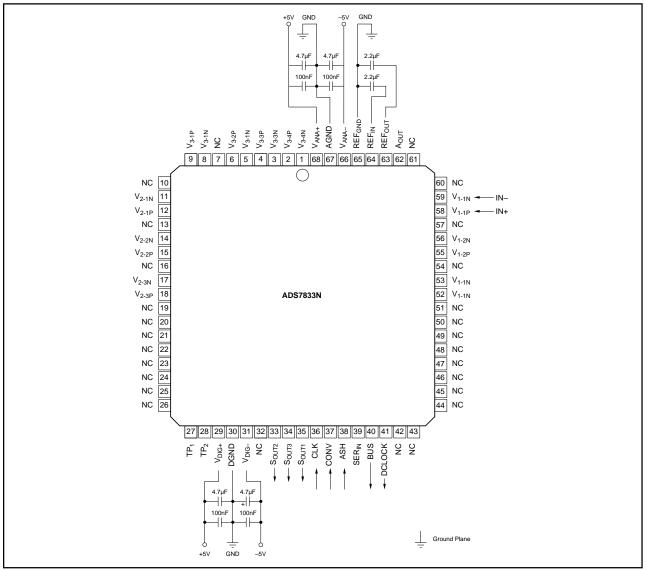

## **PIN CONFIGURATION**

## **PIN DEFINITIONS**

| PIN NO   | NAME                                   | TYPE <sup>(1)</sup> | DESCRIPTION                                                          | PIN NO | NAME               | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                |

|----------|----------------------------------------|---------------------|----------------------------------------------------------------------|--------|--------------------|---------------------|------------------------------------------------------------------------------------------------------------|

| 1        | V <sub>3-4N</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 4,                                 | 35     | S <sub>OUT1</sub>  | DO                  | Serial Digital Output, Channel 1                                                                           |

|          |                                        |                     | Negative Side                                                        | 36     | CLK                | DI                  | Clock for A/D Converters                                                                                   |

| 2        | V <sub>3-4P</sub>                      | AI                  | Voltage Input, Channel 3, Mux IP 4,<br>Positive Side                 | 37     | CONV               | DI                  | Start A/D Converters. When CONV goes to<br>"0" (low) the next rising edge of CLK<br>starts the conversion. |

| 3        | V <sub>3–3N</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 3,<br>Negative Side                | 38     | ASH                | DI                  | Digital Control for Asynchronous Sample<br>Hold. If signal is "1" (high), signals                          |

| 4        | V <sub>3–3P</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 3,<br>Positive Side                | 39     | SER <sub>IN</sub>  | DI                  | are sampled.<br>Serial Digital Input for Input Control Word                                                |

| 5        | V <sub>3-2N</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 2,<br>Negative Side                | 40     | BUSY               | DO                  | A/D Converters Busy. Busy if signal<br>is "0" (low).                                                       |

| 6        | V <sub>3-2P</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 2,<br>Positive Side                | 41     | DCLOCK             | DO                  | A Delayed and Truncated Version of the CLK Signals. It is Delayed 50ns                                     |

| 7        | NC                                     | —                   | No Connection                                                        |        |                    |                     | from the CLK Signal and Stays Low                                                                          |

| 8        | V <sub>3-1N</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 1,                                 |        |                    |                     | after 13 DCLOCK Cycles.                                                                                    |

|          |                                        |                     | Negative Side                                                        | 42     | NC                 | _                   | No Connection                                                                                              |

| 9        | V <sub>3–1P</sub>                      | AI                  | Voltage Input, Channel 3, Mux I/P 1,                                 | 43     | NC                 | _                   | No Connection                                                                                              |

|          |                                        |                     | Positive Side                                                        | 44     | NC                 | _                   | No Connection                                                                                              |

| 10       | NC                                     | _                   | No Connection                                                        | 45     | NC                 | _                   | No Connection                                                                                              |

| 11       | V <sub>2-1N</sub>                      | AI                  | Voltage Input, Channel 2, Mux I/P 1,                                 | 46     | NC                 | _                   | No Connection                                                                                              |

|          | 2 114                                  |                     | Negative Side                                                        | 47     | NC                 | _                   | No Connection                                                                                              |

| 12       | V <sub>2–1P</sub>                      | AI                  | Voltage Input, Channel 2, Mux I/P 1,                                 | 48     | NC                 | _                   | No Connection                                                                                              |

|          | • 2–1P                                 |                     | Positive Side                                                        | 49     | NC                 | _                   | No Connection                                                                                              |

| 13       | NC                                     |                     | No Connection                                                        | 50     | NC                 | _                   | No Connection                                                                                              |

| 13       | -                                      | AI                  | Voltage Input, Channel 2, Mux I/P 2,                                 | 51     | NC                 | _                   | No Connection                                                                                              |

|          | V <sub>2-2N</sub>                      |                     | Negative Side                                                        | 52     | V <sub>1-3P</sub>  | AI                  | Voltage Input, Channel 1, Mux I/P 3,<br>Positive Side                                                      |

| 15       | V <sub>2-2P</sub>                      | AI                  | Voltage Input, Channel 2, Mux I/P 2,<br>Positive Side                | 53     | V <sub>1-3N</sub>  | AI                  | Voltage Input, Channel 1, Mux I/P 3,<br>Negative Side                                                      |

| 16       | NC                                     | —                   | No Connection                                                        | 54     | NC                 |                     | No Connection                                                                                              |

| 17       | V <sub>2-3N</sub>                      | AI                  | Voltage Input, Channel 2, Mux I/P 3,<br>Negative Side.               | 55     | V <sub>1-2P</sub>  | AI                  | Voltage Input, Channel 1, Mux I/P 2,<br>Positive Side                                                      |

| 18       | V <sub>2-3P</sub>                      | AI                  | Voltage Input, Channel 2, Mux I/P 3,<br>Positive Side                | 56     | V <sub>1-2N</sub>  | AI                  | Voltage Input, Channel 1, Mux I/P 2,<br>Negative Side                                                      |

| 19       | NC                                     | _                   | No Connection                                                        |        |                    |                     |                                                                                                            |

| 20       | NC                                     |                     | No Connection                                                        | 57     | NC                 |                     | No Connection                                                                                              |

| 21       | NC                                     | _                   | No Connection                                                        | 58     | V <sub>1–1P</sub>  | AI                  | Voltage Input, Channel 1, Mux I/P 1,<br>Positive Side                                                      |

| 22       | NC                                     | _                   | No Connection                                                        |        |                    |                     |                                                                                                            |

| 23       | NC                                     | _                   | No Connection                                                        | 59     | V <sub>1-1N</sub>  | AI                  | Voltage Input, Channel 1, Mux I/P 1,                                                                       |

| 24       | NC                                     | —                   | No Connection                                                        |        |                    |                     | Negative Side                                                                                              |

| 25       | NC                                     | _                   | No Connection                                                        | 60     | NC                 | -                   | No Connection                                                                                              |

| 26       | NC                                     | _                   | No Connection                                                        | 61     | NC                 | -                   | No Connection                                                                                              |

| 27       | TP1                                    | —                   | Test Point 1, Make No Connection                                     | 62     | A <sub>OUT</sub>   | AO                  | Output of DAC                                                                                              |

| 28       | TP2                                    | —                   | Test Point 2, Make No Connection                                     | 63     | CAP                | AO                  | Decoupling Point for Internal Reference                                                                    |

| 29       | V <sub>DIG+</sub>                      | Р                   | Digital Supply Voltage, +5V                                          | 64     | REFIN              | AI                  | Input Pin for External Reference                                                                           |

| 30       | DGND                                   | Р                   | Digital Supply Voltage, Ground                                       | 65     | REF <sub>GND</sub> | Р                   | Ground Pin for External Reference                                                                          |

| 31       | V <sub>DIG</sub> _                     | Р                   | Digital Supply Voltage, -5V                                          | 66     | V <sub>ANA-</sub>  | Р                   | Analog Supply Voltage, -5V                                                                                 |

| 32       | NC                                     | -                   | No Connection                                                        | 67     | AGND               | Р                   | Analog Supply Voltage, Ground                                                                              |

| 33<br>34 | S <sub>OUT2</sub><br>S <sub>OUT3</sub> | DO<br>DO            | Serial Digital Output, Channel 2<br>Serial Digital Output, Channel 3 | 68     | V <sub>ANA+</sub>  | Р                   | Analog Supply Voltage, +5V                                                                                 |

NOTE: (1) AI is Analog Input, AO is Analog Output, DI is Digital Input, DO is Digital Output, P is Power Supply Connection.

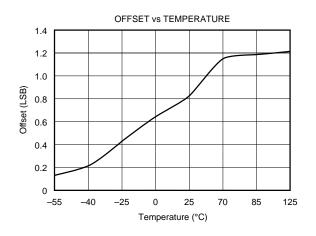

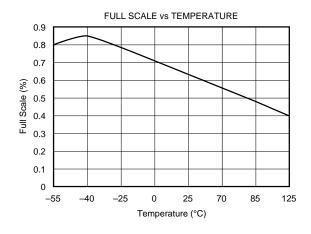

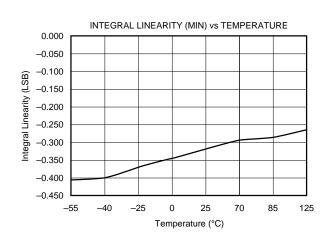

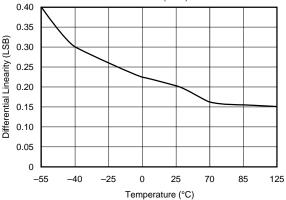

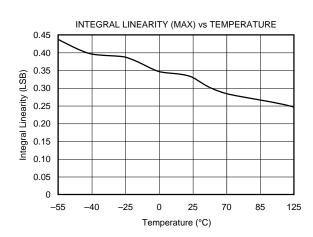

# **TYPICAL PERFORMANCE CURVES**

At  $V_{ANA+} = +5V$ ,  $V_{ANA-} = -5V$ ,  $V_{DIG+} = +5V$ ,  $V_{DIG-} = -5V$  and  $T_A = 25^{\circ}C$ , using internal reference,  $f_{CLOCK} = 2.1MHz$ .

DIFFERENTIAL LINEARITY (MIN) vs TEMPERATURE 0.000 -0.100 Differential Linearity (LSB) -0.200 -0.300 -0.400 -0.500 -0.600 -0.700 -55 -40 -25 0 25 70 85 125 Temperature (°C)

DIFFERENTIAL LINEARITY (MAX) vs TEMPERATURE

# **TYPICAL PERFORMANCE CURVES (CONT)**

At  $V_{ANA+} = +5V$ ,  $V_{ANA-} = -5V$ ,  $V_{DIG+} = +5V$ ,  $V_{DIG-} = -5V$  and  $T_A = 25^{\circ}C$ , using internal reference,  $f_{CLOCK} = 2.1MHz$ .

## **BASIC CIRCUIT CONFIGURATION**

## FUNCTIONAL DESCRIPTION

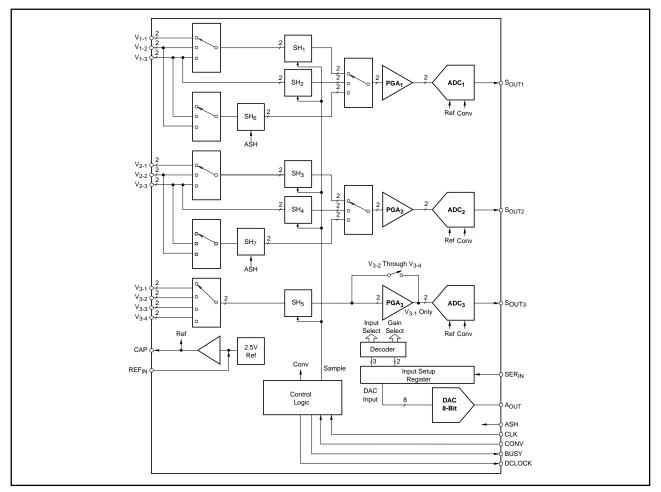

## (See Figure 1)

## ADCs AND PGAs

The ADS7833 contains three signal channels each with a 12-bit analog-to-digital converter output. The ADCs operate synchronously and their serial outputs occur simultaneously. (Table VI gives the analog input/digital output relation-

ships). The ADCs are preceded by programmable gain amplifiers. (Table II gives gain select information). For channels one and two, the PGAs are effective for all three analog inputs. For the third channel, only the  $V_{3-1}$  input is gain changed by the PGA. Inputs  $V_{3-2}$ ,  $V_{3-3}$ , and  $V_{3-4}$  are connected to ADC<sub>3</sub> at a fixed gain of 1V/V regardless of the Gain Select value.

FIGURE 1. Functional Diagram.

#### SAMPLE HOLDS

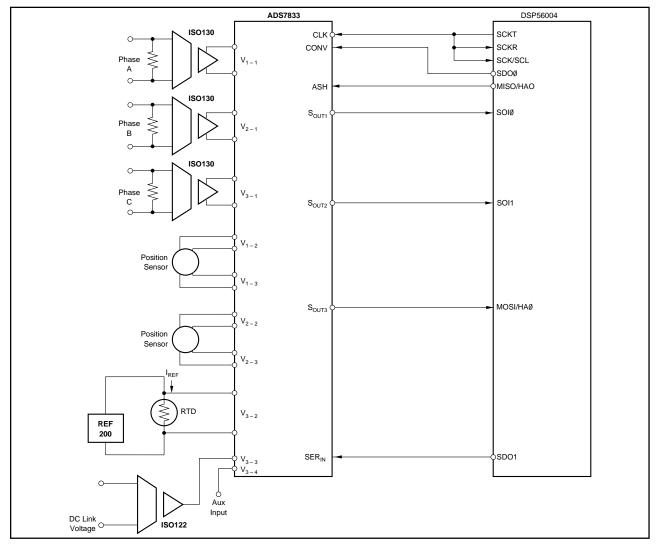

The ADS7833 contains seven sample holds. Five of them  $(SH_1 \text{ through } SH_5)$  sample simultaneously and have their sample/hold timing internally synchronized. (The timing is shown in Figure 2).

Three of the sample holds (SH<sub>1</sub>, SH<sub>3</sub>, and SH<sub>5</sub>) are connected to the input multiplexers so that they can provide simultaneous sampling for all of their channels inputs. In addition, SH<sub>2</sub> and SH<sub>4</sub> simultaneously sample the third input of their channels ( $V_{1-3}$  and  $V_{2-3}$ , respectively). This is useful in motor control applications where  $V_{1-2}$  and  $V_{1-3}$  are the quadrature inputs for one position sensor, and  $V_{2-2}$  and  $V_{2-3}$  are the quadrature inputs for a second position sensor (see Figure 6). In that application, it is desirable to sample

the quadrature inputs of a given position sensor at the same time (even though they are converted on successive conversion cycles) (see Table III), so that their values are captured at the same shaft position.

The ADS7833 also has the capability for limited asynchronous sampling. The sampling of  $SH_6$  and  $SH_7$  is controlled asynchronously by the control signal ASH (see Table III). This allows two inputs each on channel 1 and channel 2 (see Table IV) to be sampled asynchronously from the timing of the other sample holds. This can be useful in motor control applications where the two inputs for each channel come from a position sensor and it is desired to sample based on position sensor timing rather than system clock timing.

#### MULTIPLEXERS

The ADS7833 also contains several multiplexers that are used to select the desired analog inputs and connect the proper sample hold outputs to the PGAs and ADCs. The MUXs are driven by a decoder which receives its inputs from the Input Setup Register. (See Table III and Table IV for information on input channel selection). The input multiplexers can take full differential input signals (see Figure 3 and Table VII). The analog signals stay differential through the sample holds and the PGAs all the way to the inputs of the ADSs. This is done to provide the best possible high frequency noise rejection.

#### **INPUT SETUP**

As the ADCs are converting and transmitted their serial digital data for one conversion cycle, a setup word is being received to be used for the next conversion cycle. The 13-bit word is supplied at the SER<sub>IN</sub> pin (see Figure 1), and is stored in the buffered Input Setup Register. The Input Select and Gain Select portions of the word are decoded and determine the state of the multiplexers and PGAs (see CON-FIGURABLE PARAMETERS section).

#### DIGITAL-TO-ANALOG CONVERTER

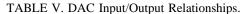

An 8-bit DAC provides 256 output voltage levels from 0V to 2.5V (see Table V for input/output relationships). The DAC is controlled by the DAC Input portion of the input setup word. The DAC Input portion of the word is strobed into the DAC at the end of the conversion cycle (14th CLK pulse in Figure 2).

## **VOLTAGE REFERENCE**

The ADS7833 contains an internal 2.5V voltage reference. It is available externally through an output buffer amplifier. If it is desired to use an external reference, one may be connected at the  $\text{REF}_{\text{IN}}$  pins. This then overrides the internal 2.5V reference, is connected to the ADCs and is available buffered at the CAP pin.

#### **OTHER DIGITAL INPUTS AND OUTPUTS**

Sampling and conversion is controlled by the CONV input (see Figure 2). The ADS7833 is designed to operate from an external clock supplied at the CLK input. This allows the conversion to be done synchronously with system timing so that transient noise effects can be minimized. The CLK signal may run continuously or may be supplied only during convert sequences. The BUSY and DCLOCK signals are internally generated and are supplied to make interfaces with microprocessors easier (see Figures 2, 4, and 6).

#### **CONFIGURABLE PARAMETERS**

Configurable parameters are:

- PGA Gain

- Input multiplexer and sample/hold selection

- DAC output voltage

Configuration information for these parameters is contained in the  $SER_{IN}$  word (See Figure 2). As one conversion is taking place, the configuration for the next conversion is being loaded into the buffered Input Setup Register via the  $SER_{IN}$  word. Table I shows information regarding these parameters.

| CLOCK<br>POSITIONS <sup>(1)</sup> | DESCRIPTION                                         | FUNCTIONS                             |  |  |  |  |

|-----------------------------------|-----------------------------------------------------|---------------------------------------|--|--|--|--|

| 2-9                               | DAC Input <sub>0-7</sub>                            | Sets DAC Output Voltage               |  |  |  |  |

| 10-11                             | Gain Select <sub>0-1</sub>                          | Sets PGA Gains                        |  |  |  |  |

| 12-14                             | Input Select <sub>0-2</sub>                         | Determines Multiplexers<br>Conditions |  |  |  |  |

| NOTE: (1) See F                   | NOTE: (1) See Figure 2. "Clock Pulse Reference No." |                                       |  |  |  |  |

TABLE I. Description of Configurable Parameters.

FIGURE 2. Timing Diagram.

#### PGA GAIN

The PGA gain is determined by the Gain Select portion (bits 8 and 9) in the  $SER_{IN}$  word (see Figure 2). There is one gain input that sets the same gain for all three PGAs. The gain values and allowable full scale inputs are shown in Table II.

For channels one and two the PGAs set the gain for all three analog inputs. For the third channel, only the  $V_{3-1}$  input is gain changed by the PGA. Inputs  $V_{3-2}$ ,  $V_{3-3}$  and  $V_{3-4}$  are connected to ADC<sub>3</sub> at a fixed gain of 1V/V regardless of the Gain Select value.

| GAIN                  | GAIN    | FULL SCALE |

|-----------------------|---------|------------|

| SELECT <sub>0-1</sub> | SETTING | INPUT      |

| 0 <sub>H</sub>        | 5.0V/V  | ±0.5V      |

| 1 <sub>H</sub>        | 2.5V/V  | ±1.0V      |

| 2 <sub>H</sub>        | 1.25V/V | ±2.0V      |

| 3 <sub>H</sub>        | 1.0V/V  | ±2.5V      |

TABLE II. Gain Select Information.

# INPUT MULTIPLEXER AND SAMPLE HOLD SELECTION

The Input Select portion of the  $SER_{IN}$  word (bits 10, 11 and 12) (see Figure 2) are decoded and determine the open/closed condition of the multiplexer switches. This in turn determines which input signals are connected to the sample holds and which sample holds are connected to the PGAs/ADCs.

## INPUT SIGNALS FOR PGAs/ADCs

Table III shows the relationships between the value of Input  $Select_{0-2}$  and the signals that are converted.

| INPUT          | SELECT <sub>0-2</sub> | ANALOG SIGNAL CONNECTED TO                          |                                                     |                                    |  |  |  |

|----------------|-----------------------|-----------------------------------------------------|-----------------------------------------------------|------------------------------------|--|--|--|

| HEX            | BINARY                | PGA <sub>x</sub> /ADC <sub>x</sub>                  |                                                     |                                    |  |  |  |

| CODE           | CODE                  | PGA <sub>1</sub> /ADC <sub>1</sub>                  | PGA <sub>2</sub> /ADC <sub>2</sub>                  | PGA <sub>3</sub> /ADC <sub>2</sub> |  |  |  |

| 0 <sub>H</sub> | 000                   | Undefined                                           | Undefined                                           | V <sub>3-4</sub>                   |  |  |  |

| 1 <sub>H</sub> | 001                   | V <sub>1-X</sub> via SH <sub>6</sub> <sup>(1)</sup> | V <sub>2-X</sub> via SH <sub>7</sub> <sup>(1)</sup> | V <sub>3-4</sub>                   |  |  |  |

| 2 <sub>H</sub> | 010                   | V <sub>1-3</sub> via SH <sub>1</sub>                | V <sub>2-3</sub> via SH <sub>3</sub>                | V <sub>3-3</sub>                   |  |  |  |

| 3 <sub>H</sub> | 011                   | V <sub>1-3</sub> via SH <sub>2</sub>                | V <sub>2-3</sub> via SH <sub>4</sub>                | V <sub>3-3</sub>                   |  |  |  |

| 4 <sub>H</sub> | 100                   | V <sub>1-2</sub>                                    | V <sub>2-2</sub>                                    | V <sub>3-2</sub>                   |  |  |  |

| 5 <sub>H</sub> | 101                   | V <sub>1-2</sub>                                    | V <sub>2-2</sub>                                    | V <sub>3-2</sub>                   |  |  |  |

| 6 <sub>H</sub> | 110                   | V <sub>1-2</sub>                                    | V <sub>2-2</sub>                                    | V <sub>3-2</sub>                   |  |  |  |

| 7 <sub>H</sub> | 111                   | V <sub>1-1</sub>                                    | V <sub>2-1</sub>                                    | V <sub>3-1</sub>                   |  |  |  |

| NOTE:          | (1) See Table I       | V for Operation.                                    | NOTE: (1) See Table IV for Operation.               |                                    |  |  |  |

TABLE III. Input Controls for Synchronous Sample Holds.

**Input Select = 7\_{H}**—Synchronously sample and convert input signals  $V_{1-1}$ ,  $V_{2-1}$ , and  $V_{3-1}$ .

**Input Select = 4<sub>H</sub>, 5<sub>H</sub>, 6<sub>H</sub>**—Synchronously sample and convert input signals  $V_{1-2}$ ,  $V_{2-2}$ , and  $V_{3-2}$ . These codes also cause SH<sub>2</sub> and SH<sub>4</sub> to sample their inputs. Values 4<sub>H</sub>, 5<sub>H</sub>, 6<sub>H</sub> have different effects on the inputs to SH<sub>6</sub> and SH<sub>7</sub> (see Table IV).

**Input Select = 3\_{H}**—Convert  $V_{1-3}$  via SH<sub>2</sub>,  $V_{2-3}$  via SH<sub>4</sub>, and  $V_{3-3}$  ( $V_{1-3}$  and  $V_{2-3}$  are from the value sampled in a preceding conversion cycle with Input Select =  $4_{H}$ ,  $5_{H}$  or  $6_{H}$ ).

**Input Select = 2\_{H}**—Convert  $V_{1-3}$  via  $SH_1$ ,  $V_{2-3}$  via  $SH_3$ , and  $V_{3-3}$  ( $V_{1-3}$  is sampled on  $SH_2$  in this conversion cycle). **Input Select = 1\_{H}**—Input  $V_{3-4}$  is converted by PGA<sub>3</sub>/ADC<sub>3</sub>. The output of the asynchronous sample holds,  $SH_6$  and  $SH_7$ , are converted by PGA<sub>1</sub>/ADC<sub>1</sub> and PGA<sub>2</sub>/ADC<sub>2</sub>, respectively. Note that the inputs to  $SH_6$  and  $SH_7$  are determined by previous Input Select values (see Table IV). Thus, to properly convert the output of one of the asynchronous sample holds it is first necessary to choose its input with a previous conversion cycle. Also, the output of  $SH_6$  or  $SH_7$  will only be converted if ASH goes low before the CONV command is received.

**Input Select = 0\_{H}**– $V_{3-4}$  is converted by PGA<sub>3</sub>/ADC<sub>3</sub>. The inputs to PGA<sub>1</sub>/ADC<sub>1</sub> and PGA<sub>2</sub>/ADC<sub>2</sub> are undefined.

## CONVERSIONS FROM THE ASYNCHRONOUS SAMPLE HOLDS

Decoding the Input Select value also determines which inputs are applied to the two asynchronously controlled sample holds  $SH_6$  and  $SH_7$ . (See Table IV.) One of the three possible inputs is selected by the Input Select value being 4, 5, or 6.

The "No Effect" states indicate that these values of Input Select have no effect on the multiplexers at the input of  $SH_6$  and  $SH_7$ . When one of the "No Effect" values of Input Select is presented, the multiplexers will not be changed (i.e., their condition is determined by the last 4, 5, or 6 value of Input Select that existed prior to the "No Effect" state).

Note that Input Select =  $1_{\rm H}$  presents the output of SH<sub>6</sub> and SH<sub>7</sub> (1ASH<sub>X</sub> and 2ASH<sub>X</sub>) to PGA<sub>1</sub>/ADC<sub>1</sub> and PGA<sub>2</sub>/ADC<sub>2</sub>, respectively (see Table III). Therefore, in order to properly convert the asynchronous sampled signals, it is first necessary to choose an input signal (Input Select equal 5 or 6 in Table IV) with one load/convert cycle and then convert the sample hold output (Input Select = 4 in Table III) in a following conversion cycle.

| INPUT          | SELECT <sub>0-2</sub> |                  |                  |

|----------------|-----------------------|------------------|------------------|

| HEX            | BINARY                | ANALOG SIGNAL    | CONNECTED TO     |

| CODE           | CODE                  | SH <sub>6</sub>  | SH <sub>7</sub>  |

| 0 <sub>H</sub> | 000                   | No Effect        | No Effect        |

| 1 <sub>H</sub> | 001                   | No Effect        | No Effect        |

| 2 <sub>H</sub> | 010                   | No Effect        | No Effect        |

| 3 <sub>H</sub> | 011                   | No Effect        | No Effect        |

| 4 <sub>H</sub> | 100                   | Open             | Open             |

| 5 <sub>H</sub> | 101                   | V <sub>1-3</sub> | V <sub>2-3</sub> |

| 6 <sub>H</sub> | 110                   | V <sub>1-2</sub> | V <sub>1-2</sub> |

| 7 <sub>H</sub> | 111                   | No Effect        | No Effect        |

TABLE IV. Input Controls for Asynchronous Sample Holds.

ADS7833

## DAC OUTPUT VOLTAGE

The value of the DAC output voltage is determined by the DAC Input portion of the SER<sub>IN</sub> word (bits 0 through 7—see Figure 2). The 8-bit DAC has 256 possible output voltages from 0V to +2.49V. The value of 1 LSB is 0.0098V.

## ANALOG-TO-DIGITAL CONVERTERS

### ARCHITECTURE

The ADCs are 12-bit, successive approximation types implemented with a switched capacitor circuitry.

### SPEED

The clock for the ADC conversion is supplied externally at the CLK pin. Maximum clock frequency for specified accuracy is 2.1MHz. This results in a complete conversion cycle (S/H acquisition and A/D conversion) of 6.6µs.

#### **INPUT/OUTPUT**

The ADS7833 is designed for bipolar input voltages and uses a binary two's complement digital output code. A programmable gain function is associated with each ADC. This changes the full scale analog input range and the analog resolution of the converter. Details are shown in Table VI.

### DIFFERENTIAL AND COMMON-MODE INPUT VOLTAGES

The ADS7833 is designed with full differential signal paths all the way from the multiplexer inputs through to the input of the ADCs. This was done to provide superior high frequency noise rejection.

|                                    | L INPUT<br>IPUT <sub>0-7</sub> | ANALOG OUTPUT  |

|------------------------------------|--------------------------------|----------------|

| HEX<br>CODE                        | BINARY<br>CODE                 |                |

| 00 <sub>H</sub><br>01 <sub>H</sub> | 0000 0000<br>0000 0001         | 0V<br>+0.0098V |

| •                                  | •                              | •              |

| •<br>FF <sub>H</sub>               | •<br>1111 1111                 | •<br>+2.499    |

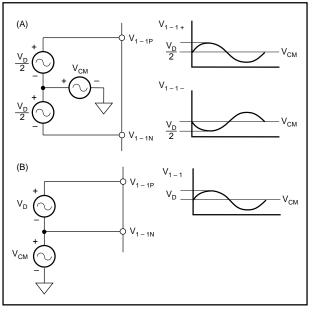

As is common with most differential input semiconductor devices, there are compound restrictions on the combination of differential and common-mode input voltages. This matter is made slightly more complicated by the fact that most of the analog inputs are capable of being affected by the programmable gain function. The possible differential and single ended configurations are shown in Figures 3a and 3b.

The maximum differential and common mode restrictions are shown in Table VII.

| GAIN SELECT CODE                                              | 0      | 1      | 2       | 3      |

|---------------------------------------------------------------|--------|--------|---------|--------|

| Gain                                                          | 5.0V/V | 2.5V/V | 1.25V/V | 1.0V/V |

| Full Scale Range<br>( $V_D$ with $V_{CM} = 0$ )               | ±0.5V  | ±1.0V  | ±2.0V   | ±2.5V  |

| Largest Positive<br>Common Mode<br>Voltage, V <sub>CM</sub> + | +2.7V  | +2.4V  | +1.9V   | +1.6V  |

| Largest Negative<br>Common Mode<br>Voltage, V <sub>CM</sub> - | -2.7V  | -2.4V  | -1.9V   | -1.6V  |

TABLE VII. Differential and Common Mode Voltage Restrictions.

FIGURE 3. (a) Differential Signal Source, and (b) Single Ended Signal Source.

| DESCRIPTION                                                                                              | ANALOG INPUT                                     |                                                   |                                                  |                                               | DIGITAL OUTPUT                                                                       |                                                                                        |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------|--------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| GAIN SELECT CODE                                                                                         | 0                                                | 1                                                 | 2                                                | 3                                             |                                                                                      |                                                                                        |

| GAIN                                                                                                     | 5V/V                                             | 2.5V/V                                            | 1.25V/V                                          | 1.0V/V                                        | BINARY TWO'S COMPLIMENT FORMAT                                                       |                                                                                        |

| FULL SCALE RANGE                                                                                         | ±0.5V                                            | ±1.0V                                             | ±2.0V                                            | ±2.5V                                         | HEX CODE                                                                             | BINARY CODE                                                                            |

| +Full Scale (FS –1LSB)<br>One Bit above Mid-Scale<br>Mid-Scale<br>One Bit Below Mid-Scale<br>-Full Scale | +0.49976<br>+0.244mV<br>0V<br>-0.244V<br>-0.500V | +0.9995V<br>+0.488mV<br>0V<br>-0.488mV<br>-1.000V | +1.999V<br>+0.976mV<br>0V<br>-0.976mV<br>-2.000V | +2.499<br>+1.22mV<br>0V<br>-1.22mV<br>-2.500V | 7FF <sub>H</sub><br>001H<br>000 <sub>H</sub><br>FFF <sub>H</sub><br>800 <sub>H</sub> | 0111 1111 1111<br>0000 0000 0001<br>0000 0000 0000<br>1111 1111 1111<br>1000 0000 0000 |

NOTE: The programmable gain function applies to all three input channels for  $ADC_1$  and  $ADC_2$ . However, the programmable gain function only applies to the first input ( $V_{3:1}$ ) for  $ADC_3$ . The other three inputs ( $V_{3:2}$ ,  $V_{3:3}$ , and  $V_{3:4}$ ) are not affected by the GAIN SEL input. They operate at a fixed gain of 1V/V and thus have a fixed ±2.5V full scale input range.

TABLE VI. Analog Input - Digital Output Relationships.

ADS7833

#### MICROPROCESSOR INTERFACE

The internal logic of the ADS7833 is designed for easy control and data interface with microprocessors. Figure 4 shows the interface for loading the input control word from the microprocessor data bus into the serial input of the ADS7833.

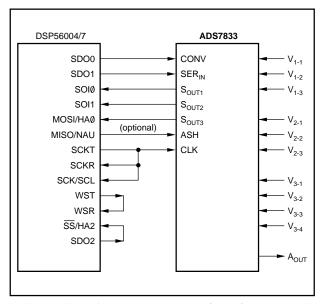

Table VIII provides a sample assembly code and Figure 4 shows the connection diagram for connecting an ADS7833 to the DSP56004N—or DSP56007 a Motorola Digital Signal Processor. This configuration allows for full control of the ADS7833 as well as receiving all three conversion results simultaneously. The start of conversion is generated by the DSP56004 as well as the sample time of the asynchronous sample/holds.

FIGURE 4. Microprocessor Interface for Motorola DSP56004/7.

While this is one of the most useful, the DSP56004/7 is flexible enough to allow various other configurations. These will free up the serial outputs for use with other serial peripherals, such as DACs.

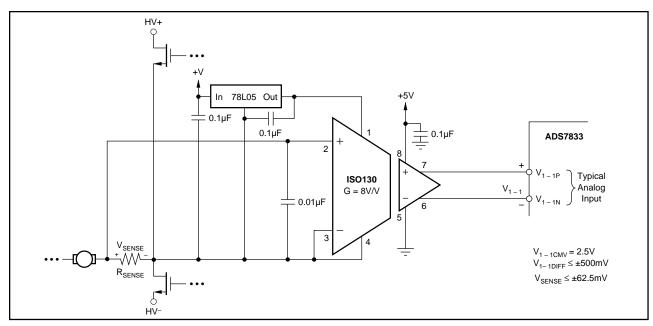

#### TYPICAL ISOLATED ANALOG INPUT

Figure 5 shows an ISO130 used to isolate the current measurement in a motor speed control application. This amplifier is well suited for this application because of its high transient immunity ( $10kV/\mu s$ ). Its differential output feature is well suited to the differential input of the ADS7833. Keeping the signal transmission differential helps to preserve the high frequency noise rejection of the system.

A unique characteristic of the ISO130 is that it has a common mode output voltage of approximately 2.39V. To accept this level of CMV, the ADS7833 must be operated at a gain of 5V/V ( $\pm 0.5V$  full scale differential input). (See Figure 3 and Table VII). Since the ISO130 has a gain of 8V/V, the maximum value of V<sub>SENSE</sub> is 62.5mV. Thus, the value of R<sub>SENSE</sub> is chosen to scale V<sub>SENSE</sub> to this maximum value.

#### **POWER-UP INITIALIZATION**

When power is applied to the ADS7833, two conversion cycles are required for initialization and valid digital data is transmitted on the third cycle.

The first conversion after power is applied is performed with indeterminate configuration values in the double buffer output of the Input Setup Register. The second conversion cycle loads the desired values into the register. The third conversion uses those values to perform proper conversions and output valid digital data from each of the ADCs.

|      | movep | #>\$0,x:\$ffe4                    | ; Disable SAI transmit port                            |

|------|-------|-----------------------------------|--------------------------------------------------------|

|      | movep | #>\$0,x:\$ffe1                    | ; Disable SAI receive port                             |

|      | movep | #>\$0,x:\$fff1                    | ; Disable SHI port                                     |

|      | ;     |                                   |                                                        |

|      | movep | <pre>#&gt;\$dfff00,x:\$ffe5</pre> | ; Convert command                                      |

|      | movep | #>\$101f00,x:\$ffe6               | ; DAC to midscale, G=1V/V, Channel 1 all ADCs          |

|      | movep | #>\$0,x:\$ffe7                    | ; For SS pin-enables SHI at proper time                |

|      | movep | #>\$10d,x:\$ffe0                  | ; Divide by 1 pre, divide by 13-96kHz conv @ 40MHz     |

|      | movep | #>\$3,x:\$ffe1                    | ; Enable SAI recv (rsng edge, MSB 1st, 16-bits, slave) |

|      |       |                                   |                                                        |

|      | movep | #>\$2001,x:\$fff0                 | ; Set narrow spike filter, CPOL=0, CPHA=1              |

|      | movep | #>\$5,x:\$fff1                    | ; Enable SHI (slave, no fifo, 16-bits)                 |

|      | movep | #>\$f,x:\$ffe4                    | ; Enable SAI trans (rsng edge, MSB 1st, 16-bits, mstr) |

|      | ;     |                                   |                                                        |

| wait | btst  |                                   | ; Look for a receive flag (left or right)              |

|      | jcs   | data                              |                                                        |

|      | btst  | #15,x:\$ffe1                      |                                                        |

|      | jcc   | wait                              |                                                        |

| data | movep | x:\$ffe2,x0                       | ; Get Sout1                                            |

|      | move  | x0,x:\$00                         | ; Save it                                              |

|      | movep | x:\$ffe3,x0                       | ; Get Sout2                                            |

|      | move  | x0,x:\$01                         | ; Save it                                              |

|      | move  | x:\$fff3,x0                       | ; Get Sout3                                            |

|      | movep | x0,x:\$02                         | ; Save it                                              |

|      |       |                                   |                                                        |

TABLE VIII. Sample Code for Motorola DSP56004/7.

FIGURE 5. Typical Isolated Differential Analog Input.

FIGURE 6. Motor Control Application Using Position Sensors.