# ADSP-2106x SHARC® DSP Microcomputer Family

# ADSP-21062/ADSP-21062L

#### SUMMARY

- High Performance Signal Processor for Communications, Graphics and Imaging Applications

- Super Harvard Architecture

- Four Independent Buses for Dual Data Fetch, Instruction Fetch and Nonintrusive I/O

- 32-Bit IEEE Floating-Point Computation Units Multiplier, ALU, and Shifter

- Dual-Ported On-Chip SRAM and Integrated I/O Peripherals—A Complete System-On-A-Chip Integrated Multiprocessing Features

### **KEY FEATURES**

- 40 MIPS, 25 ns Instruction Rate, Single-Cycle Instruction Execution

- 120 MFLOPS Peak, 80 MFLOPS Sustained Performance Dual Data Address Generators with Modulo and Bit-

- Reverse Addressing

Efficient Program Sequencing with Zero-Overhead Looping: Single-Cycle Loop Setup

- IEEE JTAG Standard 1149.1 Test Access Port and On-Chip Emulation

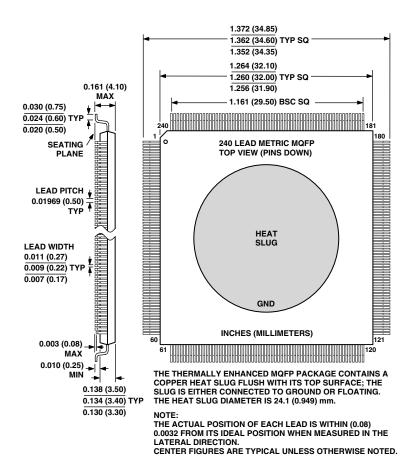

- 240-Lead Thermally Enhanced MQFP Package

- 225-Ball Plastic Ball Grid Array (PBGA)

- 32-Bit Single-Precision and 40-Bit Extended-Precision IEEE Floating-Point Data Formats or 32-Bit Fixed-Point Data Format

### **Parallel Computations**

Single-Cycle Multiply and ALU Operations in Parallel with Dual Memory Read/Writes and Instruction Fetch Multiply with Add and Subtract for Accelerated FFT Butterfly Computation

### 2 Mbit On-Chip SRAM

Dual-Ported for Independent Access by Core Processor and DMA

### **Off-Chip Memory Interfacing**

- 4 Gigawords Addressable

- Programmable Wait State Generation, Page-Mode DRAM Support

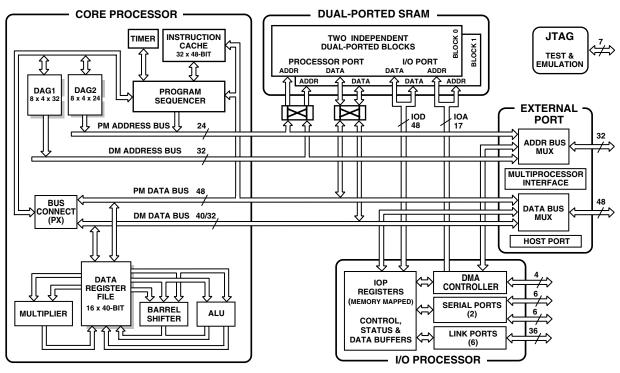

Figure 1. ADSP-21062/ADSP-21062L Block Diagram

SHARC is a registered trademark of Analog Devices, Inc.

### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

#### DMA Controller

- 10 DMA Channels for Transfers Between ADSP-21062 Internal Memory and External Memory, External Peripherals, Host Processor, Serial Ports, or Link Ports

- Background DMA Transfers at 40 MHz, in Parallel with Full-Speed Processor Execution

Host Processor Interface to 16- and 32-Bit Microprocessors Host Can Directly Read/Write ADSP-21062 Internal Memory

#### Multiprocessing

| maniprococomg                                                           |      |

|-------------------------------------------------------------------------|------|

| <b>Glueless Connection for Scalable DSP Multiprocessi</b>               | ng   |

| Architecture                                                            |      |

| <b>Distributed On-Chip Bus Arbitration for Parallel Bus</b>             |      |

| Connect of Up to Six ADSP-21062s Plus Host                              |      |

| Six Link Ports for Point-to-Point Connectivity and A<br>Multiprocessing | rray |

| 240 Mbytes/s Transfer Rate Over Parallel Bus                            |      |

| 240 Mbytes/s Transfer Rate Over Link Ports                              |      |

|                                                                         |      |

#### Serial Ports

Two 40 Mbit/s Synchronous Serial Ports with Companding Hardware Independent Transmit and Receive Functions

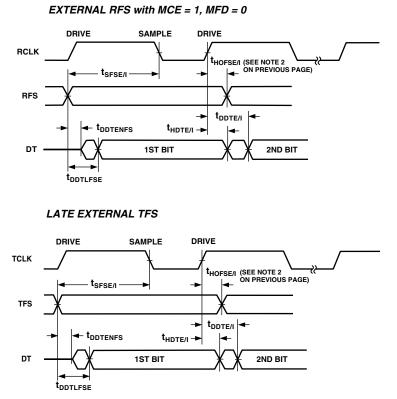

Figure 7. JTAG Clocktree for Multiple ADSP-2106x

Systems

12

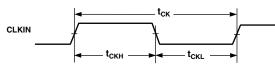

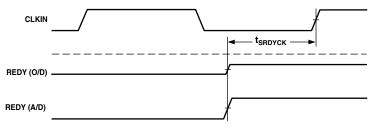

Figure 8. Clock Input

18

### TABLE OF CONTENTS

| GENERAL DESCRIPTION 3                              |

|----------------------------------------------------|

| ADSP-21000 FAMILY CORE ARCHITECTURE 4              |

| ADSP-21062/ADSP-21062L FEATURES 4                  |

| DEVELOPMENT TOOLS 7                                |

| PIN FUNCTION DESCRIPTIONS 8                        |

| TARGET BOARD CONNECTOR FOR EZ-ICE <sup>®</sup>     |

| PROBE 11                                           |

| RECOMMENDED OPERATING CONDITIONS 13                |

| ELECTRICAL CHARACTERISTICS 13                      |

| TIMING SPECIFICATIONS 17                           |

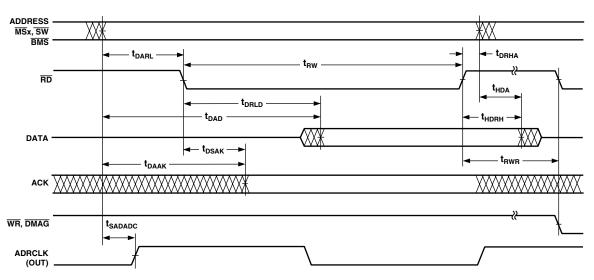

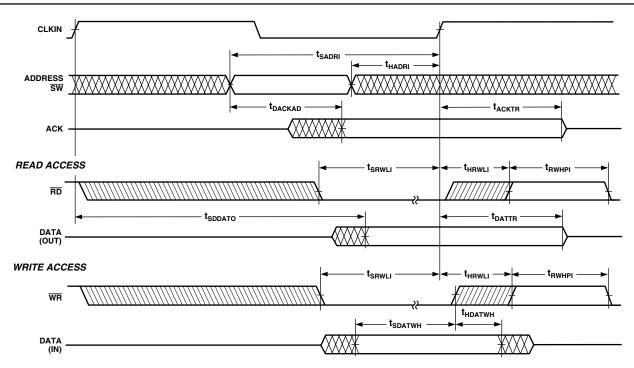

| Memory Read—Bus Master 20                          |

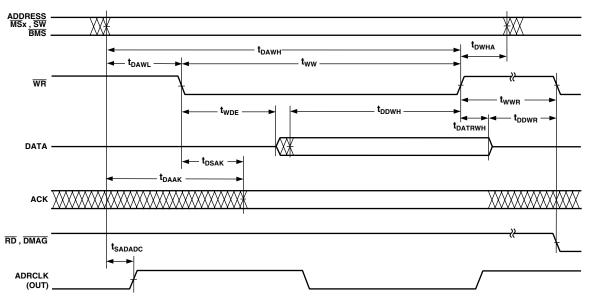

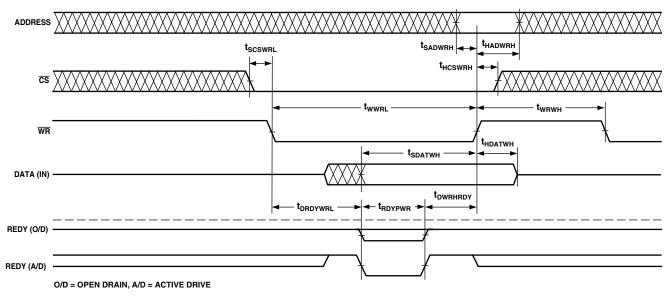

| Memory Write—Bus Master 21                         |

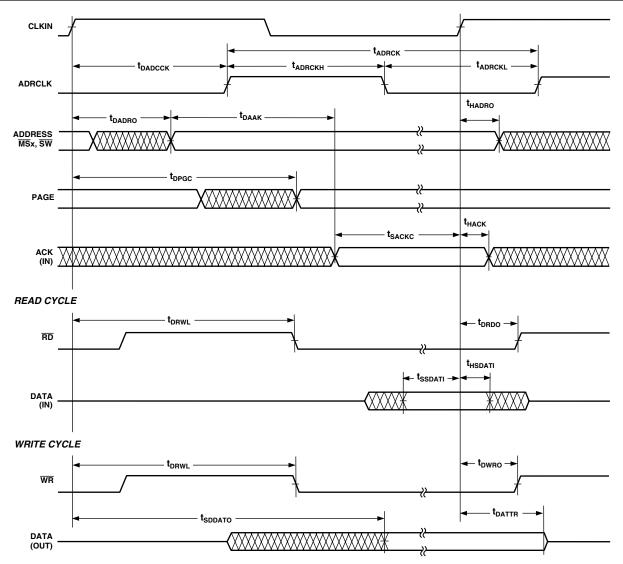

| Synchronous Read/Write—Bus Master                  |

| Synchronous Read/Write—Bus Slave                   |

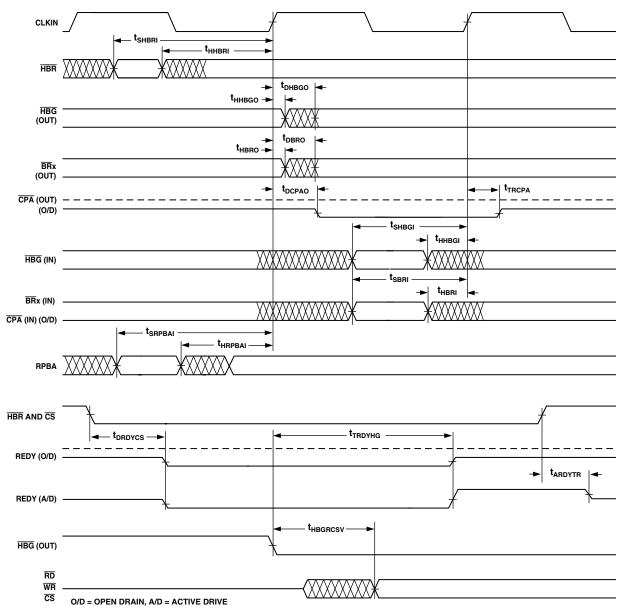

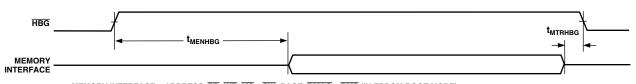

| Multiprocessor Bus Request and Host Bus Request 26 |

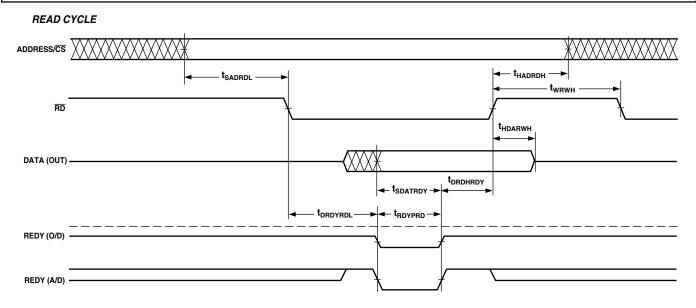

| Asynchronous Read/Write—Host to ADSP-21062 28      |

| Three-State Timing—Bus Master, Bus Slave,          |

| HBR, <u>SBTS</u> 30                                |

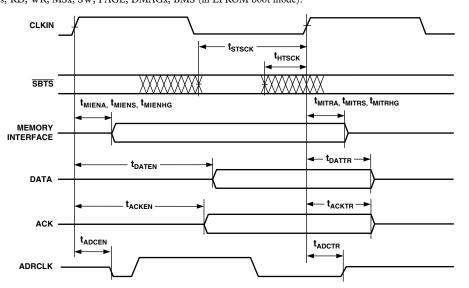

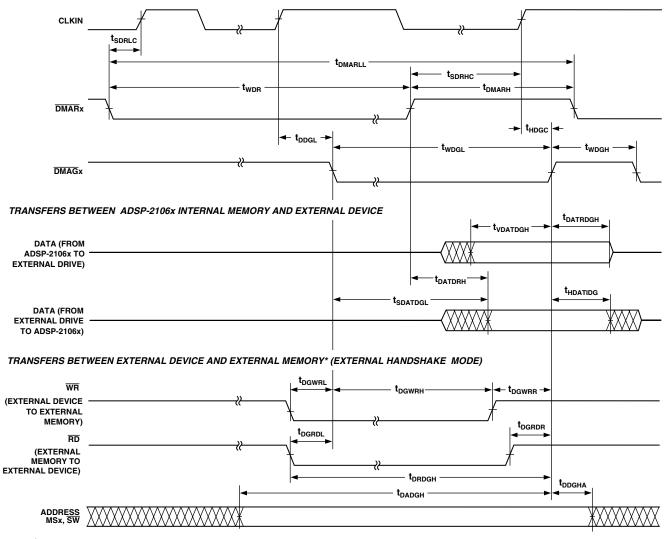

| DMA Handshake 31                                   |

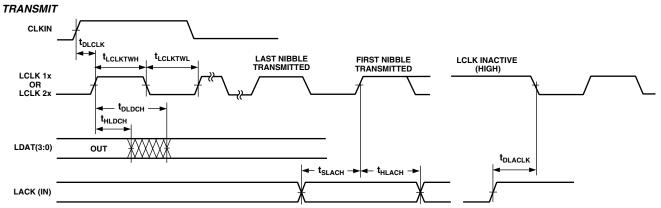

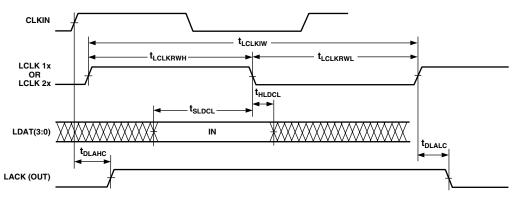

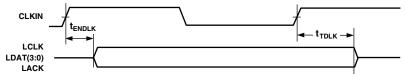

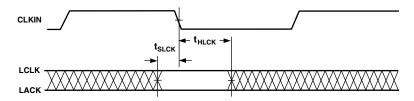

| Link Ports: 1 × CLK Speed Operation                |

| Link Ports: 2 × CLK Speed Operation                |

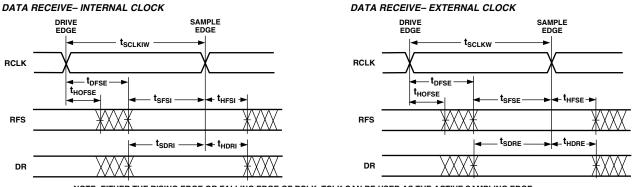

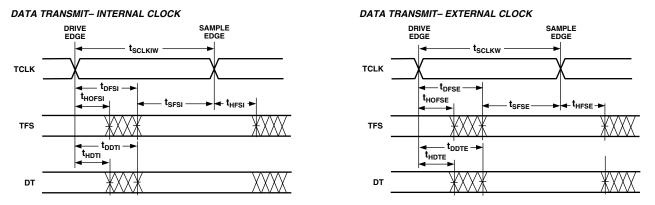

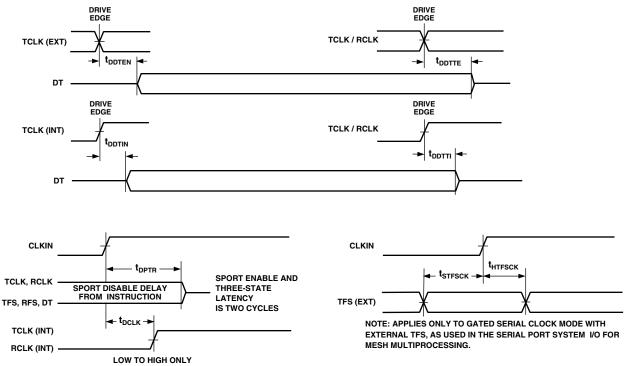

| Serial Ports                                       |

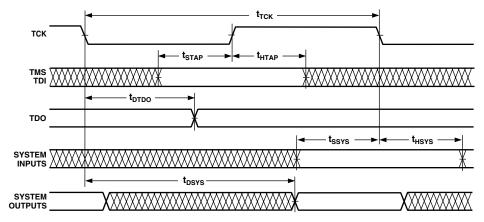

| JTAG Test Access Port and Emulation 39             |

| OUTPUT DRIVE CURRENTS 40                           |

| POWER DISSIPATION 40                               |

| TEST CONDITIONS 40                                 |

| ENVIRONMENTAL CONDITIONS 43                        |

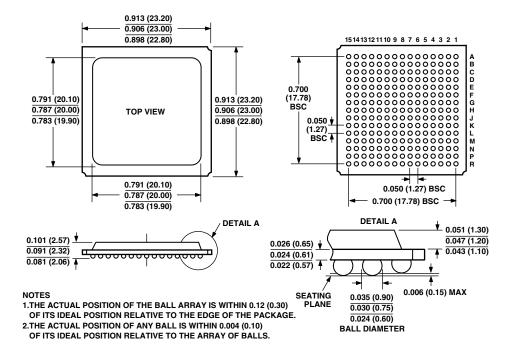

| 225 Ball Plastic Ball Grid Array (PBGA)            |

| Package Descriptions                               |

| 225 Ball Plastic Ball Grid Array (PBGA)            |

| Package Pinout                                     |

| PACKAGE DIMENSIONS, 225-Ball PBGA                  |

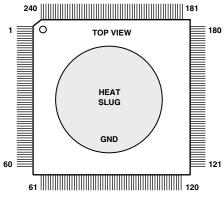

| 240-LEAD METRIC MQFP PIN CONFIGURATIONS 47         |

| PACKAGE DIMENSIONS, 240-Lead Metric MQFP 48        |

| ORDERING GUIDE 48                                  |

#### Figures

| Figure 1. ADSP-21062/ADSP-21062L Block Diagram 1  |

|---------------------------------------------------|

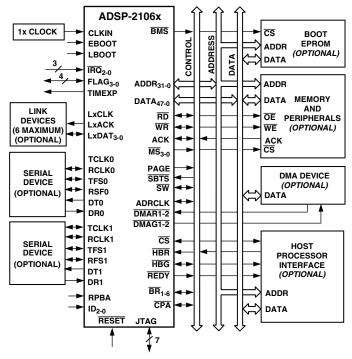

| Figure 2. ADSP-21062 System 4                     |

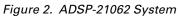

| Figure 3. Shared Memory Multiprocessing System 6  |

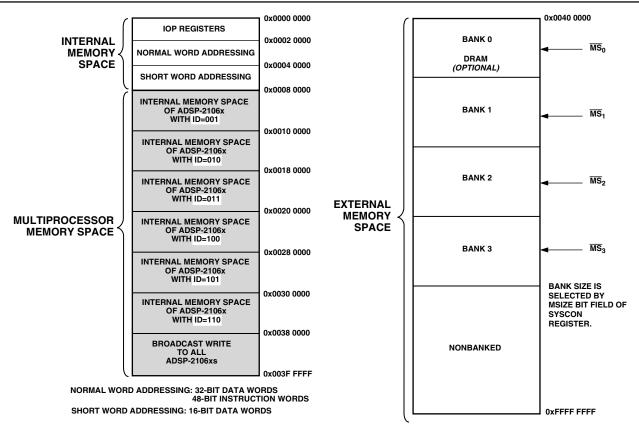

| Figure 4. ADSP-21062/ADSP-21062L Memory Map 7     |

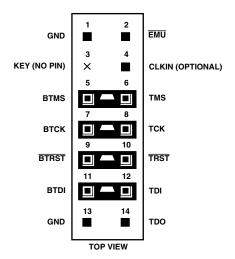

| Figure 5. Target Board Connector For ADSP-2106x   |

| EZ-ICE Emulator (Jumpers in Place)                |

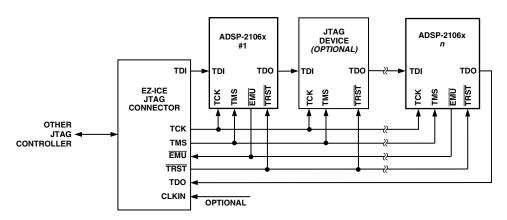

| Figure 6. JTAG Scan Path Connections for Multiple |

| ADSP-2106x Systems 11                             |

|                                                   |

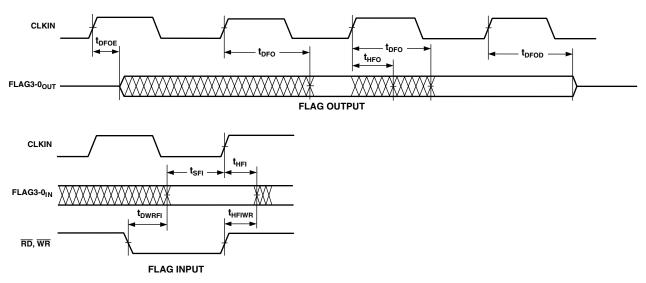

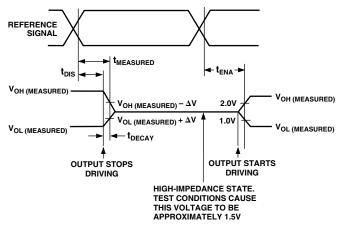

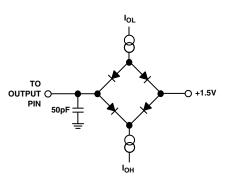

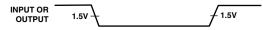

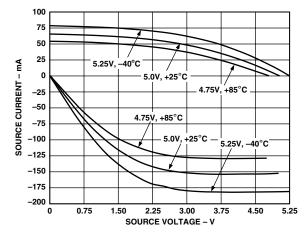

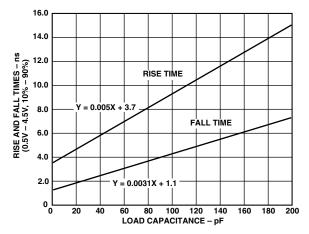

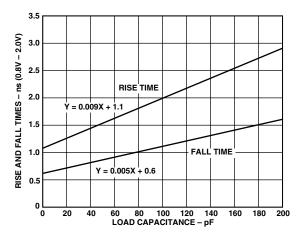

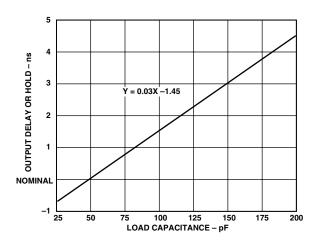

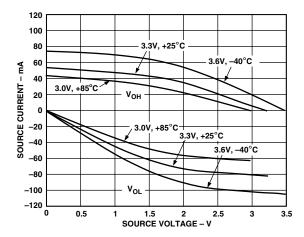

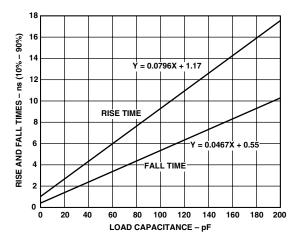

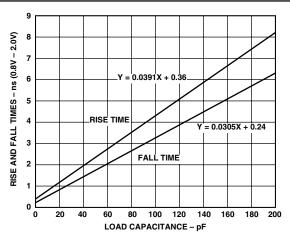

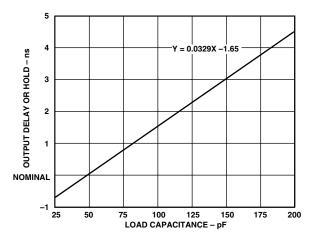

Figure 10. Interrupts ..... 18 Figure 11. Timer ..... 19 Figure 12. Flags ..... 19 Figure 13. Memory Read—Bus Master ..... 20 Figure 14. Memory Write—Bus Master ..... 21 Figure 15. Synchronous Read/Write—Bus Master ..... 23 Figure 16. Synchronous Read/Write-Bus Slave ..... 25 Figure 17. Multiprocessor Bus Request and Host Bus Figure 18a. Synchronous REDY Timing ..... 28 Figure 18b. Asynchronous Read/Write-Host to ADSP-21062 ..... 29 Figure 19a. Three-State Timing (Bus Transition Cycle, Figure 19b. Three-State Timing (Host Transition Cycle) . . 30 Figure 20. DMA Handshake Timing ...... 32 Figure 24. IEEE 11499.1 JTAG Test Access Port ..... 39 Figure 25. Output Enable/Disable ...... 41 Figure 26. Equivalent Device Loading for AC Measurements (Includes All Fixtures) ..... 41 Figure 27. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable) ..... 41 Figure 28. ADSP-21062 Typical Drive Currents Figure 29. Typical Output Rise Time (10%–90% V<sub>DD</sub>) Figure 30. Typical Output Rise Time (0.8 V-2.0 V) vs. Load Capacitance ( $V_{DD} = 5 V$ ) ..... 42 Figure 31. Typical Output Delay or Hold vs. Load Capacitance Figure 32. ADSP-21062 Typical Drive Currents Figure 33. Typical Output Rise Time (10%–90% V<sub>DD</sub>) ...

| vs. Load Capacitance (V <sub>DD</sub> = | = 3.3  V                    | 42 |

|-----------------------------------------|-----------------------------|----|

| Figure 34. Typical Output Rise          | Time (0.8 V–2.0 V) vs. Load |    |

| Capacitance ( $V_{DD}$ = 3.3 V)         |                             | 43 |

Figure 35. Typical Output Delay or Hold vs. Load Capacitance (at Maximum Case Temperature) (V<sub>DD</sub> = 3.3 V) ...... 43

EZ-ICE is a registered trademark of Analog Devices, Inc.

# **SHARC**

### **GENERAL NOTE**

This data sheet represents production released specifications for the ADSP-21062 (5 V) and ADSP-21062L (3.3 V) processors, for both 33 MHz and 40 MHz speed grades. The product name "ADSP-21062" is used throughout this data sheet to represent all devices, except where expressly noted.

### **GENERAL DESCRIPTION**

The ADSP-21062 SHARC—Super Harvard Architecture Computer—is a signal processing microcomputer that offers new capabilities and levels of performance. The ADSP-21062 SHARCs are 32-bit processors optimized for high performance DSP applications. The ADSP-21062 builds on the ADSP-21000 DSP core to form a complete system-on-a-chip, adding a dualported on-chip SRAM and integrated I/O peripherals supported by a dedicated I/O bus.

Fabricated in a high speed, low power CMOS process, the ADSP-21062 has a 25 ns instruction cycle time and operates at 40 MIPS. With its on-chip instruction cache, the processor can execute every instruction in a single cycle. Table I shows performance benchmarks for the ADSP-21062.

The ADSP-21062 SHARC represents a new standard of integration for signal computers, combining a high performance floating-point DSP core with integrated, on-chip system features including a 2 Mbit SRAM memory (4 Mbit on the ADSP-21060), host processor interface, DMA controller, serial ports and link port and parallel bus connectivity for glueless DSP multiprocessing.

Figure 1 shows a block diagram of the ADSP-21062, illustrating the following architectural features:

Computation Units (ALU, Multiplier and Shifter) with a Shared Data Register File Data Address Generators (DAG1, DAG2) Program Sequencer with Instruction Cache Interval Timer On-Chip SRAM External Port for Interfacing to Off-Chip Memory and Peripherals Host Port and Multiprocessor Interface DMA Controller Serial Ports and Link Ports JTAG Test Access Port

Figure 2 shows a typical single-processor system. A multiprocessing system is shown in Figure 3.

| Table I. | ADSP | -21062/ADSP | -21062L | Benchmarks | (@ 40 | MHz) |

|----------|------|-------------|---------|------------|-------|------|

|----------|------|-------------|---------|------------|-------|------|

| 1024-Pt. Complex FFT               | 0.46 ms      | 18,221 cycles       |  |

|------------------------------------|--------------|---------------------|--|

| (Radix 4, with Digit Reverse)      |              |                     |  |

| FIR Filter (per Tap)               | 25 ns        | 1 cycle             |  |

| IIR Filter (per Biquad)            | 100 ns       | 1 cycle<br>4 cycles |  |

| Divide (y/x)                       | 150 ns       | 6 cycles            |  |

| Inverse Square Root $(1/\sqrt{x})$ | 225 ns       | 9 cycles            |  |

| DMA Transfer Rate                  | 240 Mbytes/s |                     |  |

### ADSP-21000 FAMILY CORE ARCHITECTURE

The ADSP-21062 includes the following architectural features of the ADSP-21000 family core. The ADSP-21062 processors are code- and function-compatible with the ADSP-21020.

### Independent, Parallel Computation Units

The arithmetic/logic unit (ALU), multiplier and shifter all perform single-cycle instructions. The three units are arranged in parallel, maximizing computational throughput. Single multifunction instructions execute parallel ALU and multiplier operations. These computation units support IEEE 32-bit singleprecision floating-point, extended precision 40-bit floatingpoint, and 32-bit fixed-point data formats.

### Data Register File

A general purpose data register file is used for transferring data between the computation units and the data buses, and for storing intermediate results. This 10-port, 32-register (16 primary, 16 secondary) register file, combined with the ADSP-21000 Harvard architecture, allows unconstrained data flow between computation units and internal memory.

### Single-Cycle Fetch of Instruction and Two Operands

The ADSP-21062 features an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the program memory (PM) bus transfers both instructions and data (see Figure 1). With its separate program and data memory buses and on-chip instruction cache, the processor can simultaneously fetch two operands and an instruction (from the cache), all in a single cycle.

### **Instruction Cache**

The ADSP-21062 includes an on-chip instruction cache that enables three-bus operation for fetching an instruction and two data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This allows full-speed execution of core, looped operations such as digital filter multiply-accumulates and FFT butterfly processing.

### Data Address Generators with Hardware Circular Buffers

The ADSP-21062's two data address generators (DAGs) implement circular data buffers in hardware. Circular buffers allow efficient programming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The two DAGs of the ADSP-21062 contain sufficient registers to allow the creation of up to 32 circular buffers (16 primary register sets, 16 secondary). The DAGs automatically handle address pointer wraparound, reducing overhead, increasing performance and simplifying implementation. Circular buffers can start and end at any memory location.

### **Flexible Instruction Set**

The 48-bit instruction word accommodates a variety of parallel operations, for concise programming. For example, the ADSP-21062 can conditionally execute a multiply, an add, a subtract and a branch, all in a single instruction.

### ADSP-21062/ADSP-21062L FEATURES

Augmenting the ADSP-21000 family core, the ADSP-21062 adds the following architectural features:

### **Dual-Ported On-Chip Memory**

The ADSP-21062 contains two megabits of on-chip SRAM, organized as two blocks of 1 Mbits each, which can be configured for different combinations of code and data storage. Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor or DMA controller. The dual-ported memory and separate on-chip buses allow two data transfers from the core and one from I/O, all in a single cycle.

On the ADSP-21062, the memory can be configured as a maximum of 64K words of 32-bit data, 128K words of 16-bit data, 40K words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to two megabits. All of the memory can be accessed as 16-bit, 32-bit or 48-bit words.

A 16-bit floating-point storage format is supported, which effectively doubles the amount of data that may be stored on-chip. Conversion between the 32-bit floating-point and 16-bit floatingpoint formats is done in a single instruction.

While each memory block can store combinations of code and data, accesses are most efficient when one block stores data, using the DM bus for transfers, and the other block stores instructions and data, using the PM bus for transfers. Using the DM bus and PM bus in this way, with one dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache. Single-cycle execution is also maintained when one of the data operands is transferred to or from off-chip, via the ADSP-21062's external port.

### **Off-Chip Memory and Peripherals Interface**

The ADSP-21062's external port provides the processor's interface to off-chip memory and peripherals. The 4-gigaword offchip address space is included in the ADSP-21062's unified address space. The separate on-chip buses—for PM addresses, PM data, DM addresses, DM data, I/O addresses and I/O data—are multiplexed at the external port to create an external system bus with a single 32-bit address bus and a single 48-bit (or 32-bit) data bus.

Addressing of external memory devices is facilitated by on-chip decoding of high-order address lines to generate memory bank select signals. Separate control lines are also generated for simplified addressing of page-mode DRAM. The ADSP-21062 provides programmable memory wait states and external memory acknowledge controls to allow interfacing to DRAM and peripherals with variable access, hold and disable time requirements.

### Host Processor Interface

The ADSP-21062's host interface allows easy connection to standard microprocessor buses, both 16-bit and 32-bit, with little additional hardware required. Asynchronous transfers at speeds up to the full clock rate of the processor are supported. The host interface is accessed through the ADSP-21062's external port and is memory-mapped into the unified address space. Four channels of DMA are available for the host interface; code and data transfers are accomplished with low software overhead.

The host processor requests the ADSP-21062's external bus with the host bus request ( $\overline{\text{HBR}}$ ), host bus grant ( $\overline{\text{HBG}}$ ), and ready (REDY) signals. The host can directly read and write the internal memory of the ADSP-21062, and can access the DMA channel setup and mailbox registers. Vector interrupt support is provided for efficient execution of host commands.

### DMA Controller

The ADSP-21062's on-chip DMA controller allows zerooverhead data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simultaneously executing its program instructions.

DMA transfers can occur between the ADSP-21062's internal memory and either external memory, external peripherals or a host processor. DMA transfers can also occur between the ADSP-21062's internal memory and its serial ports or link ports. DMA transfers between external memory and external peripheral devices are another option. External bus packing to 16-, 32-, or 48-bit words is performed during DMA transfers.

Ten channels of DMA are available on the ADSP-21062—two via the link ports, four via the serial ports, and four via the processor's external port (for either host processor, other ADSP-21062s, memory or I/O transfers). Four additional link port DMA channels are shared with serial port 1 and the external port. Programs can be downloaded to the ADSP-21062 using DMA transfers. Asynchronous off-chip peripherals can control two DMA channels using DMA Request/Grant lines (DMAR1-2, DMAG1-2). Other DMA features

include interrupt generation upon completion of DMA transfers and DMA chaining for automatic linked DMA transfers.

### **Serial Ports**

The ADSP-21062 features two synchronous serial ports that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. The serial ports can operate at the full clock rate of the processor, providing each with a maximum data rate of 40 Mbit/s. Independent transmit and receive functions provide greater flexibility for serial communications. Serial port data can be automatically transferred to and from on-chip memory via DMA. Each of the serial ports offers TDM multichannel mode.

The serial ports can operate with little-endian or big-endian transmission formats, with word lengths selectable from 3 bits to 32 bits. They offer selectable synchronization and transmit modes as well as optional  $\mu$ -law or A-law companding. Serial port clocks and frame syncs can be internally or externally generated.

### Multiprocessing

The ADSP-21062 offers powerful features tailored to multiprocessor DSP systems. The unified address space (see Figure 4) allows direct interprocessor accesses of each ADSP-21062's internal memory. Distributed bus arbitration logic is included on-chip for simple, glueless connection of systems containing up to six ADSP-21062s and a host processor. Master processor changeover incurs only one cycle of overhead. Bus arbitration is selectable as either fixed or rotating priority. Bus lock allows indivisible *read-modify-write* sequences for semaphores. A vector interrupt is provided for interprocessor commands. Maximum throughput for interprocessor data transfer is 240 Mbytes/s over the link ports or external port. *Broadcast writes* allow simultaneous transmission of data to all ADSP-21062s and can be used to implement reflective semaphores.

### Link Ports

The ADSP-21062 features six 4-bit link ports that provide additional I/O capabilities. The link ports can be clocked twice per cycle, allowing each to transfer eight bits of data per cycle. Link port I/O is especially useful for point-to-point interprocessor communication in multiprocessing systems.

The link ports can operate independently and simultaneously, with a maximum data throughput of 240 Mbytes/s. Link port data is packed into 32- or 48-bit words, and can be directly read by the core processor or DMA-transferred to on-chip memory.

Each link port has its own double-buffered input and output registers. Clock/acknowledge handshaking controls link port transfers. Transfers are programmable as either transmit or receive.

### **Program Booting**

The internal memory of the ADSP-21062 can be booted at system power-up from either an 8-bit EPROM, a host processor, or through one of the link ports. Selection of the boot source is controlled by the BMS (Boot Memory Select), EBOOT (EPROM Boot), and LBOOT (Link/Host Boot) pins. 32-bit and 16-bit host processors can be used for booting.

Figure 3. Shared Memory Multiprocessing System

Figure 4. ADSP-21062/ADSP-21062L Memory Map

### **DEVELOPMENT TOOLS**

The ADSP-21062 is supported with a complete set of software and hardware development tools, including an EZ-ICE In-Circuit Emulator, EZ-LAB<sup>®</sup> development board, EZ-KIT, and development software. The EZ-LAB contains an evaluation board with an ADSP-21062 (5 V) processor and provides a serial connection to your PC. The SHARC EZ-KIT combines the ADSP-21000 Family Development Software for the PC and the EZ-LAB ADSP-21062's Development Board in one package. The EZ-KIT contains in addition to the EZ-LAB development board, an optimizing compiler, assembler, instruction level simulator, run-time libraries, diagnostic utilities and a complete set of example programs.

The same EZ-ICE hardware can be used for the ADSP-21060/ ADSP-21061, to fully emulate the ADSP-21062, with the exception of displaying and modifying the two new SPORTS registers. The emulator will not display these two registers, but your code can use them.

Analog Devices' ADSP-21000 Family Development Software includes an easy to use Assembler based on an algebraic syntax, an Assembly Library/Librarian, a Linker, an Instruction-level Simulator, an ANSI C optimizing Compiler, the CBug<sup>™</sup> C Source-Level Debugger, and a C Runtime Library including DSP and mathematical functions. The Optimizing Compiler includes Numerical C extensions based on the work of the ANSI Numerical C Extensions Group. Numerical C provides extensions to the C language for array selection, vector math operations, complex data types, circular pointers, and variably

CBug and SHARCPAC are trademarks of Analog Devices, Inc. EZ-LAB is a registered trademark of Analog Devices, Inc.

dimensioned arrays. The ADSP-21000 Family Development Software is available for both the PC and Sun platforms.

The ADSP-21062 EZ-ICE Emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-21062 processor to monitor and control the target board processor during emulation. The EZ-ICE provides full-speed emulation, allowing inspection and modification of memory, registers, and processor stacks. Nonintrusive in-circuit emulation is assured by the use of the processor's JTAG interface—the emulator does not affect target system loading or timing.

Further details and ordering information are available in the *ADSP-21000 Family Hardware & Software Development Tools* data sheet (ADDS-210xx-TOOLS). This data sheet can be requested from any Analog Devices sales office, distributor or the Literature Center.

In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the SHARC processor family. Hardware tools include SHARC PC plug-in cards, multiprocessor SHARC VME boards, and daughter card modules with multiple SHARCs and additional memory. These modules are based on the SHARCPAC<sup>™</sup> module specification. Third party software tools include an Ada compiler, DSP libraries, operating systems, and block diagram design tools.

### ADDITIONAL INFORMATION

This data sheet provides a general overview of the ADSP-21062 architecture and functionality. For detailed information on the ADSP-21000 Family core architecture and instruction set, refer to the ADSP-21062 SHARC User's Manual, Second Edition.

### PIN FUNCTION DESCRIPTIONS

ADSP-21062 pin definitions are listed below. All pins are identical on the ADSP-21062 and ADSP-21062L. Inputs identified as synchronous (S) must meet timing requirements with respect to CLKIN (or with respect to TCK for TMS, TDI). Inputs identified as asynchronous (A) can be asserted asynchronously to CLKIN (or to TCK for TRST).

Unused inputs should be tied or pulled to VDD or GND, except for ADDR<sub>31-0</sub>, DATA<sub>47-0</sub>, FLAG<sub>3-0</sub>,  $\overline{SW}$ , and inputs that have internal pull-up or pull-down resistors (CPA, ACK, DTx,

DRx, TCLKx, RCLKx, LxDAT3-0, LxCLK, LxACK, TMS and TDI)—these pins can be left floating. These pins have a logic-level hold circuit that prevents the input from floating internally.

| A = Asynchronous     | G = Ground                              | I = Input       |

|----------------------|-----------------------------------------|-----------------|

| O = Output           | P = Power Supply                        | S = Synchronous |

| (A/D) = Active Drive | (O/D) = Open Drain                      |                 |

| T = Three-State (whe | n $\overline{\text{SBTS}}$ is asserted, | or when the     |

| ADSP-21062 is a bus  | slave)                                  |                 |

| Pin                          | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR <sub>31-0</sub>         | I/O/T | <b>External Bus Address.</b> The ADSP-21062 outputs addresses for external memory and peripherals on these pins. In a multiprocessor system the bus master outputs addresses for read/writes of the internal memory or IOP registers of other ADSP-21062s. The ADSP-21062 inputs addresses when a host processor or multiprocessing bus master is reading or writing its internal memory or IOP registers.                                                                                                                                                                                                                                                                                                                                              |

| DATA <sub>47-0</sub>         | I/O/T | <b>External Bus Data</b> . The ADSP-21062 inputs and outputs data and instructions on these pins. 32-bit single-precision floating-point data and 32-bit fixed-point data is transferred over bits 47–16 of the bus. 40-bit extended-precision floating-point data is transferred over bits 47–8 of the bus. 16-bit short word data is transferred over bits 31–16 of the bus. In PROM boot mode, 8-bit data is transferred over bits 23–16. Pull-up resistors on unused DATA pins are not necessary.                                                                                                                                                                                                                                                   |

| $\overline{\text{MS}}_{3-0}$ | O/T   | <b>Memory Select Lines.</b> These lines are asserted (low) as chip selects for the corresponding banks of external memory. Memory bank size must be defined in the ADSP-21062's system control register (SYSCON). The $\overline{MS}_{3-0}$ lines are decoded memory address lines that change at the same time as the other address lines. When no external memory access is occurring the $\overline{MS}_{3-0}$ lines are inactive; they are active however when a conditional memory access instruction is executed, whether or not the condition is true. $\overline{MS}_0$ can be used with the PAGE signal to implement a bank of DRAM memory (Bank 0). In a multiprocessing system the $\overline{MS}_{3-0}$ lines are output by the bus master. |

| RD                           | I/O/T | <b>Memory Read Strobe</b> . This pin is asserted (low) when the ADSP-21062 reads from external memory devices or from the internal memory of other ADSP-21062s. External devices (including other ADSP-21062s) must assert $\overline{RD}$ to read from the ADSP-21062's internal memory. In a multiprocessing system $\overline{RD}$ is output by the bus master and is input by all other ADSP-21062s.                                                                                                                                                                                                                                                                                                                                                |

| WR                           | I/O/T | <b>Memory Write Strobe</b> . This pin is asserted (low) when the ADSP-21062 writes to external memory devices or to the internal memory of other ADSP-21062s. External devices must assert $\overline{WR}$ to write to the ADSP-21062's internal memory. In a multiprocessing system $\overline{WR}$ is output by the bus master and is input by all other ADSP-21062s.                                                                                                                                                                                                                                                                                                                                                                                 |

| PAGE                         | O/T   | <b>DRAM Page Boundary</b> . The ADSP-21062 asserts this pin to signal that an external DRAM page boundary has been crossed. DRAM page size must be defined in the ADSP-21062's memory control register (WAIT). DRAM can only be implemented in external memory Bank 0; the PAGE signal can only be activated for Bank 0 accesses. In a multiprocessing system PAGE is output by the bus master.                                                                                                                                                                                                                                                                                                                                                         |

| ADRCLK                       | O/T   | Clock Output Reference. In a multiprocessing system ADRCLK is output by the bus master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SW                           | I/O/T | <b>Synchronous Write Select</b> . This signal is used to interface the ADSP-21062 to synchronous memory devices (including other ADSP-21062s). The ADSP-21062 asserts $\overline{SW}$ (low) to provide an early indication of an impending write cycle, which can be aborted if $\overline{WR}$ is not later asserted (e.g., in a conditional write instruction). In a multiprocessing system, $\overline{SW}$ is output by the bus master and is input by all other ADSP-21062s to determine if the multiprocessor memory access is a read or write. $\overline{SW}$ is asserted at the same time as the address output. A host processor using synchronous writes must assert this pin when writing to the ADSP-21062(s).                             |

| ACK                          | I/O/S | <b>Memory Acknowledge</b> . External devices can deassert ACK (low) to add wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other peripherals to hold off completion of an external memory access. The ADSP-21062 deasserts ACK as an output to add wait states to a synchronous access of its internal memory. In a multiprocessing system, a slave ADSP-21062 deasserts the bus master's ACK input to add wait state(s) to an access of its internal memory. The bus master has a keeper latch on its ACK pin that maintains the input at the level to which it was last driven.                                                                                                                          |

REV. C

| Pin                      | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBTS                     | I/S   | Suspend Bus Three-State. External devices can assert SBTS (low) to place the external bus address,<br>data, selects and strobes in a high impedance state for the following cycle. If the ADSP-21062<br>attempts to access external memory while SBTS is asserted, the processor will halt and the memory<br>access will not be completed until SBTS is deasserted. SBTS should only be used to recover from host<br>processor/ADSP-21062 deadlock, or used with a DRAM controller.                                                                      |

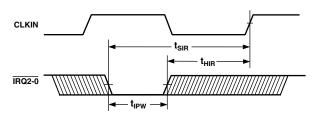

| $\overline{IRQ}_{2-0}$   | I/A   | Interrupt Request Lines. May be either edge-triggered or level-sensitive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FLAG <sub>3-0</sub>      | I/O/A | Flag Pins. Each is configured via control bits as either an input or output. As an input, they can be tested as a condition. As an output, they can be used to signal external peripherals.                                                                                                                                                                                                                                                                                                                                                              |

| TIMEXP                   | 0     | <b>Timer Expired</b> . Asserted for four cycles when the timer is enabled and TCOUNT decrements to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HBR                      | I/A   | <b>Host Bus Request</b> . This pin must be asserted by a host processor to request control of the ADSP-21062's external bus. When $\overline{\text{HBR}}$ is asserted in a multiprocessing system, the ADSP-21062 that is bus master will relinquish the bus and assert $\overline{\text{HBG}}$ . To relinquish the bus, the ADSP-21062 places the address, data, select and strobe lines in a high impedance state. $\overline{\text{HBR}}$ has priority over all ADSP-21062 bus requests ( $\overline{\text{BR}}_{6-1}$ ) in a multiprocessing system. |

| HBG                      | I/O   | <b>Host Bus Grant</b> . Acknowledges an $\overline{\text{HBR}}$ bus request, indicating that the host processor may take control of the external bus. $\overline{\text{HBG}}$ is asserted (held low) by the ADSP-21062 until $\overline{\text{HBR}}$ is released. In a multiprocessing system, $\overline{\text{HBG}}$ is output by the ADSP-21062 bus master and is monitored by all others.                                                                                                                                                            |

| $\overline{\mathrm{CS}}$ | I/A   | Chip Select. Asserted by host processor to select the ADSP-21062.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| REDY (O/D)               | 0     | <b>Host Bus Acknowledge</b> . The ADSP-21062 deasserts REDY (low) to add wait states to an asynchronous access of its internal memory or IOP registers by a host. This pin is an open drain output (O/D) by default; it can be programmed in the ADREDY bit of the SYSCON register to be active drive (A/D). REDY will only be output if the $\overline{CS}$ and $\overline{HBR}$ inputs are asserted.                                                                                                                                                   |

| DMAR1                    | I/A   | DMA Request 1 (DMA Channel 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DMAR2                    | I/A   | DMA Request 2 (DMA Channel 8).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DMAG1                    | O/T   | DMA Grant 1 (DMA Channel 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DMAG2                    | O/T   | DMA Grant 2 (DMA Channel 8).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BR <sub>6-1</sub>        | I/O/S | <b>Multiprocessing Bus Requests.</b> Used by multiprocessing ADSP-21062s to arbitrate for bus master-<br>ship. An ADSP-21062 only drives its own $\overline{BRx}$ line (corresponding to the value of its $ID_{2-0}$ inputs) and<br>monitors all others. In a multiprocessor system with less than six ADSP-21062s, the unused $\overline{BRx}$ pins<br>should be pulled high; the processor's own $\overline{BRx}$ line must not be pulled high or low because it is an<br>output.                                                                      |

| ID <sub>2-0</sub>        | Ι     | <b>Multiprocessing ID</b> . Determines which multiprocessing bus request $(\overline{BR1} - \overline{BR6})$ is used by ADSP-21062. ID = 001 corresponds to $\overline{BR1}$ , ID = 010 corresponds to $\overline{BR2}$ , etc. ID = 000 in single-processor systems. These lines are a system configuration selection which should be hardwired or changed at reset only.                                                                                                                                                                                |

| RPBA                     | I/S   | <b>Rotating Priority Bus Arbitration Select</b> . When RPBA is high, rotating priority for multiprocessor bus arbitration is selected. When RPBA is low, fixed priority is selected. This signal is a system configuration selection which must be set to the same value on every ADSP-21062. If the value of RPBA is changed during system operation, it must be changed in the same CLKIN cycle on every ADSP-21062.                                                                                                                                   |

| CPA (O/D)                | I/O   | <b>Core Priority Access.</b> Asserting its $\overline{CPA}$ pin allows the core processor of an ADSP-21062 bus slave to interrupt background DMA transfers and gain access to the external bus. $\overline{CPA}$ is an open drain output that is connected to all ADSP-21062s in the system. The $\overline{CPA}$ pin has an internal 5 k $\Omega$ pull-up resistor. If core access priority is not required in a system, the $\overline{CPA}$ pin should be left unconnected.                                                                           |

| DTx                      | 0     | <b>Data Transmit</b> (Serial Ports 0, 1). Each DT pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DRx                      | Ι     | <b>Data Receive</b> (Serial Ports 0, 1). Each DR pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TCLKx                    | I/O   | <b>Transmit Clock</b> (Serial Ports 0, 1). Each TCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RCLKx                    | I/O   | <b>Receive Clock</b> (Serial Ports 0, 1). Each RCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin                  | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TFSx                 | I/O    | Transmit Frame Sync (Serial Ports 0, 1).                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| RFSx                 | I/O    | Receive Frame Sync (Serial Ports 0, 1).                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| LxDAT <sub>3-0</sub> | I/O    | <b>Link Port Data</b> (Link Ports 0–5). Each LxDAT pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| LxCLK                | I/O    | <b>Link Port Clock</b> (Link Ports 0–5). Each LxCLK pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                        |  |  |  |  |  |

| LxACK                | I/O    | <b>Link Port Acknowledge</b> (Link Ports 0–5). Each LxACK pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                  |  |  |  |  |  |

| EBOOT                | Ι      | <b>EPROM Boot Select</b> . When EBOOT is high, the ADSP-21062 is configured for booting from an 8-<br>bit EPROM. When EBOOT is low, the LBOOT and BMS inputs determine booting mode. See table<br>below. This signal is a system configuration selection that should be hardwired.                                                                                                                                                |  |  |  |  |  |

| LBOOT                | Ι      | <b>Link Boot</b> . When LBOOT is high, the ADSP-21062 is configured for link port booting. When LBOOT is low, the ADSP-21062 is configured for host processor booting or no booting. See table below. This signal is a system configuration selection that should be hardwired.                                                                                                                                                   |  |  |  |  |  |

| BMS                  | I/O/T* | <b>Boot Memory Select</b> . <i>Output</i> : Used as chip select for boot EPROM devices (when EBOOT = 1, LBOOT = 0). In a multiprocessor system, $\overline{BMS}$ is output by the bus master. <i>Input</i> : When low, indicates that no booting will occur and that ADSP-21062 will begin executing instructions from external memory. See table below. This input is a system configuration selection that should be hardwired. |  |  |  |  |  |

|                      |        | *Three-statable only in EPROM boot mode (when $\overline{BMS}$ is an output).                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                      |        | EBOOT LBOOT BMS Booting Mode                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                      |        | 10OutputEPROM (Connect BMS to EPROM chip select.)001 (Input)Host Processor011 (Input)Link Port000 (Input)No Booting. Processor executes from external memory.010 (Input)Reserved11x (Input)Reserved                                                                                                                                                                                                                               |  |  |  |  |  |

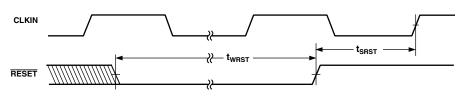

| CLKIN                | I      | <b>Clock In</b> . External clock input to the ADSP-21062. The instruction cycle rate is equal to CLKIN. CLKIN may not be halted, changed, or operated below the minimum specified frequency.                                                                                                                                                                                                                                      |  |  |  |  |  |

| RESET                | I/A    | <b>Processor Reset</b> . Resets the ADSP-21062 to a known state and begins program execution at the program memory location specified by the hardware reset vector address. This input must be asserted (low) at power-up.                                                                                                                                                                                                        |  |  |  |  |  |

| ТСК                  | I      | Test Clock (JTAG). Provides an asynchronous clock for JTAG boundary scan.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| TMS                  | I/S    | <b>Test Mode Select (JTAG)</b> . Used to control the test state machine. TMS has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| TDI                  | I/S    | <b>Test Data Input (JTAG)</b> . Provides serial data for the boundary scan logic. TDI has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| TDO                  | 0      | Test Data Output (JTAG). Serial scan output of the boundary scan path.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TRST                 | I/A    | <b>Test Reset (JTAG)</b> . Resets the test state machine. TRST must be asserted (pulsed low) after power-<br>up or held low for proper operation of the ADSP-21062. TRST has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                           |  |  |  |  |  |

| EMU                  | 0      | Emulation Status. Must be connected to the ADSP-21062 EZ-ICE target board connector only.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| ICSA                 | 0      | Reserved, leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| VDD                  | Р      | Power Supply; nominally +5.0 V dc for 5 V devices or +3.3 V dc for 3.3 V devices. (30 pins)                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| GND                  | G      | Power Supply Return. (30 pins)                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| NC                   |        | Do Not Connect. Reserved pins which must be left open and unconnected.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

### TARGET BOARD CONNECTOR FOR EZ-ICE PROBE

The ADSP-2106x EZ-ICE Emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-2106x to monitor and control the target board processor during emulation. The EZ-ICE probe requires the ADSP-2106x's CLKIN, TMS, TCK, TRST, TDI, TDO,  $\overline{EMU}$ , and GND signals be made accessible on the target system via a 14-pin connector (a  $2 \text{ row} \times 7$ pin strip header) such as that shown in Figure 5. The EZ-ICE probe plugs directly onto this connector for chip-on-board emulation. You must add this connector to your target board design if you intend to use the ADSP-2106x EZ-ICE. The total trace length between the EZ-ICE connector and the furthest device sharing the EZ-ICE JTAG pin should be limited to 15 inches maximum for guaranteed operation. This length restriction must include EZ-ICE JTAG signals that are routed to one or more ADSP-2106x devices, or a combination of ADSP-2106x devices and other JTAG devices on the chain.

Figure 5. Target Board Connector For ADSP-2106x EZ-ICE Emulator (Jumpers in Place)

The 14-pin, 2-row pin strip header is keyed at the Pin 3 location — Pin 3 must be removed from the header. The pins must be 0.025 inch square and at least 0.20 inch in length. Pin spacing should be  $0.1 \times 0.1$  inches. Pin strip headers are available from vendors such as 3M, McKenzie, and Samtec.

The BTMS, BTCK, BTRST, and BTDI signals are provided so that the test access port can also be used for board-level testing. When the connector is not being used for emulation, place jumpers between the BXXX pins and the XXX pins as shown in Figure 5. If you are not going to use the test access port for board testing, tie BTRST to GND and tie or pull up BTCK to VDD. The TRST pin must be asserted after power-up (through BTRST on the connector) or held low for proper operation of the ADSP-2106x. None of the BXXX pins (Pins 5, 7, 9, 11) are connected on the EZ-ICE probe.

The JTAG signals are terminated on the EZ-ICE probe as follows:

| Signal                                                | Termination                                           |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| TMS                                                   | Driven through 22 $\Omega$ Resistor (16 mA Driver)    |  |  |  |  |

| TCK                                                   | Driven at 10 MHz through 22 $\Omega$ Resistor (16 mA  |  |  |  |  |

| Driver)                                               |                                                       |  |  |  |  |

| TRST*                                                 | Active Low Driven through 22 $\Omega$ Resistor (16 mA |  |  |  |  |

| Driver) (Pulled Up by On-Chip 20 k $\Omega$ Resistor) |                                                       |  |  |  |  |

| TDI                                                   | Driven by 22 $\Omega$ Resistor (16 mA Driver)         |  |  |  |  |

| TDO                                                   | One TTL Load, Split Termination (160/220)             |  |  |  |  |

| CLKIN                                                 | One TTL Load, Split Termination (160/220)             |  |  |  |  |

| EMU                                                   | Active Low 4.7 kΩ Pull-Up Resistor, One TTL Load      |  |  |  |  |

| (Open-Drain Output from the DSP)                      |                                                       |  |  |  |  |

\*TRST is driven low until the EZ-ICE probe is turned on by the emulator at software start-up. After software start-up, TRST is driven high.

Figure 6. JTAG Scan Path Connections for Multiple ADSP-2106x Systems

Figure 6 shows JTAG scan path connections for systems that contain multiple ADSP-2106x processors.

Connecting CLKIN to Pin 4 of the EZ-ICE header is optional. The emulator only uses CLKIN when directed to perform operations such as starting, stopping, and single-stepping multiple ADSP-2106xs in a *synchronous* manner. If you do not need these operations to occur synchronously on the multiple processors, simply tie Pin 4 of the EZ-ICE header to ground.

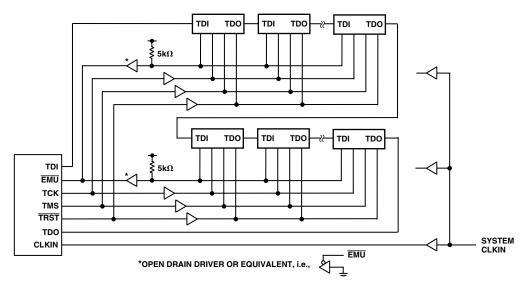

If synchronous multiprocessor operations are needed and CLKIN is connected, clock skew between the multiple ADSP-21062 processors and the CLKIN pin on the EZ-ICE header *must be minimal.* If the skew is too large, synchronous operations may be off by one or more cycles between processors. For synchronous multiprocessor operation TCK, TMS, CLKIN and **EMU** should be treated as critical signals in terms of skew, and should be laid out as short as possible on your board. If TCK, TMS, and CLKIN are driving a large number of ADSP-21062s (more than eight) in your system, then treat them as a "clock tree" using multiple drivers to minimize skew. (See Figure 7 "JTAG Clock Tree" and "Clock Distribution" in the "High Frequency Design Considerations" section of the *ADSP*-2106x User's Manual, Second Edition.)

If synchronous multiprocessor operations are not needed (i.e., CLKIN is not connected), just use appropriate parallel termination on TCK and TMS. TDI, TDO, EMU and TRST are not critical signals in terms of skew.

For complete information on the SHARC EZ-ICE, see the ADSP-21000 Family JTAG EZ-ICE User's Guide and Reference.

Figure 7. JTAG Clocktree for Multiple ADSP-2106x Systems

# ADSP-21062—SPECIFICATIONS **RECOMMENDED OPERATING CONDITIONS (5 V)**

|                     |                                         |                                   | A Grade |                | C Grade |                | K Grade |                |       |

|---------------------|-----------------------------------------|-----------------------------------|---------|----------------|---------|----------------|---------|----------------|-------|

| Parameter           |                                         | Test Conditions                   | Min     | Max            | Min     | Max            | Min     | Max            | Units |

| $\overline{V_{DD}}$ | Supply Voltage                          |                                   | 4.75    | 5.25           | 4.75    | 5.25           | 4.75    | 5.25           | V     |

| $T_{CASE}$          | Case Operating Temperature              |                                   | -40     | +85            | -40     | +100           | 0       | +85            | °C    |

| $V_{IH1}$           | High Level Input Voltage <sup>1</sup>   | $@V_{DD} = max$                   | 2.0     | $V_{DD} + 0.5$ | 2.0     | $V_{DD} + 0.5$ | 2.0     | $V_{DD} + 0.5$ | V     |

| $V_{IH2}$           | High Level Input Voltage <sup>2</sup>   | $(a) V_{DD} = max$                | 2.2     | $V_{DD} + 0.5$ | 2.2     | $V_{DD} + 0.5$ | 2.2     | $V_{DD} + 0.5$ | V     |

| V <sub>IL</sub>     | Low Level Input Voltage <sup>1, 2</sup> | $\tilde{@}$ V <sub>DD</sub> = min | -0.5    | 0.8            | -0.5    | 0.8            | -0.5    | 0.8            | V     |

NOTES

<sup>1</sup>Applies to input and bidirectional pins: DATA<sub>47-0</sub>, ADDR<sub>31-0</sub>,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $\overline{\text{SW}}$ , ACK,  $\overline{\text{SBTS}}$ ,  $\overline{\text{IRQ}}_{2-0}$ ,  $\overline{\text{FLAG}}_{3-0}$ ,  $\overline{\text{HBG}}$ ,  $\overline{\text{CS}}$ ,  $\overline{\text{DMAR1}}$ ,  $\overline{\text{DMAR2}}$ ,  $\overline{\text{BR}}_{6-1}$ ,  $\text{ID}_{2-0}$ , RPBA,  $\overline{\text{CPA}}$ , TFS0, TFS1, RFS0, RFS1,  $\underline{\text{LxDAT}}_{3-0}$ ,  $\underline{\text{LxCLK}}$ , LxACK, EBOOT, LBOOT,  $\overline{\text{BMS}}$ , TMS, TDI, TCK,  $\overline{\text{HBR}}$ , DR0, DR1, TCLK0, TCLK1, RCLK0, RCLK1. <sup>2</sup>Applies to input pins: CLKIN, RESET, TRST.

### **ELECTRICAL CHARACTERISTICS (5 V)**

| Paramet            | er                                                | Test Conditions                                                                    | Min | Max | Units |

|--------------------|---------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|-------|

| V <sub>OH</sub>    | High Level Output Voltage <sup>1</sup>            | (a) $V_{DD}$ = min, $I_{OH}$ = -2.0 mA <sup>2</sup>                                | 4.1 |     | V     |

| VOL                | Low Level Output Voltage <sup>1</sup>             | $\hat{a}$ , V <sub>DD</sub> = min, I <sub>OL</sub> = 4.0 mA <sup>2</sup>           |     | 0.4 | V     |

| $I_{IH}$           | High Level Input Current <sup>3, 4</sup>          | $\hat{a}$ , $V_{DD}$ = max, $V_{IN}$ = $V_{DD}$ max                                |     | 10  | μA    |

| $I_{IL}$           | Low Level Input Current <sup>3</sup>              | $\hat{a}$ V <sub>DD</sub> = max, V <sub>IN</sub> = 0 V                             |     | 10  | μA    |

| I <sub>ILP</sub>   | Low Level Input Current <sup>4</sup>              | $\overset{\frown}{a}$ V <sub>DD</sub> = max, V <sub>IN</sub> = 0 V                 |     | 150 | μA    |

| I <sub>OZH</sub>   | Three-State Leakage Current <sup>5, 6, 7, 8</sup> | $\hat{a}$ , $V_{DD}$ = max, $V_{IN}$ = $V_{DD}$ max                                |     | 10  | μA    |

| I <sub>OZL</sub>   | Three-State Leakage Current <sup>5, 9</sup>       | $\hat{a}$ , $V_{DD} = max$ , $V_{IN} = 0$ V                                        |     | 10  | μA    |

| I <sub>OZHP</sub>  | Three-State Leakage Current <sup>9</sup>          | $\overset{\frown}{@}$ V <sub>DD</sub> = max, V <sub>IN</sub> = V <sub>DD</sub> max |     | 350 | μA    |

| I <sub>OZLC</sub>  | Three-State Leakage Current <sup>7</sup>          | $\tilde{a}$ , $V_{DD} = \max$ , $V_{IN} = 0$ V                                     |     | 1.5 | mA    |

| I <sub>OZLA</sub>  | Three-State Leakage Current <sup>10</sup>         | $(a) V_{DD} = max, V_{IN} = 1.5 V$                                                 |     | 350 | μA    |

| I <sub>OZLAR</sub> | Three-State Leakage Current <sup>8</sup>          | $\tilde{a}$ , $V_{DD} = \max$ , $V_{IN} = 0$ V                                     |     | 4.2 | mA    |

| I <sub>OZLS</sub>  | Three-State Leakage Current <sup>6</sup>          | $\overset{\frown}{a}$ V <sub>DD</sub> = max, V <sub>IN</sub> = 0 V                 |     | 150 | μA    |

| C <sub>IN</sub>    | Input Capacitance <sup>11, 12</sup>               | $f_{IN} = 1$ MHz, $T_{CASE} = 25^{\circ}C$ , $V_{IN} = 2.5$ V                      |     | 4.7 | pF    |

NOTES

$\frac{1}{A}$  Applies to output and bidirectional pins: DATA<sub>47-0</sub>, ADDR<sub>31-0</sub>,  $\overline{MS}_{3-0}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , PAGE, ADRCLK,  $\overline{SW}$ , ACK, FLAG<sub>3-0</sub>, TIMEXP,  $\overline{HBG}$ , REDY,  $\overline{DMAG1}$ ,  $\overline{DMAG2}$ ,  $\overline{BR}_{6-1}$ ,  $\overline{CPA}$ , DT0, DT1, TCLK0, TCLK1, RCLK0, RCLK1, TFS0, TFS1, RFS0, RFS1, LxDAT<sub>3-0</sub>, LxCLK, LxACK,  $\overline{BMS}$ , TD0,  $\overline{EMU}$ , ICSA. <sup>2</sup>See "Output Drive Currents" for typical drive current capabilities.

<sup>3</sup>Applies to input pins: ACK <u>SBTS</u>, <u>IRQ</u><sub>2-0</sub>, <u>HBR</u>, <u>CS</u>, <u>DMAR1</u>, <u>DMAR2</u>, ID<sub>2-0</sub>, RPBA, EBOOT, LBOOT, CLKIN, <u>RESET</u>, TCK. <sup>4</sup>Applies to input pins with internal pull-ups: DR0, DR1, <u>TRST</u>, TMS, TDI. <sup>5</sup>Applies to three-statable pins: DATA<sub>47-0</sub>, <u>ADDR</u><sub>31-0</sub>, <u>MS</u><sub>3-0</sub>, <u>RD</u>, <u>WR</u>, PAGE, <u>ADRCLK</u>, <u>SW</u>, ACK, FLAG<sub>3-0</sub>, <u>REDY</u>, <u>HBG</u>, <u>DMAG1</u>, <u>DMAG2</u>, <u>BMS</u>, <u>BR</u><sub>6-1</sub>,  $TFS_x$ , RFS<sub>x</sub>, TDO, EMU. (Note that ACK is pulled up internally with 2 k $\Omega$  during reset in a multiprocessor system, when ID<sub>2-0</sub> = 001 and another ADSP-21062 is not requesting bus mastership.)

<sup>6</sup>Applies to three-statable pins with internal pull-ups: DT0, DT1, TCLK0, TCLK1, RCLK0, RCLK1.

<sup>7</sup>Applies to  $\overline{CPA}$  pin.

<sup>8</sup>Applies to ACK pin when pulled up. (Note that ACK is pulled up internally with 2 k $\Omega$  during reset in a multiprocessor system, when ID<sub>2-0</sub> = 001 and another ADSP-21062L is not requesting bus mastership).

<sup>9</sup>Applies to three-statable pins with internal pull-downs: LxDAT<sub>3-0</sub>, LxCLK, LxACK.

<sup>10</sup>Applies to ACK pin when keeper latch enabled.

<sup>11</sup>Applies to all signal pins.

<sup>12</sup>Guaranteed but not tested.

Specifications subject to change without notice.

### POWER DISSIPATION ADSP-21062 (5 V)

These specifications apply to the internal power portion of  $V_{DD}$  only. See the Power Dissipation section of this data sheet for calculation of external supply current and total supply current. For a complete discussion of the code used to measure power dissipation, see the technical note "SHARC Power Dissipation Measurements."

Specifications are based on the following operating scenarios:

| Operation           | Peak Activity (I <sub>DDINPEAK</sub> ) | High Activity (I <sub>DDINHIGH</sub> ) | Low Activity (I <sub>DDINLOW</sub> ) |  |  |

|---------------------|----------------------------------------|----------------------------------------|--------------------------------------|--|--|

| Instruction Type    | Multifunction                          | Multifunction                          | Single Function                      |  |  |

| Instruction Fetch   | Cache                                  | Internal Memory                        | Internal Memory                      |  |  |

| Core Memory Access  | 2 per Cycle (DM and PM)                | 1 per Cycle (DM)                       | None                                 |  |  |

| Internal Memory DMA | 1 per Cycle                            | 1 per 2 Cycles                         | 1 per 2 Cycles                       |  |  |

To estimate power consumption for a specific application, use the following equation where % is the amount of time your program spends in that state:

$\% PEAK \times I_{DDINPEAK} + \% HIGH \times I_{DDINHIGH} + \% LOW \times I_{DDINLOW} + \% IDLE \times I_{DDIDLE} = power \ consumption$

| Parameter             |                                        | Test Conditions                         | Max | Units |

|-----------------------|----------------------------------------|-----------------------------------------|-----|-------|

| I <sub>DDINPEAK</sub> | Supply Current (Internal) <sup>1</sup> | $t_{CK} = 30 \text{ ns}, V_{DD} = \max$ | 745 | mA    |

|                       |                                        | $t_{CK}$ = 25 ns, $V_{DD}$ = max        | 850 | mA    |

| I <sub>DDINHIGH</sub> | Supply Current (Internal) <sup>2</sup> | $t_{CK}$ = 30 ns, $V_{DD}$ = max        | 575 | mA    |

|                       |                                        | $t_{CK} = 25 \text{ ns}, V_{DD} = \max$ | 670 | mA    |

| IDDINLOW              | Supply Current (Internal) <sup>2</sup> | $t_{CK}$ = 30 ns, $V_{DD}$ = max        | 340 | mA    |

|                       |                                        | $t_{CK}$ = 25 ns, $V_{DD}$ = max        | 390 | mA    |

| I <sub>DDIDLE</sub>   | Supply Current (Idle) <sup>3</sup>     | $V_{DD} = max$                          | 200 | mA    |

NOTES

<sup>1</sup>The test program used to measure I<sub>DDINPEAK</sub> represents worst case processor operation and is not sustainable under normal application conditions. Actual internal power measurements made using typical applications are less than specified.

<sup>2</sup>I<sub>DDINHIGH</sub> is a composite average based on a range of high activity code. I<sub>DDINLOW</sub> is a composite average based on a range of low activity code.

<sup>3</sup>Idle denotes ADSP-21062L state during execution of IDLE instruction.

# ADSP-21062L—SPECIFICATIONS **RECOMMENDED OPERATING CONDITIONS (3.3 V)**

|                 |                                         |                           | A Grade |                | C Grade |                | K Grade |                |       |

|-----------------|-----------------------------------------|---------------------------|---------|----------------|---------|----------------|---------|----------------|-------|

| Parameter       |                                         | Test Conditions           | Min     | Max            | Min     | Max            | Min     | Max            | Units |

| V <sub>DD</sub> | Supply Voltage                          |                           | 3.15    | 3.45           | 3.15    | 3.45           | 3.15    | 3.45           | V     |

| $T_{CASE}$      | Case Operating Temperature              |                           | -40     | +85            | -40     | +100           | 0       | +85            | °C    |

| $V_{IH1}$       | High Level Input Voltage <sup>1</sup>   | $@V_{DD} = max$           | 2.0     | $V_{DD} + 0.5$ | 2.0     | $V_{DD} + 0.5$ | 2.0     | $V_{DD} + 0.5$ | V     |

| $V_{IH2}$       | High Level Input Voltage <sup>2</sup>   | (a) V <sub>DD</sub> = max | 2.2     | $V_{DD} + 0.5$ | 2.2     | $V_{DD} + 0.5$ | 2.2     | $V_{DD} + 0.5$ | V     |

| VIL             | Low Level Input Voltage <sup>1, 2</sup> | $@V_{DD} = min$           | -0.5    | 0.8            | -0.5    | 0.8            | -0.5    | 0.8            | V     |

NOTES

<sup>1</sup>Applies to input and bidirectional pins: DATA<sub>47-0</sub>, ADDR<sub>31-0</sub>,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $\overline{\text{SW}}$ , ACK,  $\overline{\text{SBTS}}$ ,  $\overline{\text{IRQ}}_{2-0}$ , FLAG<sub>3-0</sub>,  $\overline{\text{HBG}}$ ,  $\overline{\text{CS}}$ ,  $\overline{\text{DMAR1}}$ ,  $\overline{\text{DMAR2}}$ ,  $\overline{\text{BR}}_{6-1}$ ,  $\text{ID}_{2-0}$ , RPBA,  $\overline{\text{CPA}}$ , TFS0, TFS1, RFS0, RFS1, LxDAT<sub>3-0</sub>, LxCLK, LxACK, EBOOT, LBOOT,  $\overline{\text{BMS}}$ , TMS, TDI, TCK,  $\overline{\text{HBR}}$ , DR0, DR1, TCLK0, TCLK1, RCLK0, RCLK1. <sup>2</sup>Applies to input pins: CLKIN, RESET, TRST.

### **ELECTRICAL CHARACTERISTICS (3.3 V)**

| Paramete           | er                                                | Test Conditions                                                                    | Min | Max | Units |

|--------------------|---------------------------------------------------|------------------------------------------------------------------------------------|-----|-----|-------|

| V <sub>OH</sub>    | High Level Output Voltage <sup>1</sup>            | (a) $V_{DD}$ = min, $I_{OH}$ = -2.0 mA <sup>2</sup>                                | 2.4 |     | V     |

| V <sub>OL</sub>    | Low Level Output Voltage <sup>1</sup>             | $\tilde{a}$ V <sub>DD</sub> = min, I <sub>OL</sub> = 4.0 mA <sup>2</sup>           |     | 0.4 | V     |

| I <sub>IH</sub>    | High Level Input Current <sup>3, 4</sup>          | $\hat{a}$ $V_{DD}^{}$ = max, $V_{IN}^{-}$ = $V_{DD}$ max                           |     | 10  | μA    |

| I <sub>IL</sub>    | Low Level Input Current <sup>3</sup>              | $\hat{a}_{\rm VDD} = \max_{\rm VIN} = 0$ V                                         |     | 10  | μA    |