**ASI 3560A**

# Contents

| Page          | Section           | Title                                                                  |

|---------------|-------------------|------------------------------------------------------------------------|

| <b>4</b><br>4 | <b>1.</b><br>1.1. | Introduction<br>Features                                               |

| 5             | 2.                | Functional Description                                                 |

| 5             | 2.1.              | Architecture of the ASI 3560A                                          |

| 6             | 2.2.<br>2.2.1.    | Synchronization to the Video Stream                                    |

| 6<br>6        | 2.2.1.            | Synchronization to Vref and Href Synchronization to the SAV/EAV Header |

| 9             | 2.2.2.            | Ancillary Data Format                                                  |

| 9             | 2.4.              | Data Transmission Format                                               |

| 10            | 2.5.              | Reset / Standby-Mode / Operation Mode                                  |

| 11            | 2.6.              | FIFO and Output Controlling                                            |

| 11            | 2.7.              | Video Stream Interface                                                 |

| 11            | 2.8.              | I <sup>2</sup> S Interface                                             |

| 12            | 2.9.              | JTAG Boundary-Scan, Test Access Port (TAP)                             |

| 12            | 2.9.1.            | General Description                                                    |

| 12            | 2.9.2.            | TAP Architecture                                                       |

| 12            | 2.9.2.1.          | TAP Controller                                                         |

| 12            | 2.9.2.2.          | Instruction Register                                                   |

| 12            | 2.9.2.3.          | Boundary Scan Register                                                 |

| 13            | 2.9.2.4.          | Bypass Register                                                        |

| 13            | 2.9.2.5.          | Device Identification Register                                         |

| 13            | 2.9.2.6.          | Master Mode Data Register                                              |

| 13            | 2.9.3.            | IEEE 1149.1-1990 Spec Adherence                                        |

| 13            | 2.9.3.1.          | Instruction Register                                                   |

| 13            | 2.9.3.2.          | Public Instructions                                                    |

| 13            | 2.9.3.3.          | Self-Test Operation                                                    |

| 13            | 2.9.3.4.          | Test Data Registers                                                    |

| 14            | 2.9.3.5.          | Boundary Scan Register                                                 |

| 14            | 2.9.3.6.          | Device Identification Register                                         |

| 16            | 2.9.3.7.          | Performance                                                            |

| 16            | 2.10.             | Enable/Disable of Output Signals                                       |

| 17            | 3.                | I <sup>2</sup> C Bus Interface                                         |

| 17            | 3.1.              | Protocol Description                                                   |

| 18            | 3.2.              | Control Registers                                                      |

| 20            | 4.                | Specifications                                                         |

| 20            | 4.1.              | Outline Dimensions                                                     |

| 20            | 4.2.              | Pin Connections and Short Descriptions                                 |

| 22            | 4.3.              | Pin Descriptions                                                       |

| 23            | 4.4.              | Pin Configuration                                                      |

| 24            | 4.5.              | Pin Circuits                                                           |

| 25            | 4.6.              | Electrical Characteristics                                             |

| 25            | 4.6.1.            | Absolute Maximum Ratings                                               |

| 25            | 4.6.2.            | Recommended Operating Conditions                                       |

| 26            | 4.6.3.            | Recommended I <sup>2</sup> S Conditions                                |

| 26            | 4.6.4.            | Recommended I <sup>2</sup> C Conditions                                |

# Contents, continued

| Page | Section  | Title                                                                                      |

|------|----------|--------------------------------------------------------------------------------------------|

| 26   | 4.6.5.   | Recommended Digital Inputs Levels of HREF, VREF, A[7:0], LLC, I2S_xxx, RESQ, TCK, TMS, TDI |

| 27   | 4.7.     | Characteristics                                                                            |

| 27   | 4.7.1.   | Current Consumption                                                                        |

| 27   | 4.7.2.   | Characteristics, Reset                                                                     |

| 27   | 4.7.3.   | Characteristics, Control Bus Interface                                                     |

| 28   | 4.7.4.   | Characteristics, JTAG Interface (Test Access Port TAP)                                     |

| 29   | 4.7.5.   | Characteristics, Digital Inputs/Outputs                                                    |

| 29   | 4.7.6.   | Clock Signal LLC                                                                           |

| 30   | 4.7.7.   | Digital Video Interface                                                                    |

| 30   | 4.7.8.   | Characteristics, TTL Output Driver                                                         |

| 30   | 4.7.8.1. | TTL Output Driver Type A                                                                   |

| 31   | 4.7.8.2. | TTL Output Driver OEQ                                                                      |

| 33   | 4.8.     | Timing Diagrams                                                                            |

| 33   | 4.8.1.   | Power-Up Sequence                                                                          |

| 33   | 4.8.2.   | Control Bus Timing Diagram                                                                 |

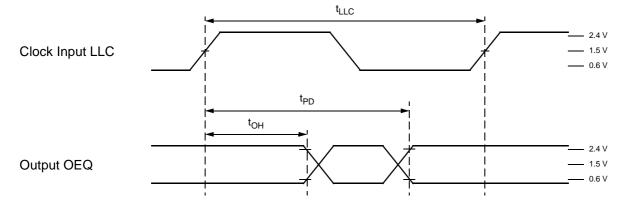

| 34   | 4.8.3.   | Output Enable by Pin OEQ                                                                   |

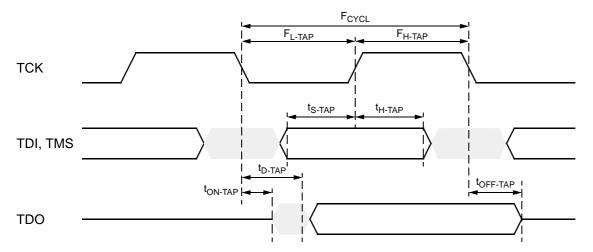

| 34   | 4.8.4.   | Timing of the Test Access Port TAP                                                         |

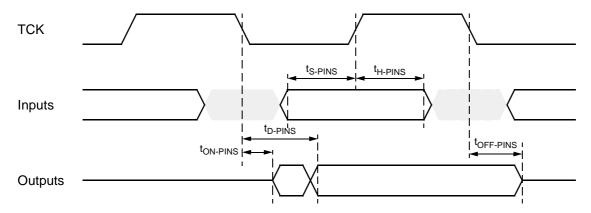

| 34   | 4.8.5.   | IO-Timing of all Pins connected to the Boundary-Scan-Register-Chain                        |

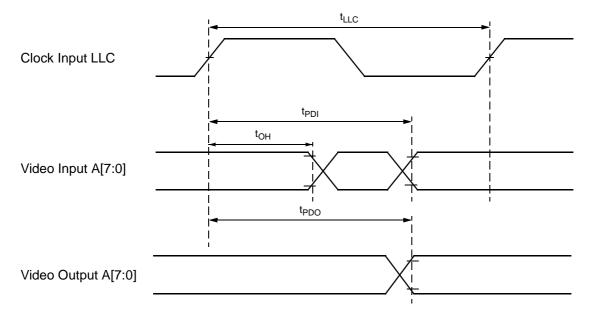

| 35   | 4.8.6.   | Timing Diagram of the Digital Video Interface                                              |

| 35   | 4.8.7.   | Timing Diagram of the I <sup>2</sup> S Interface                                           |

| 36   | 5.       | Data Sheet History                                                                         |

#### **Audio Stream Interface**

#### 1. Introduction

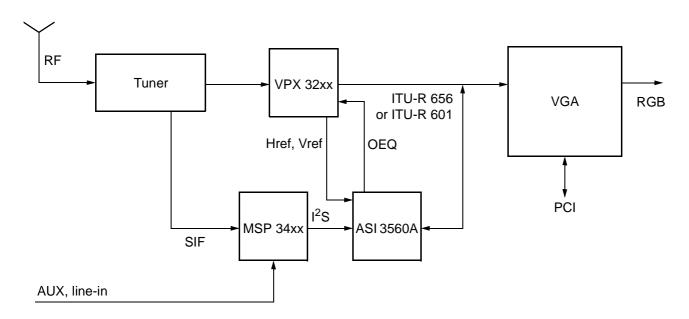

The ASI 3560A audio stream interface offers the integration of digital audio data into a digital component video stream. Combined with a video decoder of the VPX 32xx family and an audio demodulator of the MSP 34xx family, the generated output stream contains video, audio, and VBI data (e.g. teletext, intercast, etc.). This configuration enables single-board plug-and-play tuner cards without extra wiring of audio signals.

Since the ASI 3560A multiplexes arbitrary serial data into a video stream, it is generally applicable and not limited to audio data.

## 1.1. Features

- guarantees synchronized digital video and audio

- I<sup>2</sup>S interface for audio data (Sony and Philips format)

- transmission as horizontal or vertical ancillary data possible

- fully programmable audio window within the video stream

- sample rates up to 32 kHz with 16-bit stereo during transmission in the vertical blank interval.

- sample rates up to 48 kHz with 16-bit stereo during transmission in the horizontal blank interval.

- compliant to ITU-R 601-5 video stream format

- compliant to ITU-R 656-3 video stream format

- controlling via I<sup>2</sup>C interface

- IEEE 1149.1 (JTAG) boundary scan interface

- low-power / stand-by mode

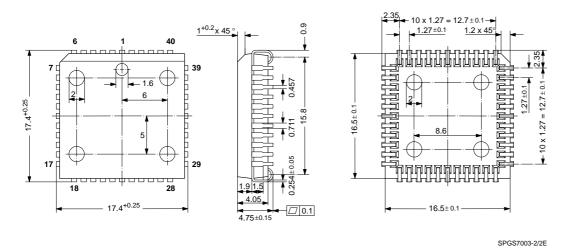

- 44-pin PLCC package

Fig. 1-1: Application example

### 2. Functional Description

#### 2.1. Architecture of the ASI 3560A

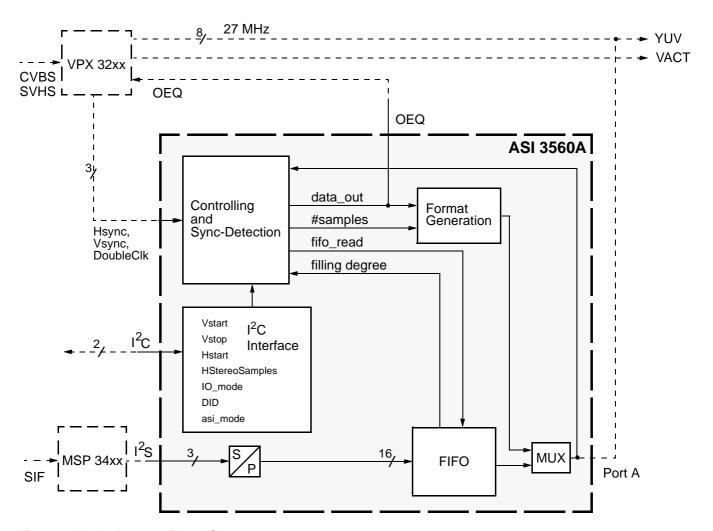

The principal task of the ASI 3560A is to buffer incoming serial digital data in a FIFO and multiplex them blockwise into a digital video component stream during the vertical or horizontal blanking interval (VBI, HBI), when no video data is transmitted. Figure 2–1 shows a simplified block diagram of the IC architecture.

The Sync-Detection unit determines the actual position within the stream by evaluating the video reference signals (ITU-R 601 mode) or scanning the video bus itself for sync information (ITU-R 656 mode).

The control unit detects the reaching of the programmed audio window, disables the video decoder output, and initiates the writing of the FIFO data to the bus.

Since the data block format is compliant to the ITU-R 656 specification, every data packet is preceded with a header and followed by a checksum, which is generated by a Format Generation block.

The configuration of the interfaces, the positioning of the data window, and most parts of the transmission format face.

Fig. 2-1: Block diagram of the ASI 3560A

## 2.2. Synchronization to the Video Stream

The ASI 3560A is capable of dealing with the following video stream formats:

- YUV 4:2:2, ITU-R 601-5, 8 bit, double clock

- YUV 4:2:2, ITU-R 656-3

Although the generated data outputs are identical, the determination of the window position is completely different for both standards. While the ITU-R 601-5 specification uses additional signals to transmit the syncinformation, the ITU-R 656-3 recommendation inserts sync information in the video stream itself and thus reduces the necessary number of wires.

The ASI 3560A begins with the output of an ancillary header, followed by audio data, if the internal line counter is within the values of the I<sup>2</sup>C-registers 'VStart' and 'VStop' and the pixel counter reaches the value of the 'HStart' register.

The internal counters are reset with the related syncinformation: reference signals or headers. Therefore, the absolute window position within the video stream determined by the I<sup>2</sup>C registers ('VStart', 'VStop', HStart', and 'HStereoSamples') depends on the selected sync-mode.

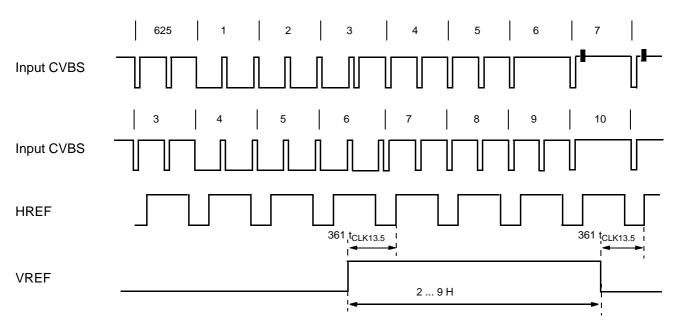

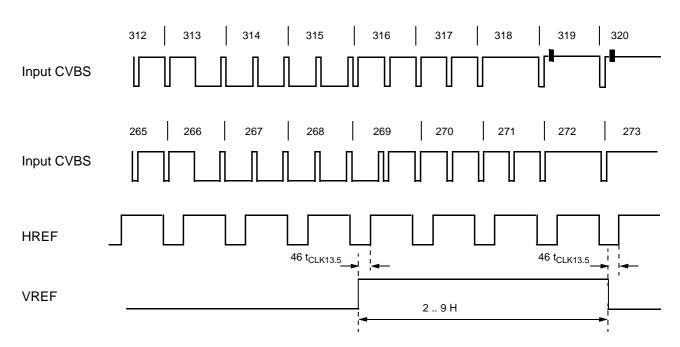

## 2.2.1. Synchronization to Vref and Href

If bit[5] of the 'IO\_mode' register (see Table 3–2 on page 18) is zero, the ASI 3560A determines the audio window position relative to the Vref and Href signals of an ITU-R 601 compliant video interface. The internal counters are reset with the first slope of the regarded reference signal. For proper detection, the polarity of the reference signals has to be specified with bits[0:1] of the 'IO\_mode' register.

For video conferencing applications, a selection of the field is possible indicated by bit[8:7] of the 'IO\_mode'-register. The field is identified by the relation between Vref and Href as depicted in Figure 2–2 and Figure 2–3

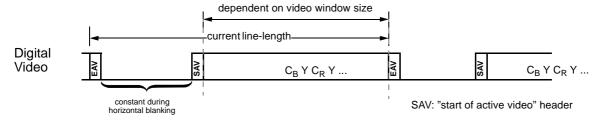

## 2.2.2. Synchronization to the SAV/EAV Header

If bit[5] of the 'IO\_mode' register (see Table 3–2 on page 18) is set to "1", the ASI 3560A determines the audio window position by evaluating the V- and H-flag of the SAV (bit[6] = 0) or the EAV (bit[6] = 1) headers of an ITU-R 656 data stream (see Table 2–1 on page 8). The internal line counter is reset to zero with every V-flag equal to "1". The pixel counter starts counting from zero if the H-flag equals bit[6] of the 'IO\_mode' register. The upper left corner of the audio window is reached when these internal counters equal the registers 'VStart' and 'HStart'.

For video conferencing applications, a selection of the field is possible indicated by bit[8:7] of the 'IO\_mode'-register. The field is identified by evaluating the F-Flag in the SAV and EAV header, respectively, and data packets are inserted only in the selected field.

Fig. 2-2: Expected VREF timing for ODD fields

Fig. 2-3: Expected VREF timing for EVEN fields

Fig. 2-4: Component video stream with embedded reference headers (according to ITU-R656)

Fig. 2-5: Detailed video stream

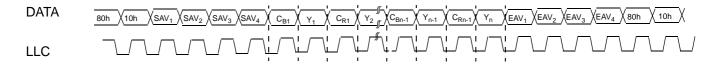

Fig. 2-6: Insertion of ancillary data in the VBI

Table 2–1: Coding of SAV/EAV-header (ITU-R 656 specification)

| words  | bit 9 | bit 8 | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| First  | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| Second | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Third  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Fourth | 1     | F     | V     | Н     | P5    | P4    | P3    | P2    |

\$FF

\$00 \$00

Compa informació

F = 0 during field 1

F = 1 during field 2

Sync information

V = 0 elsewhere

V = 1 during vertical field blanking

P2, P3, P4, and P5 are protection bits, which are not regarded by the

H = 0 in SAV

H = 1 in EAV

ASI 3560A

Table 2–2: Coding of the ancillary header (compliant to ITU-R 656-3 recommendation)

| words  | bit 9 | bit 8          | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 |

|--------|-------|----------------|-------|-------|-------|-------|-------|-------|

| First  | 0     | 0              | 0     | 0     | 0     | 0     | 0     | 0     |

| Second | 1     | 1              | 1     | 1     | 1     | 1     | 1     | 1     |

| Third  | 1     | 1              | 1     | 1     | 1     | 1     | 1     | 1     |

| Fourth | bit 8 | even<br>parity | T7    | Т6    | T5    | T4    | Т3    | T2    |

| Fifth  | bit 8 | even<br>parity | N7    | N6    | N5    | N4    | N3    | N2    |

| Sixth  | bit 8 | even<br>parity | C7    | C6    | C5    | C4    | C3    | C2    |

\$00

\$FF

\$FF

Data ID (programmable)

Data Block Number (DBN)

Data Count (DC)

### 2.3. Ancillary Data Format

Ancillary packets are transferred compliant to the draft recommendation ITU-R BT.[11-2/AD] with the following extensions:

- Ancillary data blocks may be longer than 255 bytes INTERMETALL extended mode, see Table 3–2)

- Ancillary data packets must not follow immediately after EAV or SAV.

The ASI 3560A always generates an ancillary header for each line, which is compliant to the ITU-R 656 video stream format, even in ITU-R 601 mode. The coding of the headers is depicted in Table 2–2.

If the VGA controller cannot deal with ancillary data packets, audio data can be transmitted together with video data in the active video interval. Therefore, the preamble \$00 FF FF can be modified to \$80 7F 7F with bit[2] of the 'IO\_mode' register, which assures correct SAV/EAV-detection.

The 8-bit (incl. parities!) of the Data ID (DID) are programmable to enable the user the freedom of specifying his serial data compliant to any future recommendation.

The Data Block Number (DBN) counts the ancillary data packets if its value is not forced to zero (which means \$80 with parities) with bit[3] of the 'IO\_mode' register (see Table 3–2 on page 18).

The Data Count (DC) word depends on the setting of bit[4] of the 'IO\_mode' register. If it is set to zero, the DC determines the number of following DWords (32 bit = 4 cycles) compliant to the ITU-R 656-3 recommendation and is therefore limited to 255 User Data Words (UDW). In order to allow the usage of longer packets, a so-called INTERMETALL extended mode may be used by setting bit[4] to one. In this case, the whole 8 bit represents the number of 6 byte packets, which equals the number of stereo samples. Please note that there are no longer any parities transmitted.

A successive checksum is added behind the audio data packages, which are transmitted in a format described in section 2.4. The checksum consists of the sum of the seven LSBs of DID, DBN, DC, and all UDWs (user data words) within the modulo range of 7 bit. Since the ASI 3560A supports only an 8-bit protocol, the checksum means the modulo addition of the bits 2..8 concerning the 10-bit ITU-R656 specification.

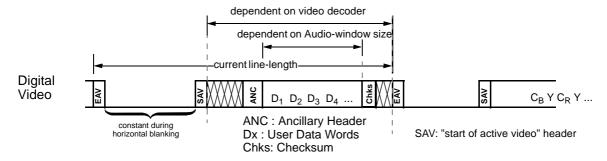

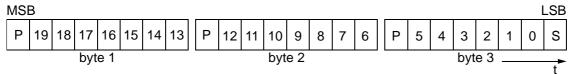

#### 2.4. Data Transmission Format

The audio data is transferred in 6-byte packages, each containing one stereo sample. The protocol has been designed for 20-bit audio data (see Figure 2–7). The audio samples are always MSB aligned, which means a 16-bit sample is transferred in bit 4-19. The ASI status flag allows the user to determine problems without polling the I2C register 'asi\_mode'.

P: odd parity (the number of ones in the whole byte is odd),

S: ASI status flag (0: data valid, 1: error / read asi\_mode register for further information)

Fig. 2-7: Transmission format of the audio data

**ASI 3560A**

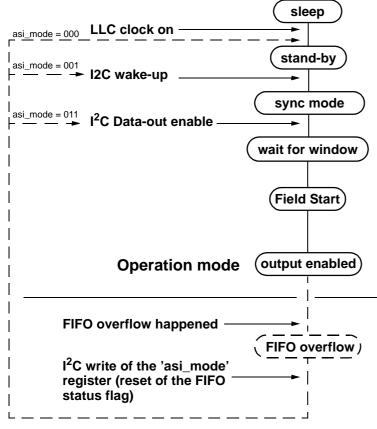

#### 2.5. Reset / Standby-Mode / Operation Mode

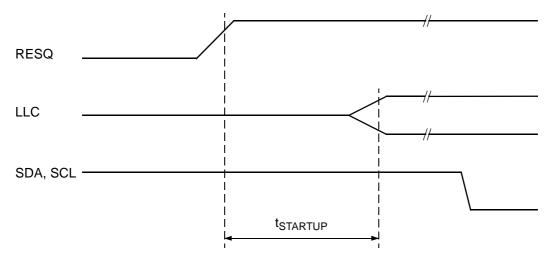

The ASI 3560A distinguishes between two kinds of reset, an external and an internal reset. The external hardware or power-on-reset leads to the stand-by mode. The internal reset is evoked by an I<sup>2</sup>C command and switches from stand-by to an operation mode.

The stand-by mode is the default mode at the startup and requires the LLC clock from the video demodulator, e.g. a VPX32xx. Without this clock, the ASI 3560A is switched off completely and is in the so-called sleep mode.

The I<sup>2</sup>C interface has its own sleep mode which is independent of the IC's stand-by mode. When a start condition is sensed, the I<sup>2</sup>C interface becomes active and performs an I<sup>2</sup>C transaction, e.g. receiving a telegram. After the stop condition has been sensed, the I<sup>2</sup>C interface automatically returns to its sleep mode. If the I<sup>2</sup>C interface has received the correct wakeup sequence for ASI3560A (setting bit[0] of the 'asi\_mode' register to one), the ASI 3560A leaves its standby mode and enters the 'sync mode'.

During the 'sync mode', the line and pixel counter are adjusted accordingly to Href/Vref or SAV/EAV, respectively. Please note that still no data is output.

Setting bit[1] of the 'asi\_mode' register switches the ASI 3560A into the operation mode, but the output will stay disabled until the end of the specified audio window in the component stream has been detected. At this point, the FIFO and the I<sup>2</sup>S-interface are reset, so that the first transmitted audio window contains the correct audio samples collected during one field period.

In general, there are no timing constraints concerning the reset procedure, apart from the fact that the ASI 3560A requires the LLC clock from the video decoder for functionality. Therefore, the controller must wait until the video decoder generates this clock before it may send the ASI 3560A wake-up protocol. Please consult the data sheet of the video decoder for further information about the time between reset and the generation of the LLC clock.

Fig. 2-8: Operation modes of the ASI 3560A

power on, LLC clock off

only I<sup>2</sup>C interface active

field and line synchronization, no output

wait until the end of the audio window is detected, no output

end of the audio window reached, clear FIFO, reset I<sup>2</sup>S interface no output

normal operation, output enabled The first audio window contains those samples which have been received since the end of the previous audio window.

The FIFO overflow is indicated by the ASI status flag in the stream and by the FIFO status flag in the asi\_mode register. The I<sup>2</sup>S input is stopped and the remaining FIFO content is output in the next audio windows. Afterwards, no further data is output until the FIFO and the interface is reset.

## 2.6. FIFO and Output Controlling

An internal state machine analyzes the incoming sync information from the video decoder (HREF,VREF, or sync headers) and derives the actual line number within the current field and the horizontal position within the line.

If the programmed audio window is detected, the state machine disables the output of the video decoder and initiates the generation of an ancillary header preceding valid audio data. After termination of the header, the reading of the assembled audio data from the internal FIFO is started.

The number of audio samples per ancillary packet is determined for each line independently. It depends on the FIFO filling level and the horizontal size of the audio window. The ASI 3560A attempts to output the data as fast as possible. If enough samples are available in the FIFO, the ancillary data packet containing audio samples will take up the maximum allowed horizontal space, otherwise an even number of samples from the available data will be output.

For clear identification of the left and right channel, data is always transmitted in packets of 6 bytes corresponding to one sample for each channel starting with the left one. For more details concerning the transmission format, see section 2.4.

The FIFO buffers the incoming continuous audio data stream. Its size of 3 kbytes is determined for the transmission of serial data with 128 kByte/s in the vertical blanking interval assuming a worst case scenario (50 Hz TV standard, 5% line frequency deviation, minimum number of lines used for the audio window).

In case of a FIFO overflow, the FIFO status bit in the 'asi\_mode' register is set and the FIFO input is stopped. This means that the FIFO contains valid data which will be output in the following audio windows. Since the ASI status flag in the output data is set, the

user can detect the overflow in time and can react with muting or even fading.

In order to restart the FIFO, the user has to reset the FIFO status flag in the 'asi\_mode' control register. Please note that every write access to the 'asi\_mode' register leads to a FIFO and I<sup>2</sup>S interface reset if bit[2] is set to zero.

#### 2.7. Video Stream Interface

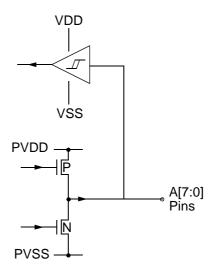

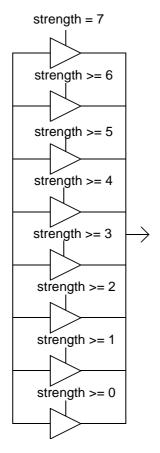

The video interface of the ASI 3560A is bidirectional, because it works as an input interface during the syncdetection in the ITU-R 656 mode. Its output driver strength can be adjusted with the bits[11:13] of the 'IO mode' register.

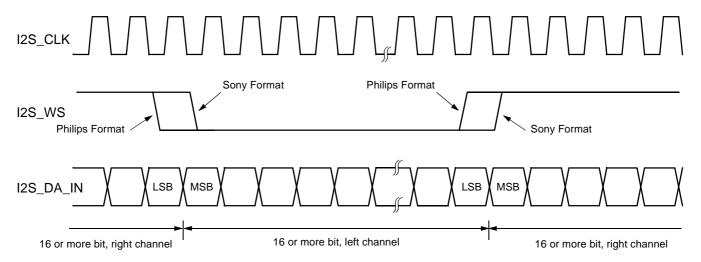

## 2.8. I<sup>2</sup>S Interface

Audio data is received via an I<sup>2</sup>S slave interface which accepts MSB first serial audio data with a resolution of 16 or more bits. However, the internal storage is limited to 16 bits per sample. The interface supports both the Philips and the Sony format. The required format can be selected with bit[9] of the 'IO\_mode' register (see Table 3–2 on page 18). Additionally, the valid data bits can be left or right aligned - but still MSB first - within the data word (bit[10]).

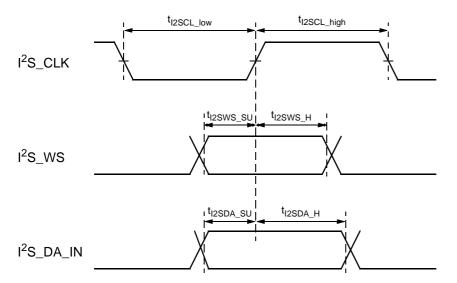

Figure 2–9 shows the supported I<sup>2</sup>S bus formats. The serial data is transmitted in two's complement with MSB first. The data is synchronized with the falling edge of the clock and latched at the rising edge.

A detailed description of the timing constraints can be found in section 4.6.3. on page 26 and section 4.8.7. on page 35.

The interface can handle data rates up to 4.1 Mbit/s, which means sample rates up to 130 kHz with 32 bit frames per sample and channel are possible.

Fig. 2–9: I<sup>2</sup>S bus transmission formats

**ASI 3560A**

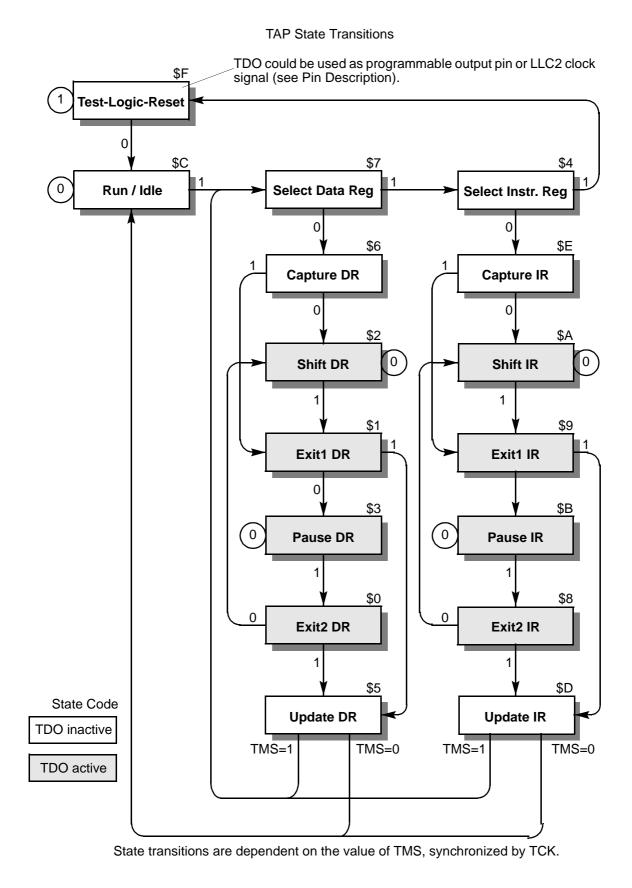

## 2.9. JTAG Boundary-Scan, Test Access Port (TAP)

The design of the Test Access Port, which is used for Boundary-Scan Test, conforms to standard IEEE 1149.1-1990. Also included is a list of the mandatory instructions supported, as well as the optional instructions. The following comprises a brief overview of some of the basics, as well as any optional features which are incorporated. The IEEE 1149.1 document may be necessary for a more concise description. Finally, an adherence section goes through a checklist of topics and describes how the design conforms to the standard.

The implementation of the instructions HIGHZ and CLAMP conforms to the supplement P1149.1/D11 (October 1992) to the standard 1149.1-1990.

## 2.9.1. General Description

The TAP in the ASI 3560A is incorporated using the four signal interface. The interface includes TCK, TMS, TDI, and TDO. The optional TRESET signal is not used. This is not needed because the chip has an internal power-on-reset which will automatically steer the chip into the TEST-LOGIC-RESET state. The goal of the interface is to provide a means to test the boundary of the chip. There is no support for internal or BIST(built-in self test).

## 2.9.2. TAP Architecture

The TAP function consists of the following blocks: TAP-controller, instruction register, boundary-scan register, bypass register, optional device identification register, and master mode register.

#### 2.9.2.1. TAP Controller

The TAP controller is responsible for responding to the TCK and TMS signals. It controls the transition between states of this device. These states control selection of the data or instruction registers and the actions which occur in these registers. These include capture, shifting, and update. See Fig. 5-1 of IEEE 1149.1 for TAP state diagram.

## 2.9.2.2. Instruction Register

The instruction register chooses which one of the data registers is placed between the TDI and TDO pins when the select data register state is entered in the TAP controller. When the select instruction register state is active, the instruction register is placed between the TDI and TDO.

#### Instructions

The following instructions are incorporated:

- bypass

- sample/preload

- extest

- master mode

- ID code

- HIGHZ

- CLAMP

## 2.9.2.3. Boundary Scan Register

The boundary scan register (BSR) consists of boundary scan cells (BSCs) which are distributed throughout the chip. These cells are located at or near the I/O pad. It allows sampling of inputs, controlling of outputs, and shifting between each cell in a serial fashion to form the BSR. This register is used to verify board interconnect.

#### **Input Cell**

The input cell is constructed to achieve capture only. This is the minimal cell necessary since Internal Test (INTEST) is not supported. The cell captures either the system input in the CAPTURE-DR state or the previous cells output in the SHIFT-DR state. The captured data is then available to the next cell. No action is taken in the UPDATE-DR state. See Figure 10-11 of IEEE 1149.1 for reference.

#### **Output Cell**

The output cell will allow both capture and update. The capture flop will obtain system information in the CAP-TURE-DR state or previous cells information in the SHIFT-DR state. The captured data is available to the next cell. The captured or shifted data is downloaded to the update flop during the UPDATE-DR state. The data from the update flop is then multiplexed to the system output pin when the EXTEST instruction is active. Otherwise, the normal system path exists where the signal from the system logic flows to the system output pin. See Fig. 10-12 of IEEE 1149.1 for reference.

#### **Tristate Cell**

Each group of output signals, which are tristatable, is controlled by a boundary scan cell (output cell type). This allows either the normal system signal or the scanned signal to control the tristate control. In the ASI 3560A, there is only one such tristate control cell for the OEQ (see section "Output Driver Tristate Control" for further information).

#### **Bidirect Cell**

The bidirect cell is comprised of an input cell and a tristate cell as described in the IEEE standard. The port A is a bidirectional tristatable port, while the SDA port is purely bidirectional.

## 2.9.2.4. Bypass Register

This register provides a minimal path between TDI and TDO. This is required for complicated boards where many chips may be connected in serial.

## 2.9.2.5. Device Identification Register

This is an optional 32-bit register which contains the MICRONAS INTERMETALL identification code (JEDEC controlled), part and revision number. This is useful in providing the tester with assurance that the correct part and revision are inserted into a PCB.

## 2.9.2.6. Master Mode Data Register

This is an optional register used to control an 8-bit test register in the chip. This register supports shift and update. No capture is supported. This was done so that the last word can be shifted out for verification.

# 2.9.3. IEEE 1149.1-1990 Spec Adherence

This section defines the details of the IEEE1149.1 design for the ASI 3560A. It describes the function as outlined by IEEE1149.1, section 12.3.1. The section of that document is referenced in the description of each function.

### 2.9.3.1. Instruction Register

(Section 12.3.1.b.i of IEEE 1149.1-1990)

The instruction register is three bits long. No parity bit is included. The pattern loaded in the instruction register during CAPTURE-IR is binary "101" (MSB to LSB). The two LSBs are defined by the spec to be "01" (bit 1 and bit 0) while the MSB (bit 2) is set to "1".

## 2.9.3.2. Public Instructions

(Section 12.3.1.b.ii of IEEE 1149.1-1990)

A list of the public instructions can be found in Table 2–3.

Table 2-3: Public instructions

| Instruction    | Code (MSB to LSB) |

|----------------|-------------------|

| EXTEST         | 000               |

| SAMPLE/PRELOAD | 001               |

| ID CODE        | 010               |

| MASTER MODE    | 011               |

| HIGHZ          | 100               |

| CLAMP          | 110               |

| BYPASS         | 100 - 111         |

The EXTEST and SAMPLE/PRELOAD instructions both apply the boundary scan chain to the serial path. The ID CODE instruction applies the ID register to the serial chain. The BYPASS, the HIGHZ, and the CLAMP instructions apply the bypass register to the serial chain.

The MASTER MODE instruction is a test data instruction for public use. It provides the ability to control an 8-bit test register in the chip.

## 2.9.3.3. Self-Test Operation

(Section 12.3.1.b.iii of IEEE 1149.1-1990).

There is no self-test operation included in the ASI 3560A design which is accessible via the TAP.

## 2.9.3.4. Test Data Registers

(Section 12.3.1.b.iv of IEEE 1149.1-1990).

The ASI 3560A includes the use of four test data registers. They are the required bypass and boundary scan registers, the optional ID code register, and the master mode register.

The bypass register is, as defined, a 1-bit register accessed by codes 100 through 111, inclusive. Since the design includes the ID code register, the bypass register is not placed in the serial path upon power-up or Test-Logic-Reset.

The master mode is an 8-bit test register which is used to force the ASI 3560A into special test modes. This is reset upon power-on-reset. This register supports shift and update only. It is not recommended to access this register. The loading of that register can drive the IC into an undefined state.

ASI 3560A

## 2.9.3.5. Boundary Scan Register

(Section 12.3.1.b.v of IEEE 1149.1-1990)

The boundary scan chain has a length of 29 shift registers. The scan chain order is specified in Table 2–4

## 2.9.3.6. Device Identification Register

(Section 12.3.1.b.vi of IEEE 1149.1-1990)

The manufacturer's identification code for MICRONAS INTERMETALL is "6C" (hex). The general implementation scheme uses only the 7 LSBs and excludes the MSB, which is the parity bit. The part number is  $3010_{\rm hex}$  in case of ASI 3560A. The version code starts from "1" (hex) and changes with every revision. The version number relates to changes of the chip interface only.

| Ve | ersi | on |     | Part | Part Number 7F |      |     |     | 7F Manufacturer ID |   |     |     | D |

|----|------|----|-----|------|----------------|------|-----|-----|--------------------|---|-----|-----|---|

| 0  | 0 0  | 1  | 001 | 1000 | 0000           | 1000 | 000 | 000 | 0                  | 1 | 101 | 100 | 1 |

| 31 |      | 28 | 27  |      |                |      | 121 | 1   | 8                  | 7 |     | 1   | 0 |

|    | 1    |    | 3   | 0    | 1              | 0    |     | 0   |                    |   | d   | 9   |   |

Fig. 2-10: Device identification register

Table 2-4: Scan chain order

| No. | Pin                    | Mode     |  |  |

|-----|------------------------|----------|--|--|

| 1   | VREF                   | input    |  |  |

| 2   | HREF                   | input    |  |  |

| 3   | I <sup>2</sup> S_WS    | input    |  |  |

| 4   | I <sup>2</sup> S_CLK   | input    |  |  |

| 5   | I <sup>2</sup> S_DA_IN | input    |  |  |

| 6   | RESQ                   | input    |  |  |

| 7   | SCL                    | input    |  |  |

| 8   | SDA                    | output   |  |  |

| 9   | SDA                    | input    |  |  |

| 10  | LLC                    | input    |  |  |

| 11  | OEQ                    | tristate |  |  |

| 12  | OEQ                    | output   |  |  |

| 13  | A[7:0]                 | tristate |  |  |

| 14  | A[0]                   | output   |  |  |

| 15  | A[0]                   | input    |  |  |

| 16  | A[1]                   | output   |  |  |

| 17  | A[1]                   | input    |  |  |

| 18  | A[2]                   | output   |  |  |

| 19  | A[2]                   | input    |  |  |

| 20  | A[3]                   | output   |  |  |

| 21  | A[3]                   | input    |  |  |

| 22  | A[4]                   | output   |  |  |

| 23  | A[4]                   | input    |  |  |

| 24  | A[5]                   | output   |  |  |

| 25  | A[5]                   | input    |  |  |

| 26  | A[6]                   | output   |  |  |

| 27  | A[6]                   | input    |  |  |

| 28  | A[7]                   | output   |  |  |

| 29  | A[7]                   | input    |  |  |

.

Fig. 2-11: TAP state transitions

#### 2.9.3.7. Performance

(Section 12.3.1.b.vii of IEEE 1149.1-1990)

See section "Specification" for further information.

## 2.10. Enable/Disable of Output Signals

In order to enable the output pins of the ASI 3560A to achieve the high impedance/tristate mode, various controls have been implemented. The following paragraphs give an overview of the different tristate modes of the output signals.

## BS (Boundary Scan) Mode:

The tristate control by the test access port TAP for boundary scan has the highest priority. Even if the TAP-controller is in the EXTEST or CLAMP mode, the tristate behavior is only defined by the state of the different boundary scan registers for enable control. If the TAP controller is in HIGHZ mode, then all output pins are in tristate mode independent of the state of the different boundary scan registers for enable control.

#### **RESET State:**

If the TAP-controller is not in the EXTEST mode, then the RESET-state defines the state of all digital outputs. The only exception is made for the data output of the boundary scan interface TDO. If the circuit is in reset condition ( $\overline{RES} = 0$ ), then all output interfaces are in tristate mode.

16 MICRONAS INTERMETALL

#### 3. I<sup>2</sup>C Bus Interface

The ASI 3560A configurations are programmable via an  $I^2C$  bus slave control interface. Only one level of subaddressing is used, which means the first bus address selects the device; the second, the internal register. The device address is given in Table 3–1, a list of the available  $I^2C$  registers in Table 3–2.

The I<sup>2</sup>C interface of the ASI 3560A conforms to the specification for the I<sup>2</sup>C-fast-mode. If the power supply of the ASI 3560A is switched off, both pins SCL and SDA float. external pull-up devices must be adapted to fulfill the required rise time for the fast-mode. For bus loads up to 200 pF, the pull-up device could be a resistor; for bus loads between 200 pF and 400 pF, the pull-up device can be a current source (3 mA max.) or a switched resistor circuit.

Please note, that the I<sup>2</sup>C control interface requires the LLC clock to work, which means that the chip cannot be addressed, if the VPX is in sleep mode

Table 3–1: I<sup>2</sup>C Device Address

| Mode                        | Write             | Read              |  |

|-----------------------------|-------------------|-------------------|--|

| ASI 3560A<br>device address | 38 <sub>hex</sub> | 39 <sub>hex</sub> |  |

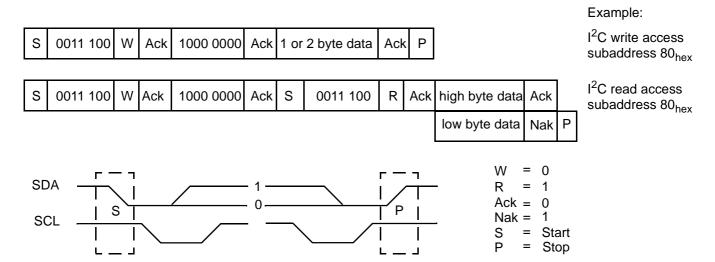

#### 3.1. Protocol Description

Once the reset is complete, the IC is selected by asserting the device address in the address part of a  $\rm I^2C$  transmission. A device address pair is defined as a write address  $(38_{\rm hex})$  and a read address  $(39_{\rm hex})$ . Writing is done by sending the device write address first, followed by the subaddress byte and one or two data bytes. For reading, the read subaddress has to be transmitted, first, by sending the device write address  $(38_{\rm hex})$  followed by the subaddress, a second start condition with the device read address  $(39_{\rm hex})$ , and reading one or two bytes of data. It is not allowed to send a stop condition in between. This will result in reading erratic data.

The registers of the ASI 3560A have 8 or 16- bit data size; 16-bit registers are accessed by reading/writing two 8-bit data bytes with the high byte first. The order of the bits in a data/address/subaddress byte is always MSB first.

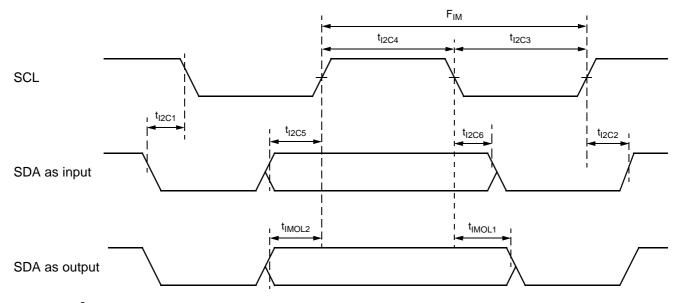

Figure 3–1 shows the I<sup>2</sup>C bus protocols for read and write operations; the read operation requires an extra start condition after the subaddress and repetition of the read chip address, followed by the read data bytes.

Fig. 3–1: I<sup>2</sup>C bus protocol (MSB first)

# 3.2. Control Registers

Table 3–2 contains a list of the available control registers. The start initialization for all registers apart from I2C\_IDx and Ver\_NR is zero. For the asi\_mode register this means that the chip is in stand-by mode after a reset.

Table 3–2: I<sup>2</sup>C Register Table

| I <sup>2</sup> C Reg.<br>Address | Number of bits | Mode <sup>1)</sup> | Function                                                                                                                                                                               | Name                |

|----------------------------------|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 00 <sub>hex</sub>                | 8/8            | r                  | Manufacture ID in accordance with JEDEC Solid State Products Engineering Council, Washington DC                                                                                        | I2C_ID0             |

|                                  |                |                    | MICRONAS INTERMETALL Code EC <sub>hex</sub>                                                                                                                                            |                     |

| 01 / 02 <sub>hex</sub>           | 8 / 8          | r                  | 16-bit part number: 3010 <sub>hex</sub> (01: LSBs, 02: MSBs)                                                                                                                           | I2C_ID1,<br>I2C_ID2 |

| 03                               | 8/8            | r                  | Version number: 01 <sub>hex</sub>                                                                                                                                                      | Ver_NR              |

| 80 <sub>hex</sub>                | 9 / 16         | w/r                | start line of the audio data window within a field                                                                                                                                     | VStart              |

| 81 <sub>hex</sub>                | 9 / 16         | w/r                | end line of the audio data window within a field                                                                                                                                       | VStop               |

| 82 <sub>hex</sub>                | 10 / 16        | w/r                | horizontal start position relative to the trailing edge of Href (2 bytes packets), minimum allowed value is 3 (means 6bytes).                                                          | HStart              |

| 7F <sub>hex</sub>                | 8/8            | w/r                | number of stereo samples (6 byte) per line                                                                                                                                             | HSte-<br>reoSamples |

| 84 <sub>hex</sub>                | 11 / 16        | w/r                | interface mode register                                                                                                                                                                | IO_mode             |

|                                  |                |                    | bit[0] : Href polarity 0 : active high 1 : active low                                                                                                                                  | hpol                |

|                                  |                |                    | bit[1] : Vref polarity 0 : active high 1 : active low                                                                                                                                  | vpol                |

|                                  |                |                    | bit[2] : ANC preamble modification<br>0 : standard header (00 <sub>h</sub> FF <sub>h</sub> FF <sub>h</sub> )<br>1 : modified header (80 <sub>h</sub> 7F <sub>h</sub> 7F <sub>h</sub> ) | preamod             |

|                                  |                |                    | bit[3] : Data block number (DBN) mode 0 : every ancillary data packet is counted with 6-bit counter 1 : DBN is always set to \$80                                                      | dbn_mod             |

|                                  |                |                    | bit[4] : data count (DC) mode 0 : Standard mode (counting DWords) 1 : INTERMETALL extended mode (8-bit counting 6 byte packages, no parities!)                                         | dc_mode             |

**Table 3–2:** I<sup>2</sup>C Register Table, continued

| I <sup>2</sup> C Reg.<br>Address | Number of bits | Mode <sup>1)</sup> | Function                                                                                                                                                                  | Name         |

|----------------------------------|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 84 <sub>hex</sub>                | 11 / 16        | w/r                | bit[6:5]: ITU-R656 header detection enable 0 0: use Vref and Href 0 1: scan video component stream and synchronize to SAVs 1 1: scan video stream and synchronize to EAVs | scanstream   |

|                                  |                |                    | bit[8:7] : Field usage<br>0 0 : every field<br>0 1 : every odd field<br>1 1 : every even field                                                                            | field_select |

|                                  |                |                    | bit[9] : I <sup>2</sup> S mode<br>0 : Japanese<br>1 : Philips                                                                                                             | I2S_mode     |

|                                  |                |                    | bit[10] : I <sup>2</sup> S alignment<br>0 : left aligned within data word, MSB first<br>1 : right aligned within data, MSB first                                          | I2S_align    |

|                                  |                |                    | bit[13:11] : driver strength of port A[7:0]                                                                                                                               | stra1        |

| 10 <sub>hex</sub>                | 8/8            | w/r                | Data ID in ANC-header                                                                                                                                                     | DID          |

| 08 <sub>hex</sub>                | 3/8            | w/r                | Stand-by, control                                                                                                                                                         | asi_mode     |

|                                  |                |                    | bit[1:0] : operation mode control 0 0 : stand-by mode (default) 0 1 : sync mode, output disabled 1 1 : data out enable                                                    | asi_state    |

|                                  |                |                    | bit[2] : FIFO control flag<br>read : FIFO status flag (1 : overflow)<br>write : 0 - reset FIFO and synchronize                                                            | status       |

<sup>1)</sup> w: writable, r: readable

## 4. Specifications

## 4.1. Outline Dimensions

Fig. 4–1: 44-Pin PLCC Plastic Leaded Chip Carrier Package (PLCC44) Weight approximately 2.5 g Dimensions in mm

# 4.2. Pin Connections and Short Descriptions

NC = not connected, leave vacant LV = if not used, leave vacant

S.T.B. = shorted to BAGNDI if not used DVSS = if not used, connect to DVSS X = obligatory; connect as described in circuit diagram AHVSS = connect to AHVSS

| Pin No.        | Pin Name | Туре   | Connection    | Short Description                    |

|----------------|----------|--------|---------------|--------------------------------------|

| PLCC<br>44-pin |          |        | (If not used) |                                      |

| 1              | TDO      | OUT    | NC            | Boundary-Scan-Test Data Output       |

| 2              | TMS      | IN     | NC            | Boundary-Scan-Test Mode Select       |

| 3              | NC       |        | LV            | not connected                        |

| 4              | TDI      | IN     | NC            | Boundary-Scan-Test Data Input        |

| 5              | NC       |        | LV            | not connected                        |

| 6              | VREF     | IN     |               | vertical reference                   |

| 7              | HREF     | IN     |               | horizontal reference                 |

| 8              | NC       |        | LV            | not connected                        |

| 9              | I2S_WS   | IN     |               | I <sup>2</sup> S word select         |

| 10             | NC       |        | LV            | not connected                        |

| 11             | I2S_CLK  | IN     |               | I <sup>2</sup> S clock               |

| 12             | VDD      | SUPPLY | Х             | supply voltage for digital circuitry |

| 13             | VSS      | SUPPLY | Х             | supply voltage for digital circuitry |

| Pin No. | Pin Name  | Туре   | Connection (If not used) | Short Description              |

|---------|-----------|--------|--------------------------|--------------------------------|

| 44-pin  | NO        |        | 137                      | not connected.                 |

| 14      | NC        | INI    | LV                       | not connected                  |

| 15      | I2S_DA_IN | IN     |                          | I <sup>2</sup> S data input    |

| 16      | NC        |        | LV                       | not connected                  |

| 17      | RESQ      | IN     |                          | reset input                    |

| 18      | SCL       | IN/OUT |                          | I <sup>2</sup> C clock         |

| 19      | NC        |        | LV                       | not connected                  |

| 20      | SDA       | IN/OUT |                          | I <sup>2</sup> C data          |

| 21      | NC        |        | LV                       | not connected                  |

| 22      | LLC       | IN     |                          | double clock (27 MHz)          |

| 23      | NC        |        | LV                       | not connected                  |

| 24      | OEQ       | OUT    |                          | disable video output           |

| 25      | NC        |        | LV                       | not connected                  |

| 26      | A0        | IN/OUT |                          | video data port                |

| 27      | NC        |        | LV                       | not connected                  |

| 28      | A1        | IN/OUT |                          | video data port                |

| 29      | A2        | IN/OUT |                          | video data port                |

| 30      | NC        |        | LV                       | not connected                  |

| 31      | A3        | IN/OUT |                          | video data port                |

| 32      | NC        |        | LV                       | not connected                  |

| 33      | PVSS      | SUPPLY | Х                        | supply voltage pad circuits    |

| 34      | NC        |        | LV                       | not connected                  |

| 35      | PVDD      | SUPPLY | Х                        | supply voltage pad circuits    |

| 36      | NC        |        | LV                       | not connected                  |

| 37      | A4        | IN/OUT |                          | video data port                |

| 38      | NC        |        | LV                       | not connected                  |

| 39      | A5        | IN/OUT |                          | video data port                |

| 40      | A6        | IN/OUT |                          | video data port                |

| 41      | NC        |        | LV                       | not connected                  |

| 42      | A7        | IN/OUT |                          | video data port                |

| 43      | NC        |        | LV                       | not connected                  |

| 44      | TCK       | IN     | NC                       | Boundary-Scan-Test Clock Input |

## 4.3. Pin Descriptions

Pins 2, 4 - JTAG Input Pins TMS, TDI (Fig. 4–4) Test Mode Select and Test Data Input signals of the JTAG Test Access Port (TAP). Both signals are inputs with a TTL compatible input specification. To comply with JTAG specification, they use pull-ups at their input stage. The input stage of the TMS and TDI uses a TTL Schmitt Trigger.

Pin 44 - JTAG Input Pin TCK (Fig. 4-3)

Clock signal of the Test-Access Port. It is used to synchronize all JTAG functions. When JTAG operations are not being performed, this pin should be driven to VSS. The input stage of the TCK uses a TTL Schmitt Trigger.

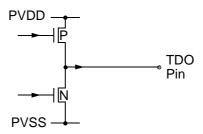

Pin 1 - JTAG Output Pin TDO (Fig. 4–7)

Data output for JTAG Test Access Port (TAP).

Pins 9 - I<sup>2</sup>S Wordstrobe I2S\_WS (Fig. 4–3) This pin connects to the I<sup>2</sup>S bus wordstrobe line.

Pins 11 - I<sup>2</sup>S Clock I2S\_CLK (Fig. 4–3) This pin connects to the I<sup>2</sup>S bus clock line.

Pins 15 - I<sup>2</sup>S Data I2S\_DA\_IN (Fig. 4–3) This pin connects to the I<sup>2</sup>S bus data line.

Pins 6,7 - Reference Signals VREF, HREF (Fig. 4–3) These signals are sync signals generated by the video decoder (e.g. VPX).

Pins 26,28,29,31,37,39,40,42 - Video Port A[7:0] (Fig. 4-8)

Pin 35 - Supply Voltage, Pad Circuitry PVDD

Pins 22 - LLC (Fig. 4-3)

LLC is the reference clock signal for the video bus connected to port A[7:0].

Pin 33- Ground, Pad Circuitry PVSS

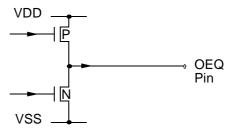

Pin 24 - Output Enable Output Signal OEQ (Fig. 4–6) The output enable output signal has TTL output characteristic. It controls the tri-state condition of the video ports of the video demodulator (e.g. VPX. Please note that the state during the positive edge of RESQ selects the I<sup>2</sup>C device address of a VPX).

Pin 20 - I<sup>2</sup>C Data SDA (Fig. 4–5) This pin connects to the I<sup>2</sup>C bus data line.

Pin 18 - I<sup>2</sup>C Clock SCL (Fig. 4–5) This pin connects to the I<sup>2</sup>C bus clock line.

Pin 17 - Reset Input RESQ (Fig. 4–3) A low level on this pin resets the circuit.

Pin 13 - Ground, Digital Circuitry VSS

Pin 12 - Supply Voltage, Digital Circuitry VDD

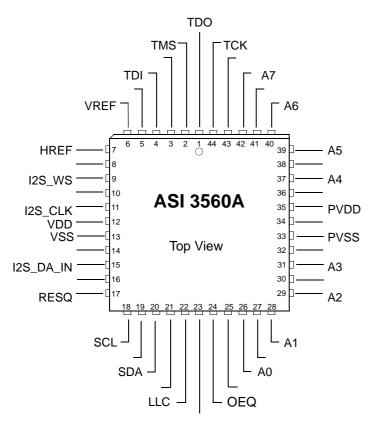

# 4.4. Pin Configuration

Fig. 4-2: 44-pin PLCC package

## 4.5. Pin Circuits

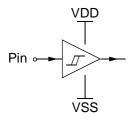

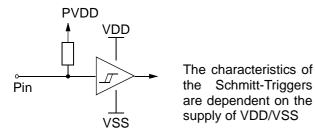

Fig. 4–3: TCK, HREF, VREF, RESQ, LLC, I<sup>2</sup>S\_xxx

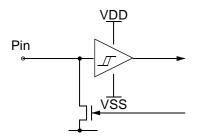

Fig. 4-4: TMS, TDI

Fig. 4-5: I<sup>2</sup>C Interface SDA, SCL

Fig. 4-6: OEQ

Fig. 4-7: Output port TDO

Fig. 4-8: Bidirectional video port A[7:0]

## 4.6. Electrical Characteristics

#### 4.6.1. Absolute Maximum Ratings

| Symbol               | Parameter                                        | Pin<br>Name    | Min.       | Max.                     | Unit |

|----------------------|--------------------------------------------------|----------------|------------|--------------------------|------|

| T <sub>A</sub>       | Ambient Temperature                              |                | 0          | 65                       | °C   |

| T <sub>S</sub>       | Storage Temperature                              |                | -40        | 125                      | °C   |

| TJ                   | Junction Temperature                             |                | 0          | 125                      | °C   |

| V <sub>SUB</sub>     | Supply Voltage, all Supply Inputs                |                | -0.3       | 6                        | V    |

| P <sub>TOT MAX</sub> | Power Dissipation due to package characteristics | VDD,<br>PVDD,  |            | 1089                     | mW   |

|                      | Input Voltage of TMS, TDI                        |                | PVSS - 0.5 | PVDD + 0.5 <sup>1)</sup> | V    |

|                      | Input Voltage                                    | TCK            | PVSS - 0.5 | 6                        | V    |

|                      | Input Voltage                                    | SDA,<br>SCL    | VSS - 0.5  | 6                        | V    |

|                      | Signal Swing                                     | A[7:0],<br>TDO | PVSS - 0.5 | PVDD + 0.5 <sup>1)</sup> | V    |

|                      | Signal Swing                                     | OEQ            | VSS - 0.5  | VDD + 0.5 <sup>1)</sup>  |      |

|                      | Maximum D   VSS - PVSS                           |                |            | 0                        | V    |

<sup>1)</sup> External voltage exceeding PVDD+0.5 V should not be applied to these pins even when they are tri-stated.

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions/Characteristics" of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

## 4.6.2. Recommended Operating Conditions

| Symbol            | Parameter                     | Pin<br>Name | Min. | Тур. | Max.              | Unit |

|-------------------|-------------------------------|-------------|------|------|-------------------|------|

| T <sub>A</sub>    | Ambient Operating Temperature | -           | 0    | -    | 65                | °C   |

| V <sub>SUPD</sub> | Digital Supply Voltage        | VDD         | 4.75 | 5.0  | 5.25              | V    |

| V <sub>SUPP</sub> | Pad Supply Voltage            | PVDD        | 3.15 |      | 3.6 <sup>1)</sup> | V    |

| f <sub>XTAL</sub> | Clock Frequency               | LLC         |      | 27.0 |                   | MHz  |

<sup>&</sup>lt;sup>1)</sup> could also be connected to the 5 V supply net; but for best performance, it is recommended to connect it to 3.3 V supply.

# 4.6.3. Recommended I<sup>2</sup>S Conditions

| Symbol                  | Parameter                               | Pin Name               | Min. | Тур. | Max. | Unit |

|-------------------------|-----------------------------------------|------------------------|------|------|------|------|

| t <sub>I2SCL_low</sub>  | I <sup>2</sup> S Clock low time         | I <sup>2</sup> S_CLK   | 120  | 490  |      | ns   |

| t <sub>I2SCL_high</sub> | I <sup>2</sup> S Clock high time        | I <sup>2</sup> S_CLK   | 120  | 490  |      | ns   |

| t <sub>I2SWS_SU</sub>   | I <sup>2</sup> S word strobe setup time | I <sup>2</sup> S_WS    | 40   |      |      | ns   |

| t <sub>I2SWS_H</sub>    | I <sup>2</sup> S word strobe hold time  | I <sup>2</sup> S_WS    | 40   |      |      | ns   |

| t <sub>I2SDA_SU</sub>   | I <sup>2</sup> S data in setup time     | I <sup>2</sup> S_DA_IN | 40   |      |      | ns   |

| t <sub>I2SDA_H</sub>    | I <sup>2</sup> S data in hold time      | I <sup>2</sup> S_DA_IN | 40   |      |      | ns   |

# 4.6.4. Recommended I<sup>2</sup>C Conditions

(Timing diagram see Fig. 4-11 on page 33)

| Symbol            | Parameter                                                       | Pin<br>Name | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------------------------|-------------|------|------|------|------|

| V <sub>IMIL</sub> | I <sup>2</sup> C-BUS Input Low Voltage                          | SCL,<br>SDA |      |      | 0.3  | VDD  |

| V <sub>IMIH</sub> | I <sup>2</sup> C-BUS Input High Voltage                         |             | 0.6  |      |      | VDD  |

| f <sub>SCL</sub>  | I <sup>2</sup> C-BUS Frequency                                  | SCL         |      |      | 400  | kHz  |

| t <sub>I2C1</sub> | I <sup>2</sup> C START Condition Setup Time                     | SCL,<br>SDA | 1250 |      |      | ns   |

| t <sub>I2C2</sub> | I <sup>2</sup> C STOP Condition Setup Time                      |             | 1250 |      |      | ns   |

| t <sub>I2C3</sub> | I <sup>2</sup> C-Clock Low Pulse Time                           | SCL         | 1250 |      |      | ns   |

| t <sub>I2C4</sub> | I <sup>2</sup> C-Clock High Pulse Time                          |             | 1250 |      |      | ns   |

| t <sub>l2C5</sub> | I <sup>2</sup> C-Data Setup Time Before<br>Rising Edge of Clock | SCL,<br>SDA | 250  |      |      | ns   |

| t <sub>I2C6</sub> | I <sup>2</sup> C-Data Hold Time after Falling<br>Edge of Clock  |             | 250  |      |      | ns   |

# $\textbf{4.6.5. Recommended Digital Inputs Levels of HREF, VREF, A[7:0], LLC, I$^2S\_xxx, RESQ, TCK, TMS, TDI Algorithms and the second secon$

| Symbol          | Parameter          | Pin Name                                                                 | Min. | Тур. | Max.          | Unit |

|-----------------|--------------------|--------------------------------------------------------------------------|------|------|---------------|------|

| V <sub>IL</sub> | Input Voltage LOW  | HREF, VREF, A[7:0],<br>LLC, I <sup>2</sup> S_xxx, RESQ,<br>TCK, TMS, TDI | -0.5 | 0    | 8.0           | V    |

| V <sub>IH</sub> | Input Voltage HIGH | HREF, VREF, LLC,<br>I <sup>2</sup> S_xxx, RESQ, TCK                      | 2.0  | 5    | 6             | V    |

| V <sub>IH</sub> | Input Voltage HIGH | TDI, TMS, A[7:0]                                                         | 2.0  | PVDD | PVDD +<br>0.3 | V    |

## 4.7. Characteristics

at T<sub>A</sub> = 0 to 65 °C, V<sub>SUPD/A</sub> = 4.75 to 5.25 V, V<sub>SUPP</sub> = 3.15 to 3.5 V, f = 27.0 MHz for min./max. values at T<sub>C</sub> = 60 °C, V<sub>SUPD/A</sub> = 5 V, V<sub>SUPP</sub> = 3.3 V, f = 27.0 MHz for typical values

## 4.7.1. Current Consumption

| Symbol             | Parameter                                           | Pin Name     | Min.                  | Тур.   | Max.             | Unit |

|--------------------|-----------------------------------------------------|--------------|-----------------------|--------|------------------|------|

| I <sub>VSUPD</sub> | Current Consumption                                 | VDD          |                       | t.b.d. |                  | mA   |

| I <sub>VSUPP</sub> | Current Consumption                                 | PVDD         | application dependent |        | mA               |      |

|                    |                                                     |              | -                     |        | 45@3.3V<br>75@5V |      |

| P <sub>TOT</sub>   | Total Power Dissipation, normal operation condition | VDD,<br>PVDD |                       | t.b.d. |                  | W    |

| P <sub>TOT</sub>   | Total Power Dissipation low power mode              | VDD,<br>PVDD |                       | t.b.d. |                  | W    |

## 4.7.2. Characteristics, Reset

(Timing diagram see Fig. 4-10 on page 33)

| Symbol               | Parameter                   | Min. | Тур. | Max. | Unit | Test Conditions                                 |

|----------------------|-----------------------------|------|------|------|------|-------------------------------------------------|

| t <sub>startup</sub> | RESQ inactive to active LLC |      | 3.2  |      | us   | Reset and LLC from video decoder (e.g. VPX32xx) |

## 4.7.3. Characteristics, Control Bus Interface

(Timing diagram see Fig. 4–11 on page 33)

| Symbol             | Parameter                                                                     | Pin<br>Name | Min. | Тур. | Max.       | Unit | Test Conditions                                     |

|--------------------|-------------------------------------------------------------------------------|-------------|------|------|------------|------|-----------------------------------------------------|

| $V_{\text{IMOL}}$  | Output Low Voltage                                                            | SDA         | -    | -    | 0.4<br>0.6 | V    | I <sub>I</sub> = 3 mA<br>I <sub>I</sub> = 6 mA      |

| t <sub>IMOL1</sub> | I <sup>2</sup> C-Data Output Hold Time after<br>Falling Edge of Clock SCL     | SDA         | 15   |      |            | ns   |                                                     |

| t <sub>IMOL2</sub> | I <sup>2</sup> C-Data Output Setup Time<br>before Rising Edge of Clock<br>SCL | SDA         | 100  |      |            | ns   | f <sub>SCL</sub> = 1 MHz, VDD = 5 V                 |

| t <sub>F</sub>     | Signal Fall Time                                                              | SDA         | -    | -    | 300        | ns   | C <sub>L</sub> = 400 pF,<br>R <sub>PU</sub> = 4,7 k |

| f <sub>SCL</sub>   | Clock Frequency <sup>1)</sup>                                                 | SCL         | 0    | -    | 400        | kHz  | low power mode                                      |

<sup>1)</sup> The maximum clock frequency of the I2C interface is limited to 400 kHz while the IC is working in the low power mode.

# 4.7.4. Characteristics, JTAG Interface (Test Access Port TAP)

(Timing diagram see Fig. 4–13 on page 34)

| Symbol                | Parameter                                                                                                              | Min.       | Тур.         | Max.      | Unit        | Test Conditions |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|------------|--------------|-----------|-------------|-----------------|

| F <sub>CYCL-TAP</sub> | JTAG Cycle Time                                                                                                        | 100        |              |           | ns          |                 |

| F <sub>H-TAP</sub>    | TCK High Time                                                                                                          | 50         |              |           | ns          |                 |

| F <sub>L-TAP</sub>    | TCK Low Time                                                                                                           | 50         |              |           | ns          |                 |

| V <sub>RES-TAP</sub>  | Minimum supply voltage to initiate an internal reset of the JTAG-TAP generated by a voltage supply supervision circuit | 3.5        |              |           | V           | VDD pin         |

| Test Access           | Port (TAP), see timing diagram Fig. 4–13 (                                                                             | on page 34 |              |           |             |                 |

| t <sub>S-TAP</sub>    | TMS, TDI Setup Time                                                                                                    | 10         |              |           | ns          |                 |

| t <sub>H-TAP</sub>    | TMS, TDI Hold Time                                                                                                     | 10         |              |           | ns          |                 |

| t <sub>D-TAP</sub>    | TCK to TDO Propagation Delay for Valid Data                                                                            |            |              | 50        | ns          |                 |

| t <sub>ON-TAP</sub>   | TDO Turn-on Delay                                                                                                      |            |              | 45        | ns          |                 |

| t <sub>OFF-TAP</sub>  | TDO Turn-off Delay                                                                                                     |            |              | 45        | ns          |                 |

| Boundary-S            | can Test, Characteristics of all IO pins which                                                                         | h are conr | nected to th | e boundar | y scan regi | ster chain      |

| t <sub>S-PINS</sub>   | Input Signals Setup Time at CAPTURE-DR                                                                                 | 10         |              |           | ns          |                 |

| t <sub>H-PINS</sub>   | Input Signals Hold Time at CAPTURE-<br>DR                                                                              | 10         |              |           | ns          |                 |

| t <sub>D-PINS</sub>   | TCK to Output Signals,<br>Delay for Valid Data                                                                         |            |              | 50        | ns          |                 |

| t <sub>ON-PINS</sub>  | Turn-on Delay                                                                                                          |            |              | 20        | ns          |                 |

| t <sub>OFF-PINS</sub> | Turn-off Delay                                                                                                         |            |              | 20        | ns          |                 |

# 4.7.5. Characteristics, Digital Inputs/Outputs

| Symbol          | Parameter                                                                                                                                       | Min.                      | Тур.                    | Max.                   | Unit       | Test Conditions                                                    |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------|------------------------|------------|--------------------------------------------------------------------|

| Digital Input   | Pins TMS, TDI, TCK, HREF, VREF, LLC, A                                                                                                          | \[7:0], I <sup>2</sup> S_ | CLK, I <sup>2</sup> S_\ | WS, I <sup>2</sup> S_D | A_IN, RES, | SCL, SDA                                                           |

| C <sub>IN</sub> | Input Capacitance                                                                                                                               |                           | 5                       | 8                      | pF         |                                                                    |

| I <sub>I</sub>  | Input Leakage Current Input Pins TCK, HREF, VREF, LLC, A[7:0], I <sup>2</sup> S_CLK, I <sup>2</sup> S_WS, I <sup>2</sup> S_DA_IN, RES, SCL, SDA |                           |                         | -1<br>+1               | mA         | $V_{I} = V_{SS}$ $V_{I} \leq V_{DD}$                               |

| I <sub>I</sub>  | Input Leakage Current<br>Input Pins with Pull-ups: TDI and TMS                                                                                  |                           | -25                     | -55<br>+1              | mA         | $V_{I} = V_{SS}$ $V_{I} \leq V_{DD}$                               |

| Digital Outpo   | ut pin OEQ                                                                                                                                      |                           |                         |                        |            |                                                                    |

| Co              | High-Impedance Output Capacitance                                                                                                               |                           |                         |                        |            |                                                                    |

| V <sub>OL</sub> | Output Voltage LOW                                                                                                                              |                           |                         |                        |            |                                                                    |

| V <sub>OH</sub> | Output Voltage HIGH                                                                                                                             |                           |                         |                        |            |                                                                    |

| I <sub>O</sub>  | Output Leakage Current                                                                                                                          |                           |                         |                        |            |                                                                    |

| Digital Outpo   | ut pins A[7:0], TDO                                                                                                                             |                           |                         |                        |            |                                                                    |

| C <sub>O</sub>  | High-Impedance Output Capacitance                                                                                                               |                           | 5                       | 8                      | pF         |                                                                    |

| $V_{OL}$        | Output Voltage LOW                                                                                                                              |                           |                         | 0.4<br>0.6             | V<br>V     | I <sub>I</sub> = 3 mA<br>I <sub>I</sub> = 6 mA                     |

| V <sub>OH</sub> | Output Voltage HIGH                                                                                                                             | 2.4                       | -                       | PVDD                   | V          |                                                                    |

| I <sub>O</sub>  | Output Leakage Current                                                                                                                          |                           |                         | -1<br>+1               | mA<br>mA   | while IC remains in low power mode $V_1 = V_{SS}$ $V_1 \le V_{DD}$ |

A special VDD, VSS supply is used only to support the digital output pins. This means, inherently, that in case of tri-state conditions, external sources should not drive these signals above the voltage PVDD which supplies the output pins.

# 4.7.6. Clock Signal LLC

The following timing specifications refer to Fig. 4–10 on page 33.

| Symbol           | Parameter                                                    | Min. | Тур. | Max. | Unit | Test Conditions |

|------------------|--------------------------------------------------------------|------|------|------|------|-----------------|

| LLC:             |                                                              |      |      |      |      |                 |

| t <sub>LLC</sub> | Cycle Time                                                   |      | 37   |      | ns   |                 |

| F <sub>H</sub>   | Duty Cycle F <sub>H</sub> /(F <sub>L+</sub> F <sub>H</sub> ) |      | 50   |      | %    |                 |

# 4.7.7. Digital Video Interface

| Symbol           | Parameter                                                                                                                                       | Min. | Тур. | Max. | Unit | Test Conditions |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----------------|--|--|--|

|                  | Data and Control Pins (LLC to A[7:0], HREF, VREF: The following timing specifications refer to the timing diagrams of section 4.8.6. on page 35 |      |      |      |      |                 |  |  |  |

| t <sub>OH</sub>  | Output Hold Time                                                                                                                                | 8    |      |      | ns   |                 |  |  |  |

| t <sub>PDI</sub> | Input Propagation Delay                                                                                                                         |      |      | 23   | ns   |                 |  |  |  |

| t <sub>PDO</sub> | Output Propagation Delay                                                                                                                        |      |      | 21   | ns   |                 |  |  |  |

| Output Ena       | ole by OEQ (see Fig. 4–12)                                                                                                                      |      |      |      |      |                 |  |  |  |

| t <sub>ON</sub>  | Output Enable OEQ                                                                                                                               |      |      | 15   | ns   |                 |  |  |  |

| t <sub>OFF</sub> | Output Disable OEQ                                                                                                                              |      |      | 15   | ns   |                 |  |  |  |

# 4.7.8. Characteristics, TTL Output Driver

# 4.7.8.1. TTL Output Driver Type A

Output Pins A[7:0], TDO

| Symbol              | Parameter                                              | Min.  | Тур.  | Max.  | Unit | Test Conditions                                               |

|---------------------|--------------------------------------------------------|-------|-------|-------|------|---------------------------------------------------------------|

| T <sub>A</sub>      |                                                        | 65    | RT    | 0     | °C   | Ambient Temperature                                           |

| VDD                 |                                                        | 4.75  | 5.0   | 5.25  | V    | Supply                                                        |