# **Quad Driver Incl. Short-Circuit Signaling**

#### **Bipolar IC**

#### Features

- Short-circuit shutdown with clock generator

- Four driver circuits for controlling power transistors

- Overload and short-circuit signaling

| Туре       | Ordering Code | Package    |

|------------|---------------|------------|

| FZL 4145 D | Q67000-H8437  | P-DIP-18-1 |

#### **General Description**

The IC comprises four driver circuits capable of driving power transistors for high output currents. The output transistors are protected against short-circuit to ground and supply voltage. The input threshold can be adjusted between 1.5 V and 7 V. Overload or short-circuit failure at an output will be indicated at pin SQ (signaling output).

#### **Functional Description**

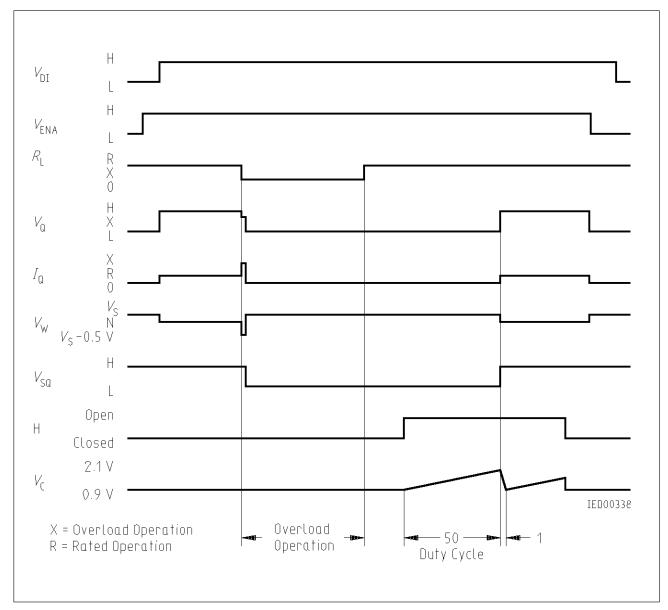

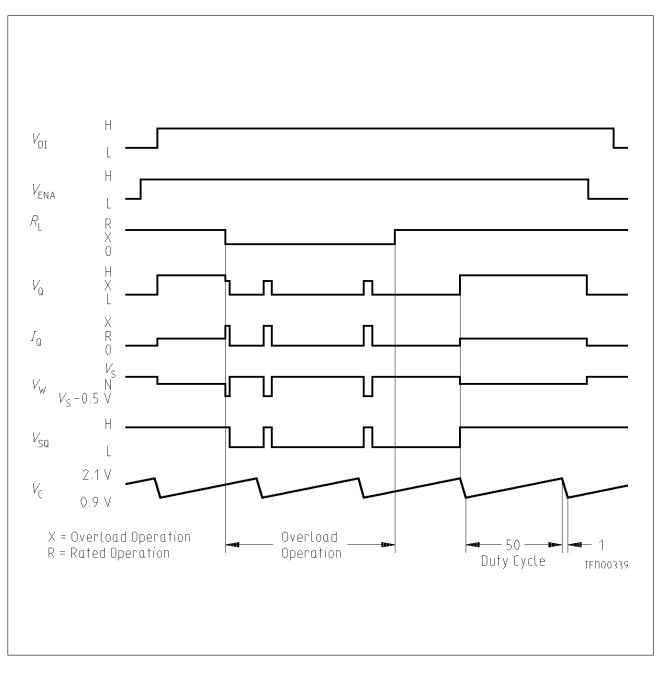

Each driver circuit has one active high driver input DI and a common enable input (ENA) (active high) is provided for all stages. The (Q) outputs are designed to drive the output transistors. The load current is sampled via pin W. If the load current exceeds the preset value, the output stage switches off. Switching-on again is provided by the built-in clock generator. Its operation requires an external capacitor  $C_{T}$  at pin C. If  $C_{T}$  is bridged by a break-key, switching on can only be carried out by operating a key. The duty cycle of the clock generator is 1:50 (e.g. 40  $\mu$ s/2 ms with  $C_{T}$  = 33 nF).

In case of overcurrent or short-circuit failure at any output stage the signaling output (SQ) will go low. In clock-governed operation (i.e. when there is automatic switching on by the clock and not by a key), SQ goes high and low at the clock rate as long as a short-circuit or overload exists. SQ is an open-collector output.

Unused W pins must be connected to  $V_{s}$ . Open W pins would simulate a short-circuit and activate the signaling output.

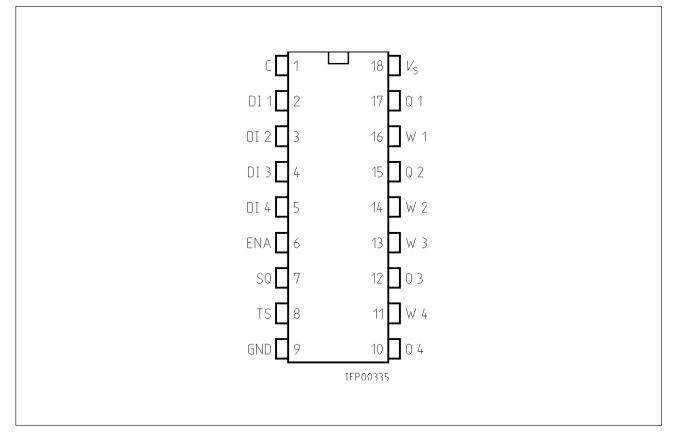

# **Pin Configuration** (top view)

$V_{\rm S}$ Clock C Generator DI 1 Q 1 8 W 1 DI 2 8 Q 2 W 2 Q3 DI 3 8 W 3 DI Driver inputs ENA Enable input Q4 DI 4 2 С **Clock capacitor** W 4 Outputs Q ENA SQ TS Input for threshold switching W Input for output current limiter ТS SQ Signaling output Ground GND IEB00336 GND ΤS

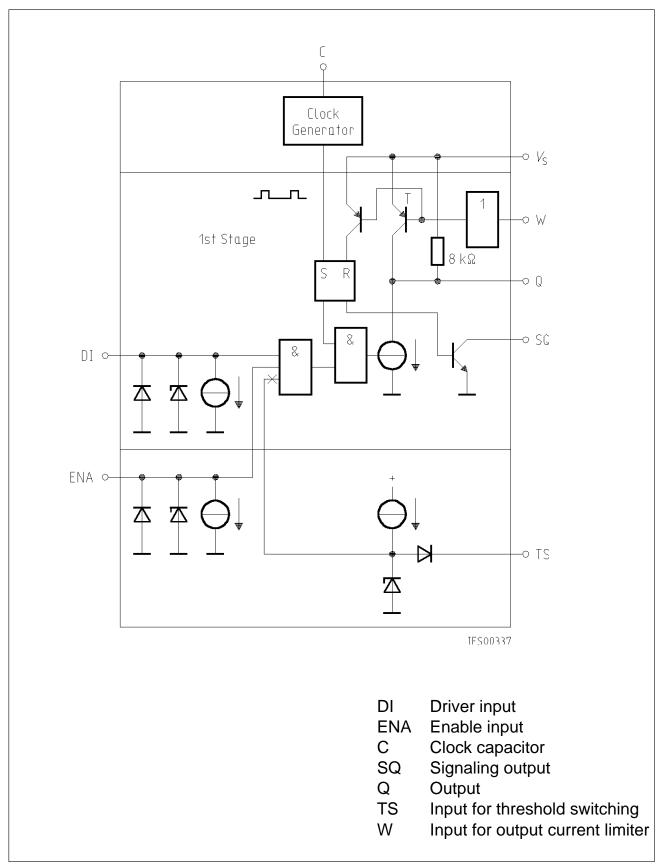

### **Block Diagram**

The switching threshold at inputs DI and ENA can be adjusted between 1.5 V and 7 V via connection TS:

| $V_{\rm TS} = 0  \rm V;$         | input threshold = 1.5 V (for 5 V logic)                   |

|----------------------------------|-----------------------------------------------------------|

| $V_{\rm TS} = 0$ to 5 V;         | input threshold = $V_{TS}$ + 1.5 V                        |

| $V_{\text{TS}} = V_{\text{S}}$ : | input threshold = 7 V (for $12/15$ V and $24/28$ V logic) |

If the output is disabled due to the logic states of inputs DI or ENA this disable is effective over the total supply voltage range between  $V_{\rm S}$  = 0 V and  $V_{\rm S}$  = 35 V.

The inputs are protected with clamp diodes.

#### **Absolute Maximum Ratings**

| Parameter                                  | Symbol                  | Limit         | Values | Unit | Remarks                                         |

|--------------------------------------------|-------------------------|---------------|--------|------|-------------------------------------------------|

|                                            |                         | min.          | max.   |      |                                                 |

| Supply voltage                             | Vs                      | - 0.3         | 35     | V    |                                                 |

|                                            | $V_{s}$                 | - 0.3         | 45     | V    | 100 ms duration,<br>1 s interval                |

| Input voltage at DI and ENA                | $V_{DI, ENA}$           | - 0.3         | 35     | V    | 1)                                              |

| Voltage at TS and SQ                       | $V_{TS, SQ}$            | - 0.3         | 45     | V    |                                                 |

| Output voltage $V_{Q}$<br>and voltage at C | $V_{ m Q}$ , $V_{ m C}$ | - 0.3         | Vs     | V    |                                                 |

| Voltage at W                               | $V_{W}$                 | $V_{\rm S}-5$ | Vs     | V    | 3)                                              |

| Input current at DI and ENA                | $I_{DI, ENA}$           | - 3           | 1      | mA   | 2)                                              |

|                                            | $I_{\rm DI, ENA}$       | - 6           | 2      | mA   | <sup>2)</sup> 100 ms duration,<br>1 s interval  |

|                                            | $I_{DI, ENA}$           | - 6           | 5      | mA   | <sup>2)</sup> 100 μs duration,<br>1 ms interval |

| Output current at SQ                       | $I_{\rm SQ}$            |               | 8      | mA   |                                                 |

| Power dissipation of                       |                         |               |        |      |                                                 |

| all input diodes                           | $P_{\rm tot}$           |               | 50     | mW   |                                                 |

| Storage temperature<br>Thermal resistance  | $T_{ m stg}$            | - 65          | 125    | °C   |                                                 |

| system - air                               | $R_{ m th~SA}$          |               | 65     | K/W  |                                                 |

| system - case                              | $R_{\rm th SC}$         |               | 45     | K/W  |                                                 |

### **Operating Range**

| Supply voltage for input threshold |                |                       |    |    |                                                                       |

|------------------------------------|----------------|-----------------------|----|----|-----------------------------------------------------------------------|

| 1.5 V                              | Vs             | 4.5                   | 35 | V  | $V_{\text{TS}} = 0 \text{ V}$                                         |

| 1.5 V to 6.5 V                     | $V_{\sf S}$    | V <sub>TS</sub> + 4.5 | 35 | V  | $V_{\text{TS}} = 0 \text{ V}$<br>$V_{\text{TS}} = 0 \text{ V}$ to 5 V |

| 7 V                                | $V_{s}$        | 10                    | 35 | V  | $V_{\rm TS} = V_{\rm S}$                                              |

| Ambient temperature                | T <sub>A</sub> | - 25                  | 85 | °C |                                                                       |

**Notes:** <sup>1)</sup>  $V_{\text{DI, ENA}} > 35$  V requires a protective resistor before DI, ENA. <sup>2)</sup>  $V_{\text{DI, ENA}}$  may increase to more than 35 V during current nodes. <sup>3)</sup> Unused W connections must be connected to  $V_{\text{S}}$ .

#### Characteristics

Supply voltage 4.5 V  $\leq V_{\rm S} \leq$  30 V

| Parameter                                                                                                            | Symbol                                                                           | Li                       | imit Valu                  | es                | Unit             | Test                                                                          |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------|----------------------------|-------------------|------------------|-------------------------------------------------------------------------------|

|                                                                                                                      |                                                                                  | min.                     | typ.                       | max.              |                  | Condition                                                                     |

| Supply current                                                                                                       | Is                                                                               |                          | 6                          | 8.5               | mA               | $V_{\rm ENA} = 0 \text{ V},$<br>$V_{\rm W} = V_{\rm S}$                       |

| H-input voltage at DI, ENA<br>H-input voltage at DI, ENA<br>L-input voltage at DI, ENA<br>L-input voltage at DI, ENA | $V_{\mathrm{IH}}$<br>$V_{\mathrm{IH}}$<br>$V_{\mathrm{IL}}$<br>$V_{\mathrm{IL}}$ | 2<br>8                   |                            | 0.7<br>6          | V<br>V<br>V<br>V | $V_{TS} = 0 V$ $V_{TS} = V_{S}$ $V_{TS} = 0 V$ $V_{TS} = V_{S}$               |

| Input current at DI, ENA                                                                                             | $I_{DI, ENA}$                                                                    | 50                       |                            | 200               | μA               | $0.5 \text{ V} \le V_{\text{DI, ENA}}$ $\le 30 \text{ V}$                     |

| L-output voltage at SQ                                                                                               | $V_{\rm SQL}$                                                                    |                          |                            | 0.5               | V                | $I_{SQ} = 5 \text{ mA}$                                                       |

| Output current available <sup>1)</sup>                                                                               | I <sub>Q</sub><br>I <sub>Q</sub>                                                 | 1.5<br>1.7               | 2.5                        |                   | mA<br>mA         | $V_{Q} = V_{S} - 1.5 V$<br>$T_{A} = 0 \ ^{\circ}C$<br>$V_{Q} = V_{S} - 1.5 V$ |

| Current from TS                                                                                                      | $-I_{TS}$                                                                        |                          | 2                          | 10                | μA               | $V_{\rm Q} = V_{\rm S} = 1.5 \text{ V}$ $V_{\rm TS} = 0 \text{ V}$            |

| Switching threshold at W                                                                                             | $V_{W}$                                                                          | $V_{\rm S}$ – 0.6        | $V_{\rm S}$ – 0.5          | $V_{\rm S}$ – 0.4 | V                |                                                                               |

| Current in W<br>Current from C<br>Current in C                                                                       | $     I_{W}      - I_{C}      I_{C}   $                                          | 12<br>0.6                | 20<br>1                    | 100<br>34<br>1.7  | μΑ<br>μΑ<br>mA   | $T_{\rm A}$ = 20 °C<br>$T_{\rm A}$ = 20 °C                                    |

| Upper switching<br>threshold at C<br>Lower switching                                                                 | V <sub>CU</sub>                                                                  | 1.6                      | 2.1                        | 1.7               | V                | <i>T</i> <sub>A</sub> = 20 °C                                                 |

| threshold at C Saturation voltage at $T^{2}$                                                                         | $V_{ m CL}$<br>$V_{ m QR}$                                                       | 0.6                      | 0.9<br>V <sub>S</sub> -0.3 | 1.2               | V<br>V           | $T_{A} = 20 \text{ °C}$ $V_{W} = V_{S} - 2 \text{ V},$ $I_{Q} = 0$            |

| H-output voltage                                                                                                     | V <sub>QH</sub>                                                                  | V <sub>S</sub> –<br>0.25 | V <sub>S</sub> –<br>0.02   |                   | V                | $V_{\rm ENA} = 0  \rm V$                                                      |

<sup>1)</sup> The actual output current is typically 0.5 mA higher, a value which is required as current for the short-circuit protection. However, only the value specified above is available to drive the external output transistors.

<sup>2)</sup> See block diagram

### Schematic Circuit Diagram of One Stage

Mode of Operation: Switching-ON again after Overload with Key H

#### Mode of Operation: Automatic Switching-ON again after Overload

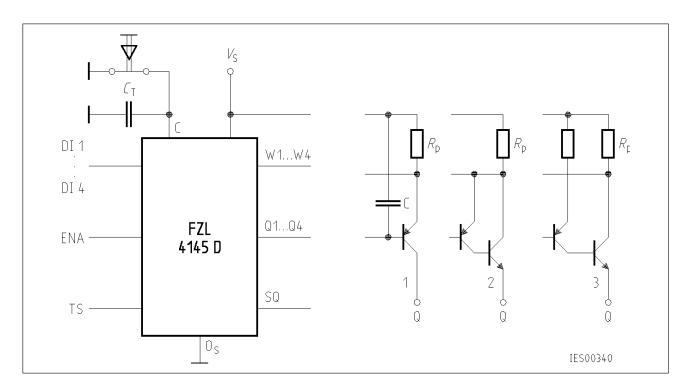

## **Typical Application Circuits**

The load conditions at Q depend on the permissible power dissipation of the used power transistors. The pulsed power dissipation in case of a short circuit must be observed.

In order to suppress oscillations of the power stage in case of a short circuit, a capacitor C at Q1 to Q4 is necessary if e.g. fast switching transistors are used.

Typical value X of C: approx. 20 nF.

The output circuit 1 is suited for currents up to approx.  $I_Q = 100$  mA.

The output circuit 2 and 3 are suited for currents up to approx.  $I_Q = 2 \text{ A}$ . A minimum power dissipation can be achieved with circuit 3.

A break key in parallel to  $C_{T}$  allows a manual switch-on in case of short-circuit.

$R_{\rm P}$  = Precision resistor (current measurement)

$C_{\rm T} = 0.8 \, {\rm x} \, t_{\rm p} \, ({\rm nF}, \, {\rm \mu s})$

$t_{\rm p}$  = Short-circuit current pulse length

**Note:** Circuit 1 does not permit a capacitor between Q1 and Q4 and the collector. Circuit 2 does not permit a capacitor between Q1 and Q4 and base or emitter, respectively.

Otherwise too high current spikes would arise in case of a short circuit.

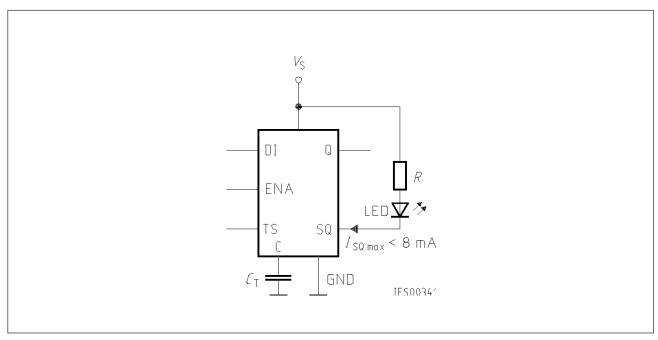

### **Typical Application of Short-Circuit Signaling Output SQ**

#### 1. LED Display

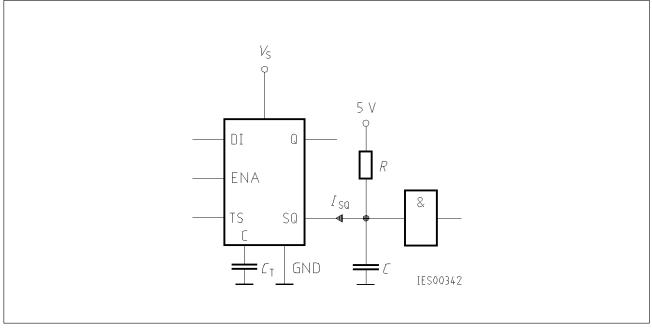

### 2. TTL/CMOS/LSL Driving

If the pulses appearing at SQ during clocked operation disturb the remainder of the circuit, a lowpass filter will be necessary. For a load current of  $I_{SQ} = 1 \text{ mA}$  a capacitor C of approx. 10 nF is necessary to limit the output pulses of up to 10 µs (depending on  $C_T$ ) to 1 V. Signaling occurs after approx. 50 µs.

## **Quad Driver Incl. Short-Circuit Signaling**

FZL 4146

#### **Bipolar IC**

#### Features

- Short-circuit signaling

- Four driver circuits for driving power transistors

- Turn-ON threshold setting from 1.5 to 7 V

| Туре       | Ordering Code | Package          |

|------------|---------------|------------------|

| FZL 4146 G | Q67000-H8743  | P-DSO-20-7 (SMD) |

#### **General Description**

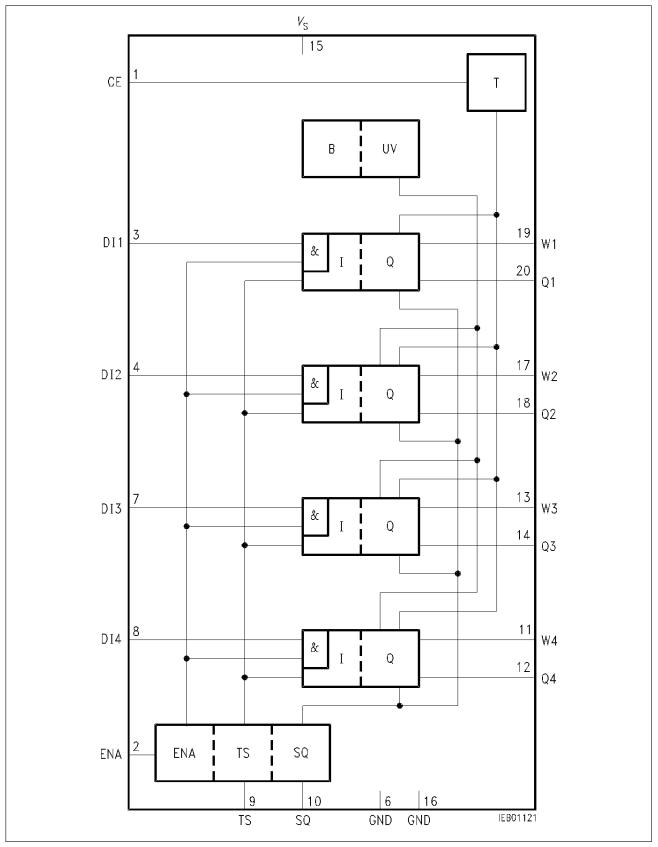

The IC comprises four driver circuits capable of driving power transistors (PNP or PMOS). The output transistors are protected against short-circuit to ground and supply voltage. The turn-ON threshold can be set from 1.5 V to 7 V. Overload at one or several outputs will be indicated at pin SQ (signaling output). The corresponding power transistors are then protected by changeover to clock-governed operation.

#### **Circuit Description**

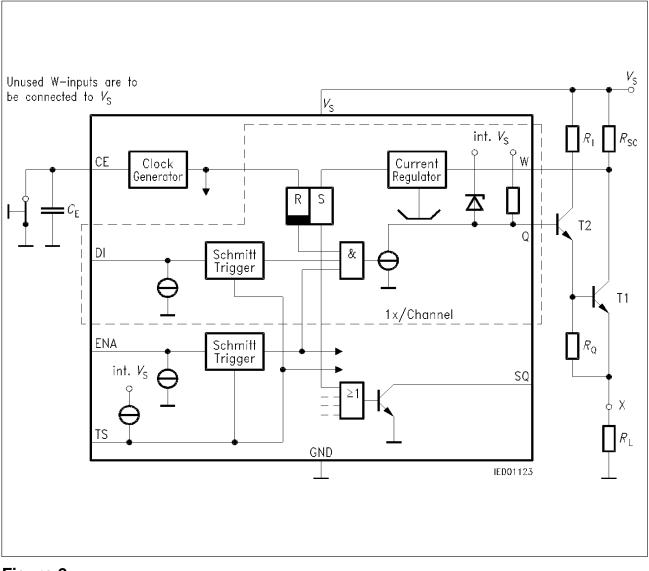

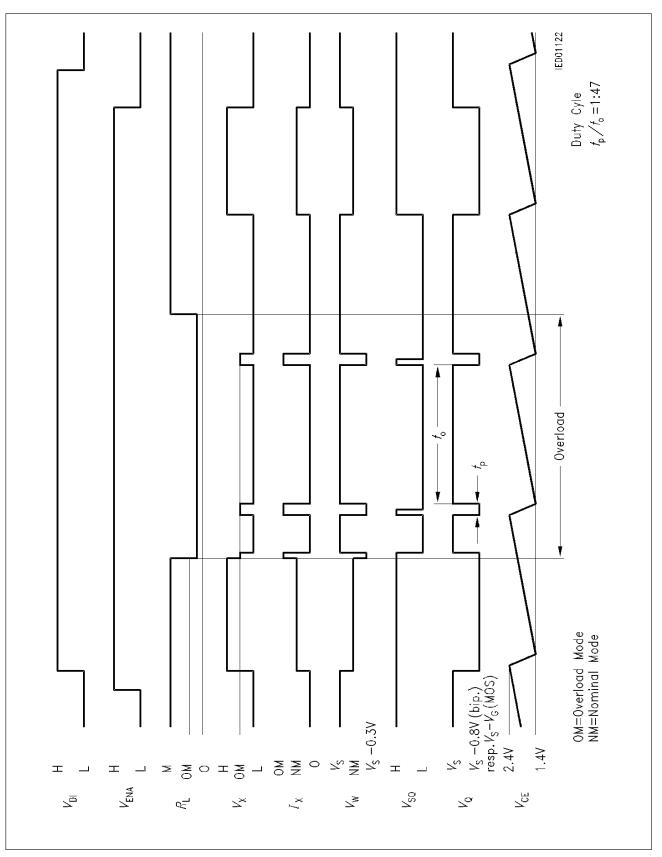

Each driver circuit has one active high driver input DI and a common enable input ENA (active high) is provided for all stages. The Q output is designed to drive the output transistors. The load current is sampled and, if necessary, limited via pin W. If the load current exceeds the preset value, the output stage switches off. Switching-ON again is provided by the built-in clock generator T. Its operation requires an external capacitor  $C_e$  at pin CE. If  $C_e$  is bridged by a break-key, switching-ON can only be carried out by operating a key. The duty cycle of the clock generator is 1:47 (e.g. 45  $\mu$ s/2.1 ms with  $C_e$  = 10 nF). The clock generator is previleged versus the current sensor shut down. When the supply is connected, the internal RS-FF goes into the state corresponding to the released output.

The turn-ON threshold at input DI and ENA can be set via pin TS from 1.5 to 7 V.

$V_{\text{TS}} = 0 \ \text{V} \dots 1.5 \ \text{V}$ Turn-ON threshold = 1.5 \ V $V_{\text{TS}} = 1.5 \ \text{V} \dots 1.5 \ \text{V}$ Turn-ON threshold =  $V_{\text{TS}}$  $V_{\text{TS}} = V_{\text{S}}$ Turn-ON threshold = 7 \ V

Inputs DI, ENA and W are proof against line break, i.e. an open input at DI or ENA corresponds to input L, open input W corresponds to overcurrent. If input TS is open, the highest turn-ON threshold is provided.

The internal current supply B and the undervoltage monitor UV ensure that in case of a supply voltage that is below the  $V_{\rm S}$  turn-OFF threshold, outputs Q and SQ are disabled and the inputs go high-impedance. Basic functioning is possible within the range from  $V_{\rm S}$  turn-OFF threshold to 4.5 V.

In case of overcurrent or short-circuit to ground at any output stage the signaling output (SQ) will go low. In clock-governed operation (i.e. when there is automatic switching-ON by the clock and not by a key), SQ goes high and low at the clock rate as long as a short-circuit or overload is present. SQ is an open-collector output.

Any input and output is ESD proof within the limit values.

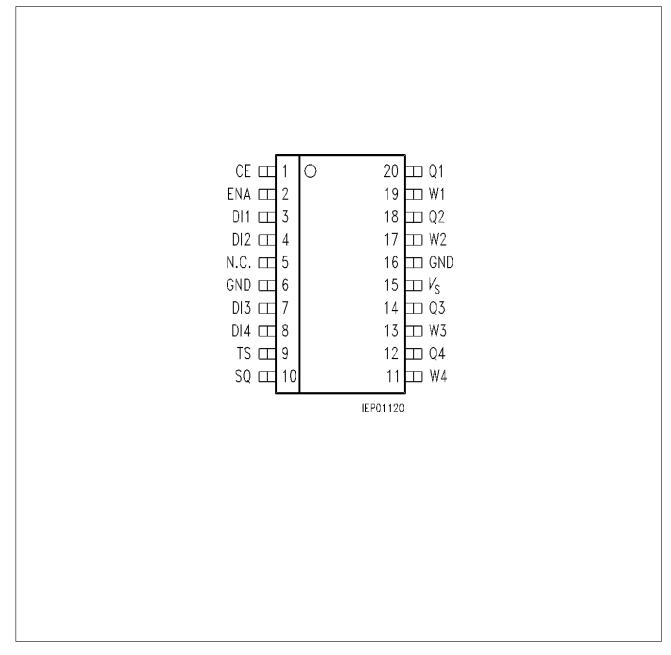

# **Pin Configuration** (top view)

## **Pin Definitions and Functions**

| Pin | Symbol | Function                                           |

|-----|--------|----------------------------------------------------|

| 1   | CE     | Pin for $C_{e}$                                    |

| 2   | ENA    | Enable input for drivers 1 to 4                    |

| 3   | DI1    | Input, driver 1                                    |

| 4   | DI2    | Input, driver 2                                    |

| 5   | N.C.   | Not connected                                      |

| 6   | GND    | Ground                                             |

| 7   | DI3    | Input, driver 3                                    |

| 8   | DI4    | Input, driver 4                                    |

| 9   | TS     | Threshold changeover for all inputs                |

| 10  | SQ     | Short-circuit signaling, output for drivers 1 to 4 |

| 11  | W4     | Output, current sensor driver 4                    |

| 12  | Q4     | Output, driver 4                                   |

| 13  | W3     | Output, current sensor driver 3                    |

| 14  | Q3     | Output, driver 3                                   |

| 15  | Vs     | Supply voltage                                     |

| 16  | GND    | Ground                                             |

| 17  | W2     | Output, current sensor driver 2                    |

| 18  | Q2     | Output, driver 2                                   |

| 19  | W1     | Output, current sensor driver 1                    |

| 20  | Q1     | Output, driver 1                                   |

# **Block Diagram**

Semiconductor Group

#### Absolute Maximum Ratings

| Parameter                       | Symbol                  | Limit \           | /alues          | Unit | Remarks                   |

|---------------------------------|-------------------------|-------------------|-----------------|------|---------------------------|

|                                 |                         | min.              | max.            |      |                           |

| Supply voltage                  | Vs                      | - 0.3             | 40              | V    |                           |

| Supply voltage                  | Vs                      | - 0.3             | 45              | V    | 100 ms,                   |

|                                 |                         |                   |                 |      | 5 s interval              |

| Supply voltage                  | Vs                      | - 0.3             | 48              | V    | 120 μs                    |

| Reverse supply current in GND   | I <sub>GND</sub>        |                   | 0.5             | А    | 1) 4)                     |

| Input voltage at DI and ENA, TS | $V_{DI, ENA, TS}$       | - 5               | 40              | V    |                           |

| Input voltage at DI and ENA, TS | $V_{DI, ENA, TS}$       | - 5               | 45              | V    | 100 ms,                   |

|                                 |                         |                   |                 |      | 5 s interval              |

| Output voltage Q                | $V_{Q}$                 | $V_{\rm S}-8$     | $V_{\sf S}$     | V    | min. (– 0.3 V)            |

| Current in Q                    | IQ                      | - 10              | 3               | mA   | 18)                       |

| Voltage on W                    | $V_{W}$                 | $V_{\rm S} - 6.5$ | $V_{\rm S}$ + 5 | V    | min. – 0.3 V,             |

| -                               |                         |                   | C               |      | max. 45                   |

| Voltage on W                    | V <sub>W</sub>          | $V_{\rm S} - 12$  | $V_{\rm S}$ + 5 | V    | min. – 0.3 V,             |

| -                               |                         | -                 | -               |      | max. 45 V <sup>2)</sup>   |

| Voltage on CE                   | V <sub>c</sub>          | - 0.3             | $V_{\sf S}$     | V    | min. – 0.3 V,             |

|                                 |                         |                   | -               |      | max. 45 V <sup>3)</sup>   |

| Voltage on SQ                   | $V_{ m SQ}$             | - 0.5             | 45              | V    | Output high               |

| Input current DI, ENA, TS       | V <sub>DI, ENA, T</sub> | - 3               | 3               | mA   | 4)                        |

|                                 |                         |                   |                 |      |                           |

| Input current DI, ENA, TS       | V <sub>DI, ENA, T</sub> | - 5               | 5               | mA   | 100 ms,                   |

| -                               |                         |                   |                 |      | 5 s interval              |

| Input current DI, ENA, TS       | $V_{DI, ENA, T}$        | - 10              | 10              | mA   | 10 μs, 500 μs<br>interval |

**Notes:** <sup>1)</sup> An adequate resistor in the GND line can provide protection in case of polarization of  $V_s$ . It should be noted, however, that in this case all pins may become conductive across GND.

<sup>2)</sup> Loading may lead to degradation and thus to a shift of the switching threshold at W. (Characteristics: switching threshold at W).

Short loading may lead to a deviation of approx. 20 mV.

$^{3)}$  In case of short-circuit of  $V_{\rm S}$ , the capacitance stored in  $C_{\rm e}$  during previous operation will not damage the IC.

<sup>4)</sup> Note the power loss.

#### Absolute Maximum Ratings (cont'd)

| Parameter                                                                                                                   | Symbol                                              | Limit              | Values                 | Unit                   | Remarks                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------|------------------------|------------------------|------------------------------------------------------------------------------------------------|

|                                                                                                                             |                                                     | min.               | max.                   |                        |                                                                                                |

| Current in SQ<br>Current in W<br>Current in W                                                                               | I <sub>SQ</sub><br>I <sub>W</sub><br>I <sub>W</sub> | - 3<br>- 5<br>- 10 | 8<br>5<br>10           | mA<br>mA<br>mA         | Output low<br>1 ms, 50 ms<br>interval <sup>5)</sup><br>10 μs, 500 μs<br>interval <sup>5)</sup> |

| Junction temperature<br>Storage temperature<br>Therm. resistance,<br>system-ambient<br>Therm. resistance,<br>system-packag. | $T_{ m stg}$<br>$R_{ m th~SA}$<br>$R_{ m th~SP}$    | - 40<br>- 50       | 150<br>150<br>95<br>25 | °C<br>°C<br>K/W<br>K/W | 6)                                                                                             |

| ESD strength acc. to MIL -<br>hrs. 883 Meth. 3015<br>(100 pF/1.5 kΩ,<br>5 discharges/polarity)                              | V <sub>ESD</sub>                                    | -2                 | 2                      | kV                     |                                                                                                |

| Burst strength of the inputs/<br>outputs Q and W connected to<br>the power transistors (in acc.<br>with IEC publ. 801-4)    | V <sub>Burst</sub>                                  | 300                |                        | V                      | 7)                                                                                             |

| Junction temperature in normal operation during 15 years with 100 % ED                                                      | <i>T</i> <sub>j15</sub>                             |                    | 125                    | °C                     | 8)                                                                                             |

**Notes:** <sup>5)</sup> Loading may lead to degradation and thus to a shift of the switching threshold at W. Unfrequent loading leads to a deviation of approx. 20 mV.

<sup>6)</sup> Related to GND; the GND pins are connected with the chip carrier via the leadframe.

<sup>7)</sup> If it can be prooved with samples.

<sup>8)</sup> During normal operation, the failure rate is  $\leq$  100 fit acc. to SN 29500 at a junction temperature of 75 °C.

#### **Operating Range**

| Parameter                                                                                                              | Symbol                                              | Limit                                  | Values              | Unit                | Remarks                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                        |                                                     | min.                                   | max.                |                     |                                                                                                                             |

| Supply voltage <sup>11)</sup><br>Supply voltage <sup>12)</sup><br>Supply voltage <sup>13)</sup><br>Supply voltage rise | $V_{\rm S}$ $V_{\rm S}$ $V_{\rm S}$ $dV_{\rm S}/dt$ | 4.5<br>V <sub>s</sub> + 3<br>10<br>- 1 | 40<br>40<br>40<br>1 | V<br>V<br>V<br>V/μs | $V_{\text{TS}} = 0 \dots 1.5 \text{ V}$<br>$V_{\text{TS}} = 1.5 \dots 7 \text{ V}$<br>$V_{\text{TS}} = V_{\text{S}}$<br>20) |

| Junction temperature                                                                                                   | Tj                                                  | 1                                      | 150                 | °C                  |                                                                                                                             |

| Time-determining capacitor of the clock generator                                                                      | Ce                                                  | 1                                      | 100                 | nF                  | 10)                                                                                                                         |

| Input voltage                                                                                                          | $V_{ m DI,\ ENA,\ TS}$                              | - 2                                    | 40                  | V                   | 14) 15) 16) 17) 19)                                                                                                         |

| Current at output SQ                                                                                                   | I <sub>SQ</sub>                                     | - 1                                    | 6                   | mA                  |                                                                                                                             |

**Notes:** <sup>9)</sup> W pins that remain open, must be connected to  $V_{\rm S}$ .

- <sup>10)</sup> The  $C_{\rm e}$  value depends on the desired pulse width  $t_{\rm p}$  during short circuit. It applies:  $C_{\rm e} = 0.25$  mS x  $t_{\rm p}$ .

- <sup>11)</sup> At an input threshold = 1.5 V

- <sup>12)</sup> At an input threshold = 1.5 V to 7 V

- <sup>13)</sup> At an input threshold = 7 V

- <sup>14)</sup> This function is also ensured for 40 V  $\leq V_{\rm S} \leq$  45 V and 40 °C  $\leq T_{\rm j} \leq$  25 °C as long as 0 V  $\leq V_{\rm DI, ENA, TS} \leq$  40 V.

- <sup>15)</sup> The outputs Q are disabled even if  $-3 \text{ V} \le V_{\text{DI, ENA}} \le -2 \text{ V}$  or  $-1 \text{ mA} \le V_{\text{DI, ENA}} \le 50 \text{ }\mu\text{A}$  and  $V_{\text{S}} 5 \text{ V} \le V_{\text{W}} \le V_{\text{S}} + 5 \text{ V}$ , max. 45 V.

- <sup>16)</sup> The outputs Q are enabled even if 40 V  $\leq V_{I, ENA} \leq$  45 V and  $V_S 0.2$  V  $\leq V_W \leq V_S + 5$  V, max. 45 V.

- <sup>17)</sup> Current limiting and disabling of outputs Q are ensured even if 40 V  $\leq V_{DI, ENA} \leq$  45 V and  $V_{S} 5 V \leq V_{W} \leq V_{S} 0.4 V$ .

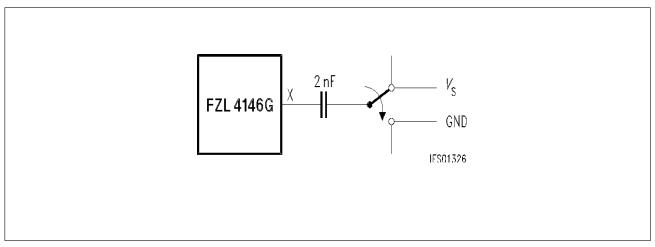

- <sup>18)</sup> Dynamic charge reversal of a 2-nF capacitor as in **figure** 1 is permissible (corresponds to short circuit to conducting output in P-channel MOSFET)

- <sup>19)</sup> Proper working of the IC is also ensured if, before  $V_{\rm S}$  is turned-On, an input voltage  $V_{\rm DI, ENA}$  is present in the permissible range (footnote 15).

### Characteristics

Supply voltage 4.5 V  $\leq V_{\rm S} \leq$  40 V, junction temperature – 25 °C  $\leq T_{\rm j} \leq$  125 °C

| Parameter                                        | Symbol                       | L                        | imit Valu               | ues                      | Unit     | Test Condition                                                                                                                         |

|--------------------------------------------------|------------------------------|--------------------------|-------------------------|--------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                              | min.                     | typ.                    | max.                     | -        |                                                                                                                                        |

| Current consumption                              | $I_{ m s,  OFF}$             |                          |                         | 5                        | mA       | $V_{\rm ENA} = 0 \text{ V},$ $V_{\rm w} = V_{\rm S}^{4}$                                                                               |

| Current consumption                              | $I_{\rm s,  ON}$             |                          |                         | 13.5                     | mA       | $V_{\text{ENA}} = V_{\text{DI}} = V_{\text{w}} = V_{\text{Q}} = V_{\text{S}}; V_{\text{TS}} = 0 \text{ V}^{3}$                         |

| H-input voltage<br>at DI, ENA<br>H-input voltage | V <sub>IH</sub>              | 2                        |                         |                          | V        | $V_{\rm TS} = 0 \ { m V}$                                                                                                              |

| at DI, ENA<br>L-input voltage                    | $V_{IH}$                     | 6.8                      |                         |                          | V        | $V_{\rm TS} = V_{\rm S}$                                                                                                               |

| at DI, ENA<br>L-input voltage                    | $V_{\rm IL}$                 |                          |                         | 0.7                      | V        | $V_{\rm TS}$ = 0 V                                                                                                                     |

| at DI, ENA                                       | VIL                          |                          |                         | 4.8                      | V        | $V_{\rm TS} = V_{\rm S}$                                                                                                               |

| Input hysteresis                                 | $V_{HI}$                     | 30                       | 100                     | 300                      | mV       | $0 V \le V_{TS} \le V_S$                                                                                                               |

| Input current DI, ENA <sup>1), 7)</sup>          | I <sub>DI, ENA</sub>         | 50                       |                         | 200                      | μA       | $1.5 \text{ V} \le V_{\text{DI, ENA}} \le 30 \text{ V}$                                                                                |

| Input current DI, ENA                            | $I_{DI0, ENA0}$              |                          |                         | 100                      | μA       | $\begin{array}{l} 0 \hspace{0.1cm}V \leq V_{DI, ENA} \\ \leq 30 \hspace{0.1cm}V, \hspace{0.1cm} V_{S} = 0 \hspace{0.1cm}V \end{array}$ |

| L-output voltage at SQ                           | $V_{\rm SQL}$                |                          |                         | 0.5                      | V        | $I_{\rm SQ}$ = 5 mA,<br>$V_{\rm W}$ = $V_{\rm S}$ – 2 V                                                                                |

| Leakage current<br>output SQ                     | I <sub>SQ H</sub>            |                          |                         | 10                       | μA       | $V_{\rm W} = V_{\rm S}$                                                                                                                |

| Output current Q                                 | $I_{Q0}$                     | 0.6                      |                         | 1.6                      | mA       | $V_{\rm S}$ – 2 V $\leq$ $\leq$ $V_{\rm Q}$ $\leq$ $V_{\rm S}$                                                                         |

| Current from TS<br>Current in W                  | $-I_{\rm TS}$<br>$I_{\rm W}$ | 2                        | 5                       | 10<br>100                | μΑ<br>μΑ | $V_{\mathrm{TS}} = 0.7 \mathrm{V}$<br>$V_{\mathrm{S}} - 2 \mathrm{V} \le V_{\mathrm{W}} \le V_{\mathrm{S}}$                            |

| Switching threshold at $W^{2)}$                  | $V_{W}$                      | V <sub>S</sub> –<br>0.25 | V <sub>S</sub> –<br>0.3 | V <sub>S</sub> –<br>0.35 | V        |                                                                                                                                        |

Notes see page 11.

### Characteristics (cont'd)

Supply voltage 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  40 V, junction temperature – 25 °C  $\leq$  T<sub>j</sub>  $\leq$  125 °C

| Parameter                                                                                 | Symbol                                   | L                         | imit Valı | ues              | Unit           | Test Condition                                                                                               |

|-------------------------------------------------------------------------------------------|------------------------------------------|---------------------------|-----------|------------------|----------------|--------------------------------------------------------------------------------------------------------------|

|                                                                                           |                                          | min.                      | typ.      | max.             | -              |                                                                                                              |

| Current in W<br>Current from CE<br>Current in CE                                          | $I_{\rm W} - I_{\rm Ce}$<br>$I_{\rm Ce}$ | 12<br>0.6                 | 20<br>1   | 100<br>34<br>1.7 | μΑ<br>μΑ<br>mA | $T_{\rm A}$ = 20 °C<br>$T_{\rm A}$ = 20 °C                                                                   |

| Charge current<br>from CE<br>Discharge current<br>from CE                                 | — I <sub>Ce</sub><br>I <sub>Ce</sub>     |                           | 5<br>235  |                  | μΑ<br>μΑ       |                                                                                                              |

| Upper switching<br>threshold at CE<br>Lower switching<br>threshold at CE                  | V <sub>CU</sub><br>V <sub>CL</sub>       |                           |           | 2.4<br>1.4       | V<br>V         |                                                                                                              |

| $V_{\rm Q}$ at overcurrent                                                                | $V_{\sf QR}{}^{6)}$                      | V <sub>S</sub> –<br>0.4 V |           |                  | V              | $V_{\rm W} = V_{\rm S} - 2 {\rm V},$<br>$I_{\rm Q} = -20 {\rm \mu A}$                                        |

| $V_{\rm Q}$ at output disable                                                             | $V_{\sf QL}$ <sup>6)</sup>               | V <sub>S</sub> –<br>0.4 V |           |                  | V              | $V_{\rm ENA} = 0 \text{ V},$<br>$I_{\rm Q} = -20 \mu\text{A},$<br>$0 \text{V} \le V_{\rm S} \le 40 \text{V}$ |

| Signal run time LH                                                                        | t <sub>PLH</sub>                         |                           |           | 50               | μs             |                                                                                                              |

| Signal run time HL                                                                        | t <sub>PHL</sub>                         |                           |           | 50               | μs             |                                                                                                              |

| Pulse width                                                                               | t <sub>P</sub>                           | 33                        | 45        | 65               | μs             | C <sub>e</sub> = 10 nF                                                                                       |

| Duty cycle                                                                                | $t_{\rm P}/t_0$                          | 1:55                      | 1:47      | 1:40             |                | <i>C</i> <sub>e</sub> = 10 nF                                                                                |

| Delay time of the short-circuit signaling                                                 | <i>t</i> <sub>PWM</sub> <sup>5)</sup>    |                           |           | 10               | μs             | $V_{\rm C} = 0 \ {\rm V}$                                                                                    |

| Duration of the<br>negative spikes at<br>input W, which do not<br>result in switching off | t <sub>vz</sub>                          | 1                         |           |                  | μs             |                                                                                                              |

Notes see page 11.

#### Characteristics (cont'd)

Supply voltage 4.5 V  $\leq V_{\rm S} \leq$  40 V, junction temperature – 25 °C  $\leq T_{\rm i} \leq$  125 °C

| Parameter                                                                                       | Symbol                 | Limit Values           |                          |                        | Unit | Test Condition                                                                                                                               |

|-------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                 |                        | min.                   | typ.                     | max.                   |      |                                                                                                                                              |

| Difference between $V_{TS}$ and input switching threshold ENA, DI during transition from L to H | $V_{DIH-}$<br>$V_{TS}$ | - 0.2                  |                          | 0.2                    | V    | V <sub>TS</sub> = 2 4.8 V                                                                                                                    |

| Idling voltage at<br>output Q                                                                   | $V_{QH}$               | V <sub>s</sub> –<br>13 | V <sub>s</sub> –<br>11.5 | V <sub>s</sub> –<br>10 | V    | $V_{\rm S} \ge 18 \ { m V}$                                                                                                                  |

| $V_{s}$ turn-Off threshold                                                                      | $V_{ m TSV}$           | 2.5                    |                          | 4.5                    | V    | $V_{\rm Q} > V_{\rm QL};$<br>$I_{\rm Q} = -20 \mu\text{A}$                                                                                   |

| Resistance across Q and $V_{\rm S}$                                                             | R <sub>Q</sub>         | 8                      | 13                       | 19                     | kΩ   | $V_{\rm ENA} = 0 \text{ V};$<br>$I_{\rm Q} = -100 \mu\text{A}$<br>$R_{\rm Q} = (V_{\rm S} - V_{\rm Q})/$<br>0.1 mA                           |

| Z-diode<br>internal resistance                                                                  | R <sub>Z</sub>         |                        | 20                       | 50                     | Ω    | $V_{\rm ENA} = 0 \text{ V};$<br>$I_{\rm Q1} = -3 \text{ mA}$<br>$I_{\rm Q2} = -8 \text{ mA},$<br>$R_{\rm Q} = \Delta V_{\rm Q}/5 \text{ mA}$ |

#### **Footnotes for the Characteristics**

- <sup>1)</sup> The given limit values apply to inputs DI, ENA, if they are not measured, from 0 to 40 V.

- <sup>2)</sup> The layout provides an adaption of  $V_{wtyp}$  from  $V_s 0.3$  V to  $V_s 0.4$  V or  $V_s 0.48$  V by simply changing of the ALU mask.

- <sup>3)</sup> All inputs DI1 to DI4 and W1 to W4 as well as Q1 to Q4  $I_{SON}$  means the sum of all currents flowing from the voltage source  $V_{S}$  into the IC, i.e.  $I_{SON} = I_{S} + \Sigma I_{DI} + \Sigma I_{ENA} + \Sigma I_{W} + \Sigma I_{Q}$ .

- <sup>4)</sup> All other pins are open.

- <sup>5)</sup> The delay time of loop W → I regulator → RS-FF AND → current source → Q is un accessable for measurement without external wiring due to fast reaction of the current regulator. For this reason, in case of overload, the above mentioned switch-OFF delay time is replaced by the delay time for input W → output SQ.

Measurement: jump function at W from  $V_{\rm W} = V_{\rm S}$  to  $V_{\rm W} = V_{\rm S} - 1$  V

- <sup>6)</sup> IQ = leakage current  $I_{CBO}$  of the external PNP-driver transistor

- <sup>7)</sup> For  $V_{ID, TS} < 1.5$  V,  $I_{DI, ENA}$  remains below its minimum value; it is however ensured that in case of open inputs the corresponding outputs will be safely disabled.

### Figure 1

#### Figure 2 Application Circuit

Semiconductor Group

Figure 3 Operating Mode: Automatic Turn-ON after Overload