# Intel® IXF6402 Broadband Access Processor

#### **Product Overview**

The Intel® IXF6402 is a fourth-generation 64-bit Broadband Access Processor capable of formatting and provisioning a broad range of high-speed network traffic types. These include frames, cells, and packets at broadband data rates of up to 622Mbps full duplex, or up to 2.4Gbps in a multi-engine configuration. Implemented in low-power CMOS process technology, the IXF6402 has a 66/100MHz/64-bit PCI interface and offers a high-speed local memory bus, list and buffer management, DMA, traffic shaping, accounting, tagging, and packet encapsulation engine—all in a single, integrated package.

The Intel® IXF6402 Broadband Access Processor can significantly benefit developers by helping:

- Minimize research and development cycles

- Provide comprehensive system design

- Enable granular and efficient traffic shaping

- Provide extremely low latency

- Offer connectivity to both SONET and ATM backbones

- Multi-port POS support

- Programmable VC/VP shaping

### Key Applications

- Edge/access devices

- Switches and routers

- DSLAMs

- Internet media servers

- VoIP gateways

- ATM switches

- Storage area networking platforms

- Networking interface cards (NICs)

- Multi-access concentrators

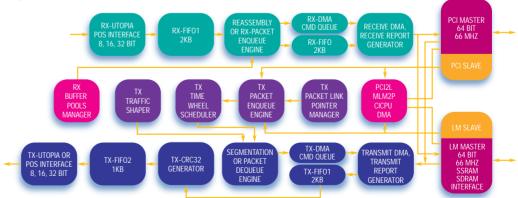

## Chip Architecture

Intel

Internet Exchange

**Architecture**

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Benefits                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| <ul> <li>Integrated ATM OC-12c SAR, multi-chip OC-48</li> <li>Full-duplex line rate operation for 64-byte packets</li> <li>64-bit state machine architecture</li> <li>Hardware encapsulation and tagging</li> <li>Hardware packet formatting</li> <li>66/100MHz Local Memory Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           | ■ Highest performance                      |

| <ul> <li>Up to 64K VC/VPs per transmit and receive</li> <li>Traffic shaping resources for CBR, VBR</li> <li>Granularity for rates down to 1 Kbps</li> <li>Time wheel scheduling for ABR and other traffic types</li> <li>Automates FRM cell generation and MCR support for ABR</li> <li>UBR support</li> <li>Dual GCRA policing per VC or VP</li> <li>Weighted fair queuing and dynamic priority arbitration</li> <li>UBR fill-in cells for maximum bandwidth utilization</li> </ul>                                                                                                                                                                                                        | ■ Extensive traffic shaping and policing   |

| <ul> <li>LEC ID, ELAN ID, LLC/SNAP, MPOA, IP encapsulations</li> <li>64-byte header</li> <li>Programmable header encapsulation and tagging</li> <li>LANE, MPOA, MPLS, and IP protocol assist</li> <li>Support for both packet and VC tagging</li> <li>Support for per-packet tagging in receive</li> <li>Support for 32-bit cell-or-packet counters for receive</li> <li>Ability to report the LSB 16-bit of the 32-bit cell-or-packet counter in the receive buffer report, removing need for an additional read operation</li> <li>Support for transmit per packet offset up to 256 bytes</li> <li>Support for receive start-of-packet offset for per-packet and/or per-buffer</li> </ul> | ■ Upper Layer Assist                       |

| <ul> <li>AAL types 0, 1, and 3/4, 5</li> <li>TM 4.0 compliant</li> <li>Flow control: UBR-H, UBR, CBR, VBR, VBR-rt, ABR</li> <li>Full 64-byte VC descriptors</li> <li>Scalable to OC-48</li> <li>ATM/POS UTOPIA support</li> <li>Support for multi-port POS</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       | ■ Feature rich                             |

| <ul> <li>Dual-port OC-12c or quad OC-3c</li> <li>Glueless 64-bit SSRAM and SDRAM interface</li> <li>PCI 2.1 compliant 33/66MHz, 32/64-bit operation</li> <li>UTOPIA levels 1, 2, and via mux</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ■ Multiple interfaces for flexible options |

| <ul> <li>Full scatter/gather DMA for SAR</li> <li>Extensive transmit and receive buffering</li> <li>Two-dimensional link-list packet queuing</li> <li>64K internal transmit product descriptor and packet buffer pools; 36K internal buffer</li> <li>Multiple buffer sizes and cell splitting</li> <li>Support for four-bank structured SDRAM</li> </ul>                                                                                                                                                                                                                                                                                                                                    | ■ Sophisticated buffer management          |

| <ul> <li>2.5V/3.3V tolerant I/Os</li> <li>0.25µm CMOS design, 2.5V</li> <li>352-pin EBGA/ABGA package (Industrial or Commercial Temp) -40° to 85°C</li> <li>Pin compatible with Intel® IXF6401</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ■ State-of-the-art process technology      |

### Support Collateral/Tools

| ( | Item              | Description                          | Order Number |

|---|-------------------|--------------------------------------|--------------|

|   | Data Sheet        | ■ IXF6402 Broadband Access Processor | 273472       |

|   | Developers Manual | ■ IXF6402                            | 273453       |

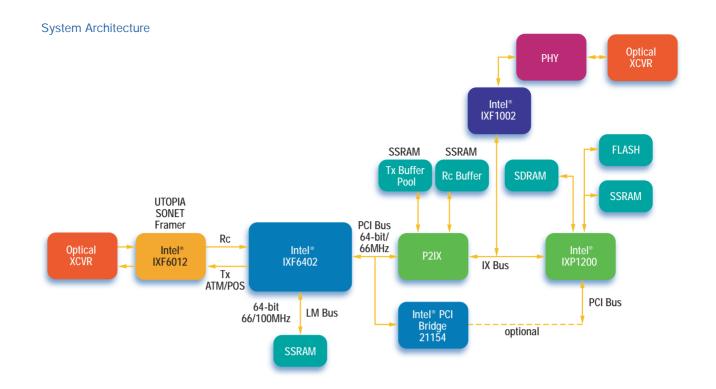

### Intel® Internet Exchange Architecture

Intel® Internet Exchange Architecture (IXA) is an end-to-end family of high-performance, flexible and scalable hardware and software development building blocks designed to meet the growing performance requirements of today's networks. Based on programmable silicon and software building blocks, Intel® IXA solutions enable faster development, more cost-effective deployment, and future upgradability of network and communications systems. Additional information can be found at www.intel.com/IXA.

### Intel Access

| Developer Web Site                              | http://developer.intel.com                                                                                                                                       |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel® Internet Exchange Architecture Home Page | http://intel.com/IXA                                                                                                                                             |

| Networking Components Home Page                 | http://developer.intel.com/design/network                                                                                                                        |

| Intel Literature Center                         | http://developer.intel.com/design/litcentr (800) 548-4725 7 a.m. to 7 p.m. CST (U.S. and Canada) International locations please contact your local sales office. |

| General Information Hotline                     | (800) 628-8686 or (916) 356-3104 5 a.m. to 5 p.m. PST                                                                                                            |

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right. Intel products are not intended for use in medical, life-saving or life-sustaining applications. Intel may make changes to specifications and product descriptions at anytime, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked \*reserved\* or \*undefined.\* Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

For more information, visit the Intel Web site at: developer.intel.com

UNITED STATES AND CANADA Intel Corporation Robert Noyce Building 2200 Mission College Blvd. P.O. Box 58119 Santa Clara, CA 95052-8119 USA

EUROPE Intel Corporation (UK) Ltd. Pipers Way Swindon Wiltshire SN3 1RJ UK

ASIA-PACIFIC Intel Semiconductor Ltd. 32/F Two Pacific Place 88 Queensway, Central Hong Kong, SAR

JAPAN Intel Japan (Tsukuba HQ) 5-6 Tokodai, Tsukuba-shi 300-2635 Ibaraki-ken

SOUTH AMERICA Intel Semicondutores do Brasil LTDA Rua Florida, 1703-2 and CJ 22 04565-001 Sao Paulo, SP Brazil