# LM9801

LM9801 8-Bit Greyscale/24-Bit Color Linear CCD Sensor Processor

Literature Number: SNOS870

April 1998

LM9801 8-Bit Greyscale/24-Bit Color Linear

· CCD

Sensor Processor

National Semiconductor

# LM9801 8-Bit Greyscale/24-Bit Color Linear CCD Sensor Processor

# **General Description**

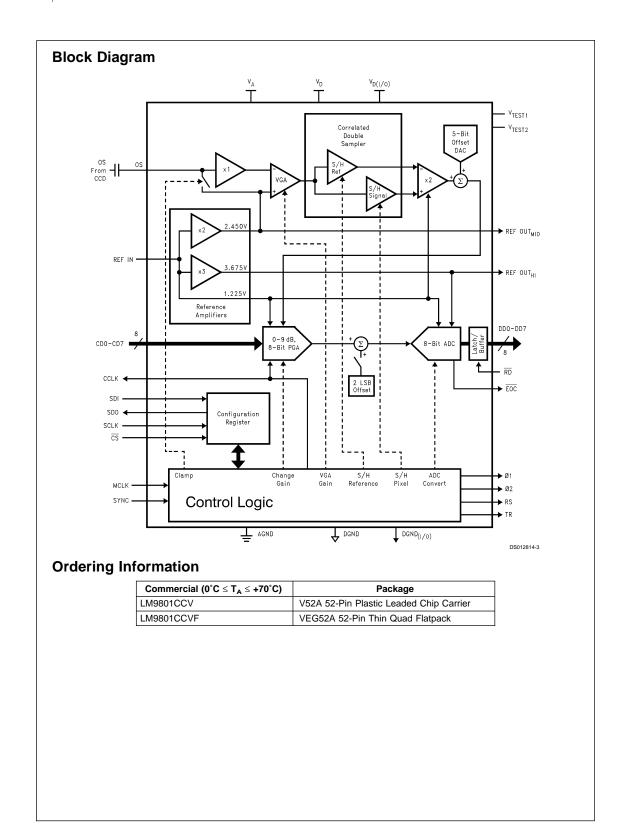

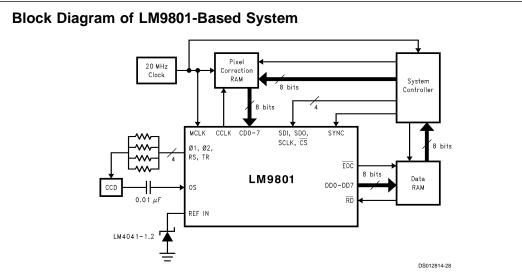

The LM9801 is a high performance integrated signal processor/digitizer for linear CCD image scanners. The LM9801 performs all the analog processing (correlated double sampling for black level and offset compensation, pixel-by-pixel gain (shading) correction, and 8-bit analog-to-digital conversion) necessary to maximize the performance of a wide range of linear CCD sensors.

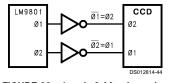

The LM9801 can be digitally programmed to work with a wide variety of CCDs from different manufacturers. An internal configuration register sets CCD and sampling timing to maximize performance, simplifying the design and manufacturing processes.

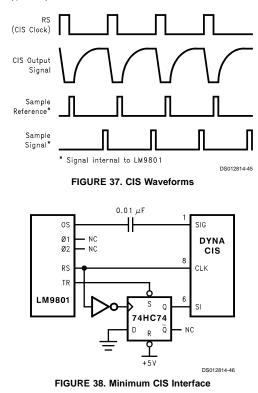

The LM9801 can be used with parallel output color CCDs. A signal inversion mode eases use with CIS sensors. For complementary voltage reference see the LM4041.

# Applications

- Color and Greyscale Flatbed and Sheetfed Scanners

- Fax and Multifunction Peripherals

- Digital Copiers

- General Purpose Linear CCD Imaging

#### Features

- 2.5 Million pixels/s conversion rate

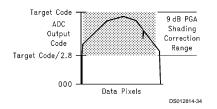

- Pixel-rate shading correction for individual pixels maximizes dynamic range and resolution, even on "weak" pixels

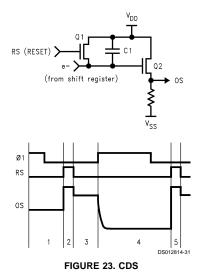

- Implements Correlated Double Sampling for minimum noise and offset error

- Reference and signal sampling points digitally controlled in 25 ns increments for maximum performance

- Generates all necessary CCD clock signals

- Compatible with a wide range of linear CCDs

- Supports some Contact Image Sensors (CIS)

- TTL/CMOS input/output compatible

# **Key Specifications**

| Resolution:            | 8 Bits                  |

|------------------------|-------------------------|

| Pixel Conversion Rate: | 2.5 MHz                 |

| Supply Voltage:        | +5V ± 5%                |

| Supply Voltage         |                         |

| (Digital I/O):         | +3.3V ± 10% or +5V ± 5% |

| Power Dissipation:     | 260 mW (max)            |

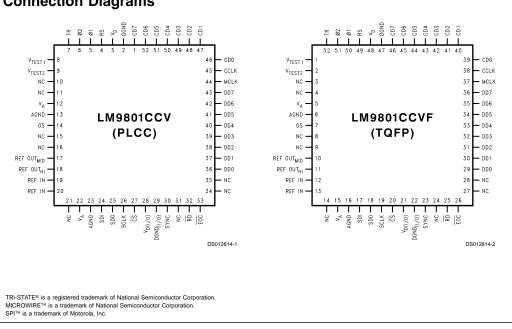

# **Connection Diagrams**

# Absolute Maximum Ratings (Notes 2, 1)

# **Operating Ratings** (Notes 1, 2)

| Positive Supply Voltage ( $V^+ = V_A = V_D$<br>with Respect to GND = AGND = DGI | ()                           |

|---------------------------------------------------------------------------------|------------------------------|

| DGND <sub>(I/O)</sub>                                                           | 6.5V                         |

| Voltage on any Input or Output Pin                                              | 0.3V to V <sup>+</sup> +0.3V |

| Input Current at any Pin (Note 3)                                               | ±25 mA                       |

| Package Input Current (Note 3)                                                  | ±50 mA                       |

| Package Dissipation at T <sub>A</sub> = 25°C                                    | (Note 4)                     |

| ESD Susceptibility (Note 5)                                                     |                              |

| Human Body Model                                                                | 2000V                        |

| Soldering Information (Note 6)                                                  |                              |

| Infrared, 10 seconds                                                            |                              |

| LM9801CCV                                                                       | 300°C                        |

| LM9801CCVF                                                                      | 220°C                        |

| Storage Temperature                                                             | –65°C to +150°C              |

Operating Temperature Range LM9801CCV, LM9801CCVF  $V_A$  Supply Voltage  $V_D$  Supply Voltage  $V_{D(I/O)}$  Supply Voltage  $|V_A-V_D|$  $V_A-V_D(I/O)$ OS, REF IN Voltage Range CD0-CD7, MCLK, SYNC, SDI, SCLK,  $\overline{CS}$ ,  $\overline{RD}$

Voltage Range

$$\begin{split} T_{\text{MIN}} &\leq T_{\text{A}} \leq T_{\text{MAX}} \\ 0\text{`C} \leq T_{\text{A}} \leq +70\text{`C} \\ +4.75\text{V to} +5.25\text{V} \\ +4.75\text{V to} +5.25\text{V} \\ +2.7\text{V to} +5.25\text{V} \\ \leq 100 \text{ mV} \\ \geq -100 \text{ mV} \\ -0.05\text{V to} \text{V}_{\text{A}} + 0.05\text{V} \end{split}$$

–0.05V to V<sub>D(I/O)</sub> + 0.05V

# **Electrical Characteristics**

The following specifications apply for AGND = DGND = DGND(I/O) = 0V,  $V_A = V_D = +5.0V_{DC}$ ,  $V_{D(I/O)} = +5.0 \text{ or } +3.0V_{DC}$ , REF IN = +1.225 $V_{DC}$ ,  $f_{MCLK} = 20$  MHz,  $R_S = 25\Omega$ . All LSB units are ADC LSBs unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25$ °C. (Note 8)

| Symbol             | Parameter                                  | Conditions                                                            | Typical    | Limits    | Units      |

|--------------------|--------------------------------------------|-----------------------------------------------------------------------|------------|-----------|------------|

|                    |                                            |                                                                       | (Note 9)   | (Note 10) | (Limits)   |

| CCD SO             | URCE REQUIREMENTS FOR FULL SPE             | CIFIED ACCURACY AND DYNAMIC                                           | RANGE (Not | te 11)    |            |

| V <sub>WHITE</sub> | Maximum Peak CCD Differential              | VGA Gain = 0 dB                                                       |            | 1.1       | V (min)    |

|                    | Signal Range                               | VGA Gain = 9 dB                                                       |            | 0.4       | V (min)    |

| $V_{RFT}$          | Maximum CCD Reset FeedThrough<br>Amplitude |                                                                       | 2          |           | V (min)    |

| ADC CH             | ARACTERISTICS                              |                                                                       |            |           |            |

|                    | Resolution with No Missing Codes           |                                                                       |            | 8         | Bits (min) |

| ILE                | Integral Linearity Error (Note 12)         |                                                                       |            | ±1.5      | LSB (max)  |

| DNL                | Differential Non-Linearity                 |                                                                       |            | ±1.0      | LSB (max)  |

| PGA CH             | ARACTERISTICS                              |                                                                       | 1          |           |            |

|                    | Monotonicity                               |                                                                       |            | 8         | Bits (min) |

|                    | PGA Adjustment Range                       | $\frac{\text{Gain}_{\text{PGA}} = 255}{\text{Gain}_{\text{PGA}} = 0}$ | 2.95       | 2.8       | V/V (min)  |

|                    | Gain Error at any Gain (Note 14)           |                                                                       |            | 1.4       | % (max)    |

| VGA CH             | ARACTERISTICS                              |                                                                       |            |           | `          |

|                    | Monotonicity                               |                                                                       |            | 4         | Bits (min) |

|                    | VGA Adjustment Range                       | $20 log \left( \frac{Gain_{VGA} = 15}{Gain_{VGA} = 0} \right)$        | 8.95       | 8.5       | dB (min)   |

|                    | Gain Error at any Gain (Note 15)           |                                                                       |            | ±0.15     | dB (max)   |

| OFFSET             | TRIM CHARACTERISTICS                       |                                                                       | 1          |           |            |

|                    | Offset DAC LSB Size                        | In Units of ADC LSBs                                                  | 0.42       |           | LSB        |

|                    | Offset DAC DNL                             | In Units of Offset DAC LSBs                                           | ±0.25      | ±0.9      | LSB (max)  |

|                    |                                            |                                                                       |            | 1.6       | LSB (min)  |

|                    | Offset Add Magnitude                       | In Units of ADC LSBs                                                  | 2.0        | 2.5       | LSB (max)  |

| SYSTEM             | CHARACTERISTICS                            |                                                                       |            | 1         |            |

|                    | Full Channel Gain Error                    | VGA Gain = 1, PGA Gain = 1                                            | ±0.6       | ±3.0      | % (max)    |

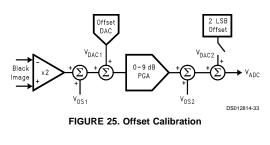

| V <sub>OS1</sub>   | Pre-PGA Offset Error                       | VGA Gain = 1, Offset DAC = 0                                          | ±1         |           | LSB        |

| V <sub>OS2</sub>   | Post-PGA Offset Error                      | Offset Add = 0                                                        | ±1         |           | LSB        |

|                    | NCE AND ANALOG INPUT CHARACTER             | RISTICS (Note 7)                                                      | L          |           | L          |

|                    | OS Input Capacitance                       |                                                                       | 5          |           | pF         |

|                    | OS Input Leakage Current                   | Measured with OS = $2.45V_{DC}$                                       | 2          | 20        | nA (max)   |

# Electrical Characteristics (Continued)

.

The following specifications apply for AGND = DGND = DGND(I/O) = 0V,  $V_A = V_D = +5.0V_{DC}$ ,  $V_{D(I/O)} = +5.0 \text{ or } +3.0V_{DC}$ , REF IN = +1.225 $V_{DC}$ ,  $f_{MCLK}$  = 20 MHz,  $R_S = 25\Omega$ . All LSB units are ADC LSBs unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25$ °C. (Note 8)

| Symbol           | Parameter                                   | Conditions     | Typical  | Limits    | Units    |

|------------------|---------------------------------------------|----------------|----------|-----------|----------|

|                  |                                             |                | (Note 9) | (Note 10) | (Limits) |

| REFERE           | NCE AND ANALOG INPUT CHARACTERI             | STICS (Note 7) |          |           |          |

| R <sub>REF</sub> | ADC Reference Ladder (REF OUT <sub>HI</sub> |                | 950      | 500       | Ω (min)  |

|                  | to REF IN) Impedance                        |                |          | 2000      | Ω (max)  |

|                  |                                             |                | 4 005    | 1.19      | V (min)  |

| REF IN           | Reference Voltage (Note 13)                 |                | 1.225    | 1.26      | V (max)  |

**DC and Logic Electrical Characteristics** The following specifications apply for AGND = DGND = DGND<sub>(UO)</sub> = 0V,  $V_A = V_D = +5.0V_{DC}$ ,  $V_{D(UO)} = +5.0$  or  $+3.0V_{DC}$ , REF IN =  $+1.225V_{DC}$ ,  $f_{MCLK} = 20$  MHz,  $R_s = 25\Omega$ . Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| SYNC, SDI, SCLK, CS , R<br>I "1" Input Voltage<br>I "0" Input Voltage<br>.eakage Current<br>Capacitance<br>CLK, SDO DIGITAL OUTP | $\begin{tabular}{ c c c c c c } \hline \hline \textbf{DIGITAL INPUT CHARACTERISTICS} \\ \hline \hline \textbf{V}_{D(UO)} = 5.25V \\ \hline \hline V_{D(UO)} = 3.6V \\ \hline \hline V_{D(UO)} = 4.75V \\ \hline \hline V_{D(UO)} = 2.7V \\ \hline \hline V_{IN} = V_D \\ \hline \hline V_{IN} = DGND \\ \hline \hline \hline \textbf{UT CHARACTERISTICS} \\ \hline \end{tabular}$ | 0.1<br>-0.1<br>5                                                                                                                                                                                              | (Note 10)<br>2.0<br>2.0<br>0.8<br>0.7                                                                                                     | (Limits)<br>V (min)<br>V (min)<br>V (max)<br>V (max)<br>uA                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I "1" Input Voltage<br>I "0" Input Voltage<br>Leakage Current<br>Capacitance                                                     | $\begin{array}{l} V_{D(I'O)} = 5.25V \\ V_{D(I'O)} = 3.6V \\ \end{array} \\ V_{D(I'O)} = 4.75V \\ V_{D(I'O)} = 2.7V \\ \end{array} \\ V_{IN} = V_{D} \\ V_{IN} = DGND \end{array}$                                                                                                                                                                                                | 0.1<br>-0.1                                                                                                                                                                                                   | 2.0<br>0.8                                                                                                                                | V (min)<br>V (max)<br>V (max)                                                                                                                                                    |

| I "0" Input Voltage<br>eakage Current<br>Capacitance                                                                             | $V_{D(VO)} = 3.6V$<br>$V_{D(VO)} = 4.75V$<br>$V_{D(VO)} = 2.7V$<br>$V_{IN} = V_D$<br>$V_{IN} = DGND$                                                                                                                                                                                                                                                                              | -0.1                                                                                                                                                                                                          | 2.0<br>0.8                                                                                                                                | V (min)<br>V (max)<br>V (max)                                                                                                                                                    |

| I "0" Input Voltage<br>eakage Current<br>Capacitance                                                                             | $V_{D(VO)} = 4.75V$<br>$V_{D(VO)} = 2.7V$<br>$V_{IN} = V_D$<br>$V_{IN} = DGND$                                                                                                                                                                                                                                                                                                    | -0.1                                                                                                                                                                                                          | 0.8                                                                                                                                       | V (max)<br>V (max)                                                                                                                                                               |

| eakage Current                                                                                                                   | $V_{D(IO)} = 2.7V$ $V_{IN} = V_{D}$ $V_{IN} = DGND$                                                                                                                                                                                                                                                                                                                               | -0.1                                                                                                                                                                                                          |                                                                                                                                           | V (max)                                                                                                                                                                          |

| eakage Current                                                                                                                   | $V_{IN} = V_D$<br>$V_{IN} = DGND$                                                                                                                                                                                                                                                                                                                                                 | -0.1                                                                                                                                                                                                          | 0.7                                                                                                                                       | · · /                                                                                                                                                                            |

| Capacitance                                                                                                                      | V <sub>IN</sub> = DGND                                                                                                                                                                                                                                                                                                                                                            | -0.1                                                                                                                                                                                                          |                                                                                                                                           | - ΠΔ                                                                                                                                                                             |

| Capacitance                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                               |                                                                                                                                           | P''                                                                                                                                                                              |

| 1                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                             |                                                                                                                                           | μA                                                                                                                                                                               |

| CLK, SDO DIGITAL OUTP                                                                                                            | PUT CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                                                                                                             |                                                                                                                                           | pF                                                                                                                                                                               |

|                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                                                                                                  |

|                                                                                                                                  | V <sub>D(I/O)</sub> = 4.75V, I <sub>OUT</sub> = -360 μA                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                               | 2.4                                                                                                                                       | V (min)                                                                                                                                                                          |

|                                                                                                                                  | $V_{D(I/O)} = 4.75V, I_{OUT} = -10 \ \mu A$                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                               | 4.4                                                                                                                                       | V (min)                                                                                                                                                                          |

| I "1" Output Voltage                                                                                                             | V <sub>D(I/O)</sub> = 2.7V, I <sub>OUT</sub> = -360 μA                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                               | 2.1                                                                                                                                       | V (min)                                                                                                                                                                          |

|                                                                                                                                  | $V_{D(I/O)} = 2.7V, I_{OUT} = -10 \ \mu A$                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                               | 2.5                                                                                                                                       | V (min)                                                                                                                                                                          |

| nical "0" Output Voltage                                                                                                         | V <sub>D(I/O)</sub> = 5.25V, I <sub>OUT</sub> = 1.6 mA                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                               | 0.4                                                                                                                                       | V (max                                                                                                                                                                           |

|                                                                                                                                  | V <sub>D(I/O)</sub> = 3.6V, I <sub>OUT</sub> = 1.6 mA                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                               | 0.4                                                                                                                                       | V (max                                                                                                                                                                           |

| TATE <sup>®</sup> Output Current                                                                                                 | V <sub>OUT</sub> = DGND                                                                                                                                                                                                                                                                                                                                                           | 0.1                                                                                                                                                                                                           |                                                                                                                                           | μA                                                                                                                                                                               |

| DD7 only)                                                                                                                        | $V_{OUT} = V_{D}$                                                                                                                                                                                                                                                                                                                                                                 | -0.1                                                                                                                                                                                                          |                                                                                                                                           | μA                                                                                                                                                                               |

| ATE Output Capacitance                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                             |                                                                                                                                           | pF                                                                                                                                                                               |

| ITAL OUTPUT CHARACTE                                                                                                             | RISTICS                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                                                                                                  |

|                                                                                                                                  | V <sub>D</sub> = 4.75V, I <sub>OUT</sub> = -360 μA                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                               | 2.4                                                                                                                                       | V (min)                                                                                                                                                                          |

| I "1" Output Voltage                                                                                                             | V <sub>D</sub> = 4.75V, I <sub>OUT</sub> = -10 μA                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               | 4.4                                                                                                                                       | V (min)                                                                                                                                                                          |

| I "0" Output Voltage                                                                                                             | V <sub>D</sub> = 5.25V, I <sub>OUT</sub> = 1.6 mA                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               | 0.4                                                                                                                                       | V (max                                                                                                                                                                           |

| CHARACTERISTICS                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                                                                                                  |

| 0 1 0 1                                                                                                                          | Operating                                                                                                                                                                                                                                                                                                                                                                         | 25                                                                                                                                                                                                            | 38                                                                                                                                        | mA (ma                                                                                                                                                                           |

| Supply Current                                                                                                                   | Standby                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                                                                                                                                            |                                                                                                                                           | μA                                                                                                                                                                               |

|                                                                                                                                  | Operating                                                                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                             | 8                                                                                                                                         | mA (ma                                                                                                                                                                           |

| Supply Current                                                                                                                   | MCLK = 0                                                                                                                                                                                                                                                                                                                                                                          | 65                                                                                                                                                                                                            |                                                                                                                                           | μA                                                                                                                                                                               |

|                                                                                                                                  | Operating, $V_{D(I/O)} = 5.0V$                                                                                                                                                                                                                                                                                                                                                    | 3.1                                                                                                                                                                                                           | 6                                                                                                                                         | mA (ma                                                                                                                                                                           |

| Digital I/O Supply Current                                                                                                       | Operating, $V_{D(I/O)} = 3.0V$                                                                                                                                                                                                                                                                                                                                                    | 1.6                                                                                                                                                                                                           | 4                                                                                                                                         | mA (ma                                                                                                                                                                           |

| I/O Supply Current                                                                                                               | MCLK = 0, $V_{D(I/O)}$ = 5.0V or 3.0V                                                                                                                                                                                                                                                                                                                                             | 1.7                                                                                                                                                                                                           |                                                                                                                                           | mA                                                                                                                                                                               |

|                                                                                                                                  | Supply Current<br>Supply Current<br>/O Supply Current                                                                                                                                                                                                                                                                                                                             | Supply Current     Standby       Supply Current     Operating<br>MCLK = 0       /O Supply Current     Operating, V <sub>D(I/O)</sub> = 5.0V       /O Supply Current     Operating, V <sub>D(I/O)</sub> = 3.0V | Supply CurrentStandby50Supply CurrentOperating<br>MCLK = 06MCLK = 065Operating, $V_{D(I/O)} = 5.0V$ 3.1Operating, $V_{D(I/O)} = 3.0V$ 1.6 | Supply CurrentStandby50Supply CurrentOperating<br>MCLK = 068MCLK = 06565/O Supply CurrentOperating, $V_{D(I/O)} = 5.0V$ 3.16/O Supply CurrentOperating, $V_{D(I/O)} = 3.0V$ 1.64 |

| Symbol                              | g specifications apply for AGND = DGND = D<br>MHz, $t_{MCLK} = 1/f_{MCLK}$ , $t_r = t_r = 5$ ns, $R_s = 250$<br><b>T_MAX</b> ; all other limits $T_A = T_J = 25^{\circ}C$ .<br><b>Parameter</b> | Conditions                                  | Typical<br>(Note 9) | Limits<br>(Note 10) | Units<br>(Limits)      |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------|---------------------|------------------------|

| f <sub>MCLK</sub>                   | Maximum MCLK Frequency<br>Minimum MCLK Frequency                                                                                                                                                |                                             |                     | 20<br>1             | MHz (min)<br>MHz (max) |

|                                     | MCLK Duty Cycle                                                                                                                                                                                 |                                             | 30<br>70            | 40<br>60            | % (min)<br>% (max)     |

| t <sub>A</sub>                      | SYNC Setup of MCLK                                                                                                                                                                              |                                             | 5                   | 10                  | ns (min)               |

| t <sub>CDSETUP</sub>                | Correction Data Valid to CLK Setup                                                                                                                                                              |                                             | 14                  | 20                  | ns (min)               |

| t <sub>CDHOLD</sub>                 | Correction Data Valid to CLK Hold                                                                                                                                                               |                                             | -12                 | 0                   | ns (min)               |

| t <sub>D1H</sub> , t <sub>D0H</sub> | RD High to DD0–DD7 TRI-STATE                                                                                                                                                                    |                                             | 5                   | 15                  | ns (max)               |

| t <sub>DACC</sub>                   | Access Time Delay from RD Low to DD0–DD7 Data Valid                                                                                                                                             |                                             | 15                  | 30                  | ns (max)               |

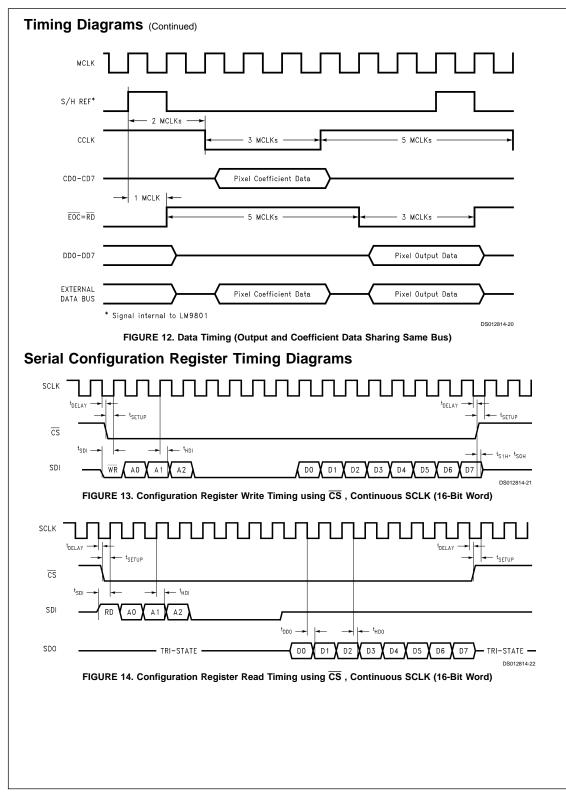

| f <sub>sclk</sub>                   | Maximum SCLK Frequency                                                                                                                                                                          |                                             |                     | 8                   | MHz (min)              |

|                                     | SCLK Duty Cycle                                                                                                                                                                                 |                                             |                     | 40                  | % (min)                |

|                                     | SEEK Duly Cycle                                                                                                                                                                                 |                                             |                     | 60                  | % (max)                |

| t <sub>sDI</sub>                    | SDI Set-Up Time from SCLK Rising Edge                                                                                                                                                           |                                             | 3                   | 10                  | ns (min)               |

| t <sub>HDI</sub>                    | SDI Hold Time from SCLK Rising Edge                                                                                                                                                             |                                             | 2                   | 15                  | ns (min)               |

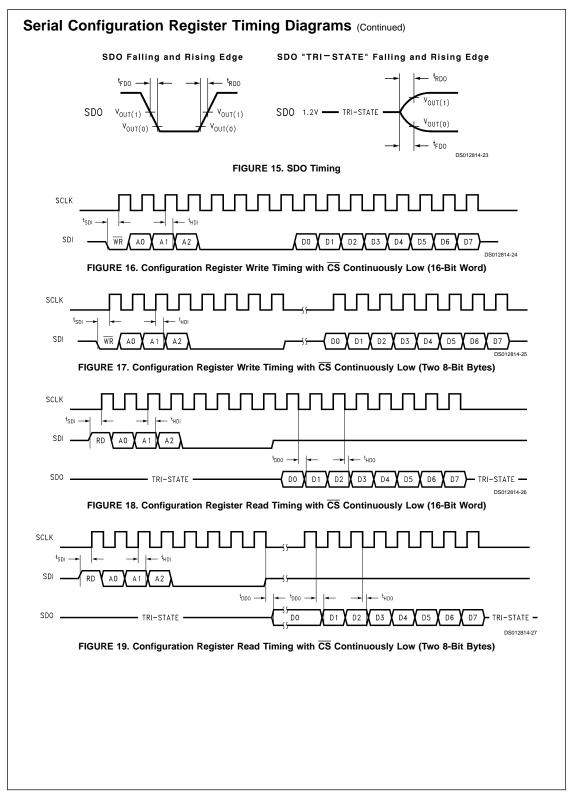

| t <sub>DDO</sub>                    | Delay from SCLK Falling Edge to SDO<br>Data Valid                                                                                                                                               |                                             | 25                  | 55                  | ns (max)               |

| t <sub>HDO</sub>                    | SDO Hold Time from SCLK Falling Edge                                                                                                                                                            | $R_{L} = 3k, C_{L} = 25 \text{ pF}$         | 30                  | 55<br>5             | ns (max)<br>ns (min)   |

| t <sub>DELAY</sub>                  | DELAY from SCLK Falling Edge to CS<br>Rising or Falling Edge                                                                                                                                    |                                             | 5                   | 10                  | ns (min)               |

| t <sub>SETUP</sub>                  | Set-Up Time of CS Rising or Falling<br>Edge to SCLK Rising Edge                                                                                                                                 |                                             | 0                   | 10                  | ns (min)               |

| t <sub>s1н</sub> , t <sub>soн</sub> | Delay from CS Rising Edge to SDO<br>TRI-STATE                                                                                                                                                   | R <sub>L</sub> = 3k, C <sub>L</sub> = 50 pF | 25                  | 50                  | ns (max)               |

| t <sub>RDO</sub>                    | SDO Rise Time, TRI-STATE to High<br>SDO Rise Time, Low to High                                                                                                                                  | R <sub>L</sub> = 3k, C <sub>L</sub> = 50 pF | 20<br>20            |                     | ns<br>ns               |

| t <sub>FDO</sub>                    | SDO Fall Time, TRI-STATE to Low<br>SDO Fall Time, High to Low                                                                                                                                   | R <sub>L</sub> = 3k, C <sub>L</sub> = 50 pF | 20<br>20            |                     | ns                     |

. .

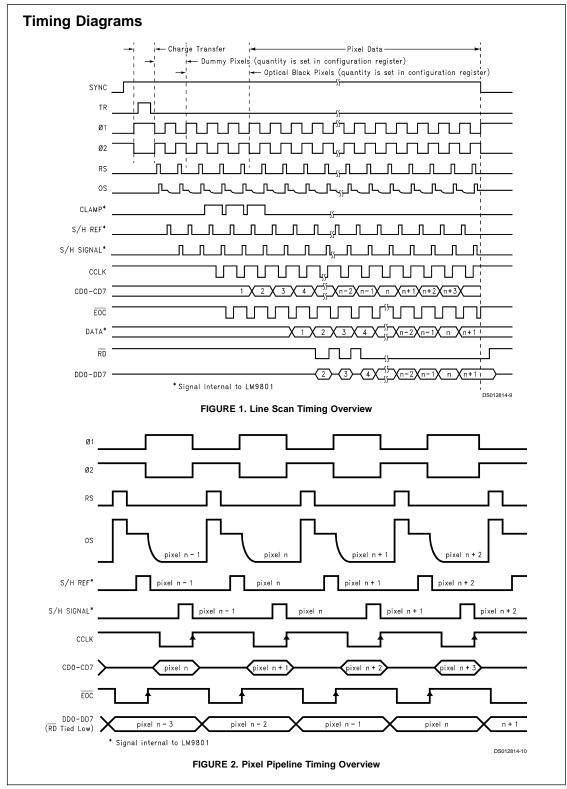

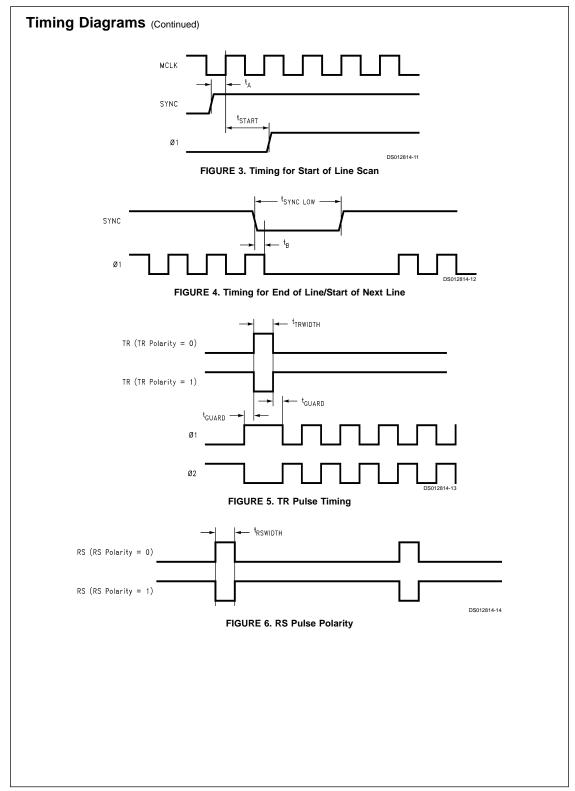

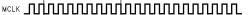

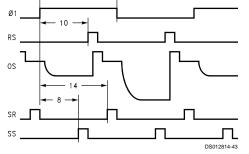

AC Electrical Characteristics, MCLK Dependent The following specifications apply for AGND = DGND = DGND<sub>(I/O)</sub> = 0V,  $V_A = V_D = V_{D(I/O)} = +5.0V_{DC}$ , REF IN = +1.225V<sub>DC</sub>,  $f_{MCLK} = 20$  MHz,  $t_{MCLK} = 1/f_{MCLK}$ ,  $t_r = t_r = 5$  ns,  $R_s = 25\Omega$ ,  $C_L$  (databus loading) = 50 pF/pin. Refer to *Table 2*, Configuration Register Parameters, for limits labelled C.R. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$

| Symbol               | Parameter                    | Conditions        | Typical  | Limits    | Units             |

|----------------------|------------------------------|-------------------|----------|-----------|-------------------|

|                      |                              |                   | (Note 9) | (Note 10) | (Limits)          |

| t <sub>start</sub>   | MCLK to first                |                   | 50 ns    | 1         | t <sub>MCLK</sub> |

| +                    |                              | Standard CCD Mode | 400 ns   | 8         | t <sub>MCLK</sub> |

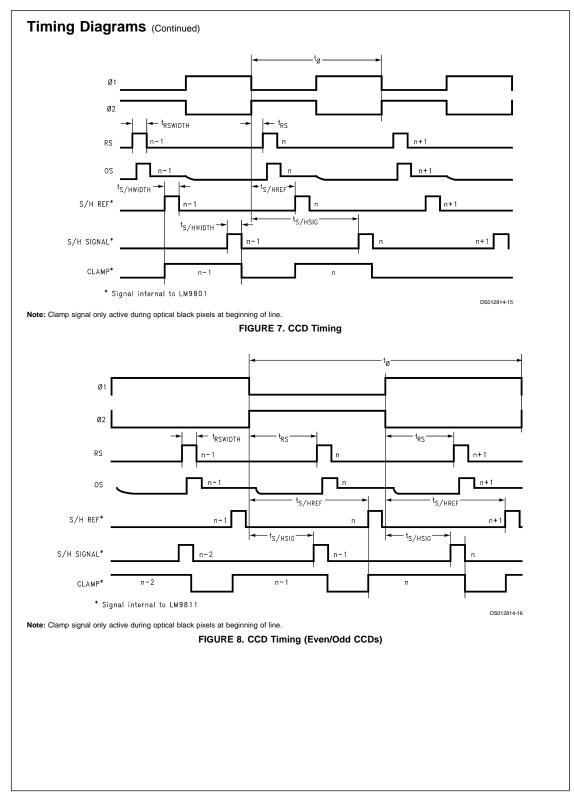

| $t_{\phi}$           |                              | Even/Odd CCD Mode | 800 ns   | 16        | t <sub>MCLK</sub> |

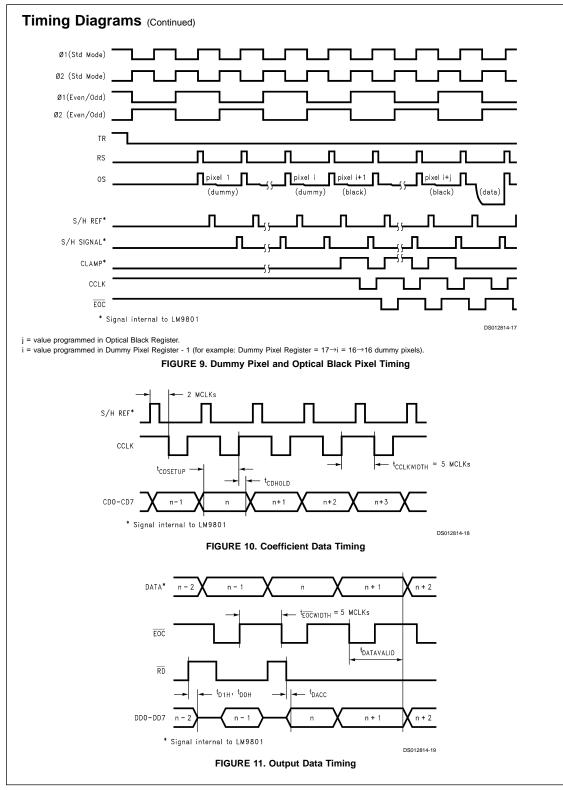

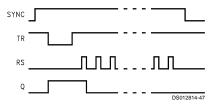

| t <sub>TRWIDTH</sub> | Transfer Pulse (TR) Width    |                   |          | C.R.      | μs                |

| t <sub>GUARD</sub>   | φ1 to TR, TR to φ1 Guardband |                   |          | C.R.      | ns                |

| t <sub>RSWIDTH</sub> | Reset Pulse (RS) Width       |                   |          | C.R.      | ns                |

|                      | Falling Edge of              | Standard CCD Mode |          | C.R.      | 20                |

| t <sub>RS</sub>      | Either Edge of               | Even/Odd CCD Mode |          | U.K.      | ns                |

|                      | Falling Edge of              | Standard CCD Mode |          | C.R.      | 20                |

| t <sub>S/HREF</sub>  | Either Edge of               | Even/Odd CCD Mode |          | U.R.      | ns                |

# AC Electrical Characteristics, MCLK Dependent (Continued)

The following specifications apply for AGND = DGND = DGND<sub>(UO)</sub> = 0V,  $V_A = V_D = V_{D(UO)} = +5.0V_{DC}$ , REF IN = +1.225V<sub>DC</sub>,  $f_{MCLK} = 20$  MHz,  $t_{MCLK} = 1/f_{MCLK}$ ,  $t_r = t_r = 5$  ns,  $R_s = 25\Omega$ ,  $C_L$  (databus loading) = 50 pF/pin. Refer to *Table 2*, **Configuration Register Parameters**, for limits labelled **C.R. Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX}; all other limits T\_A = T\_J = 25\Gamma.**

| Symbol                 | Parameter                               | Conditions        | Typical  | Limits                        | Units                   |

|------------------------|-----------------------------------------|-------------------|----------|-------------------------------|-------------------------|

|                        |                                         |                   | (Note 9) | (Note 10)                     | (Limits)                |

| •                      | Falling Edge of $\phi$ 1 to Sig. Sample | Standard CCD Mode |          | C.R.                          | 20                      |

| t <sub>S/HSIG</sub>    | Either Edge of                          | Even/Odd CCD Mode |          | U.R.                          | ns                      |

| t <sub>s/HWIDTH</sub>  | Sample Pulse Width (Acquisition Time)   |                   | 50 ns    | 1                             | t <sub>MCLK</sub>       |

| t <sub>SYNCLOW</sub>   | SYNC Low Between Lines                  |                   | 100 ns   | 2                             | t <sub>MCLK</sub> (min) |

| t <sub>B</sub>         | SYNC Setup of                           |                   |          | 2                             | t <sub>MCLK</sub> (max) |

| t <sub>CCLKWIDTH</sub> | CCLK Pulse Width                        |                   | 250 ns   | 5                             | t <sub>MCLK</sub>       |

| t <sub>DATAVALID</sub> | Data Valid Time from EOC Low            |                   |          | 300                           | ns (min)                |

| t_                     | EOC Pulse Width                         |                   | 250 ns   | 5                             | t <sub>MCLK</sub>       |

|                        | φ1 and φ2 Frequency                     | Standard CCD Mode | 2.5 MHz  | f <sub>мськ</sub> /8          | Hz                      |

|                        |                                         | Even/Odd CCD Mode | 1.25 MHz | f <sub>мськ</sub> / <b>16</b> | Hz                      |

|                        | φ1 and φ2 Duty Cycle                    |                   |          | 50                            | %                       |

## **Electrical Characteristics (Notes)**

.

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to  $GND = AGND = DGND = DGND_{(I/O)} = 0V$ , unless otherwise specified.

**Note 3:** When the input voltage ( $V_{IN}$ ) at any pin exceeds the power supplies ( $V_{IN} < GND$  or  $V_{IN} > V_A$  or  $V_D$ ), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

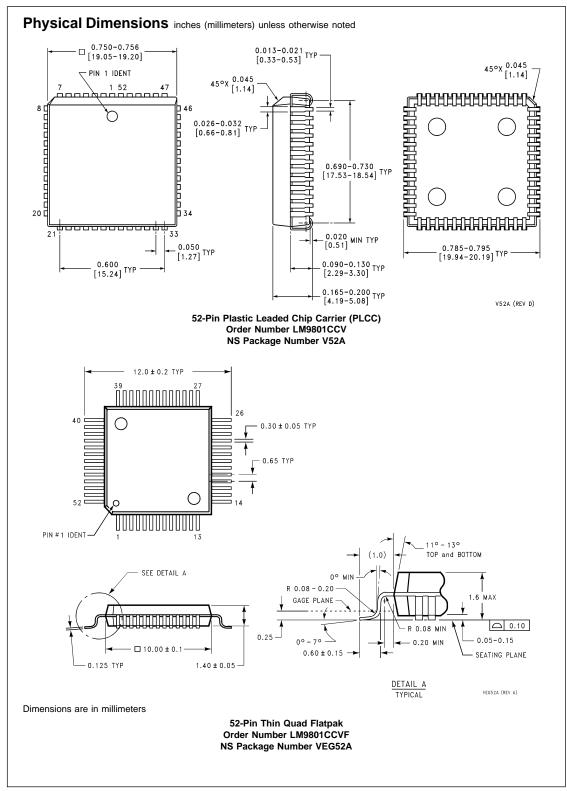

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$ ,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{Jmax} - T_A)/\theta_{JA}$ .  $T_{Jmax} = 150$ °C for this device. The typical thermal resistance ( $\theta_{JA}$ ) of this part when board mounted is 52°C/W for the V52A PLCC package, and 70°C/W for the VEG52A TQFP package.

Note 5: Human body model, 100pF capacitor discharged through a 1.5 k $\!\Omega$  resistor.

Note 6: See AN450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in any National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

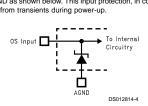

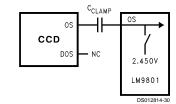

Note 7: A Zener diode clamps the OS analog input to AGND as shown below. This input protection, in combination with the external clamp capacitor and the output impedance of the CCD, prevents damage to the LM9801 from transients during power-up.

**Note 8:** To guarantee accuracy, it is required that  $V_A$  and  $V_D$  be connected together to the same power supply with separate bypass capacitors at each supply pin. **Note 9:** Typicals are at  $T_J = T_A = 25^{\circ}C$ ,  $f_{MCLK} = 20$  MHz, and represent most likely parametric norm. **Note 10:** Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

# Electrical Characteristics (Notes) (Continued)

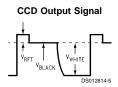

Note 11: For CCDs,  $V_{BLACK}$  is defined as the CCD OS voltage for the reference period following the reset feedthrough pulse.  $V_{WHITE}$  is defined as the peak CCD pixel output voltage for a white (full scale) image with respect to the reference level,  $V_{BLACK} - V_{RFT}$  is defined as the peak positive deviation above  $V_{BLACK}$  of the reset feedthrough pulse. For CIS,  $V_{WHITE}$  is defined as the peak CCD pixel output voltage for a white (full scale) image with respect to GND (0V). The maximum correctable range of pixel-to-pixel  $V_{WHITE}$  variation is defined as the maximum variation in  $V_{WHITE}$  (due to PRNU, light source intensity variation, optics, etc.) that the LM9801 can correct for using its internal PGA.

Note 12: Integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function of the ADC.

Note 13: Reference voltages below 1.19V may decrease SNR. Reference voltages above 1.26V may cause clipping errors inside the LM9801. The LM4041EIM3-1.2 (SOT-23 package) or the LM4041EIZ-1.2 (TO-92 package) bandgap voltage references are recommended for this application.

Gain<sub>PGA</sub>

$$\left(\frac{V}{V}\right) = 1 + C \frac{PGA \text{ code}}{256}$$

where C = (PGA RANGE -1) $\frac{256}{255}$

and PGA RANGE = the PGA adjustment range (in V/V) of the LM9801 under test.

Note 15: VGA Gain Error is the maximum difference between the measured gain for any VGA code and the ideal gain calculated by using the formula

$$Gain_{VGA}(dB) = C \frac{VGA \text{ code}}{16} \text{ where } C = (VGA \text{ RANGE}) \frac{16}{15}$$

and VGA RANGE = the VGA adjustment range (in dB) of the LM9801 under test.

# **Typical Performance Characteristics**

| CCD Driver Signals        |                                                                                   |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| ¢1                        | Digital Output. CCD clock signal, phas                                            |  |  |  |  |

| ψ <b>ι</b>                |                                                                                   |  |  |  |  |

| φ2                        | Digital Output. CCD clock signal, phas                                            |  |  |  |  |

| r                         | 2.                                                                                |  |  |  |  |

| RS                        | Digital Output. Reset pulse for the CC                                            |  |  |  |  |

| TR                        | Digital Output. Transfer pulse for the                                            |  |  |  |  |

|                           | CCD.                                                                              |  |  |  |  |

|                           | Analog I/O                                                                        |  |  |  |  |

| OS                        | Analog Input. This is the OS (Output                                              |  |  |  |  |

|                           | Signal) from the CCD. The maximum                                                 |  |  |  |  |

|                           | peak signal that can be accurately                                                |  |  |  |  |

|                           | digitized is equal to the voltage at REI                                          |  |  |  |  |

|                           | IN, typically 1.225V.                                                             |  |  |  |  |

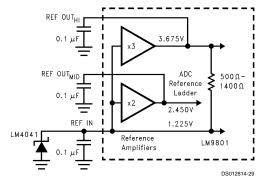

| REF IN                    | Analog Inputs. These two pins are the                                             |  |  |  |  |

|                           | system reference voltage inputs and should be tied together to a 1.225V           |  |  |  |  |

|                           | voltage source and bypassed to AGNI                                               |  |  |  |  |

|                           | with a 0.1 $\mu$ F monolithic capacitor.                                          |  |  |  |  |

| REF OUT <sub>HI</sub>     | Analog Output. This reference voltage                                             |  |  |  |  |

|                           | developed internally by the LM9801,                                               |  |  |  |  |

|                           | and is equal to 3 times REF IN. It                                                |  |  |  |  |

|                           | should be bypassed to AGND with a                                                 |  |  |  |  |

|                           | 0.1 µF monolithic capacitor.                                                      |  |  |  |  |

| REF OUT <sub>MID</sub>    | Analog Output. This reference voltage                                             |  |  |  |  |

|                           | developed internally by the LM9801,                                               |  |  |  |  |

|                           | and is equal to 2 times REF IN. It                                                |  |  |  |  |

|                           | should be bypassed to AGND using a                                                |  |  |  |  |

| <u> </u>                  | 0.1 µF monolithic capacitor.                                                      |  |  |  |  |

| V <sub>TEST1</sub> ,<br>V | Analog Inputs/Outputs. These pins are<br>used for testing the device during       |  |  |  |  |

| V <sub>TEST2</sub>        | manufacture and should be left                                                    |  |  |  |  |

|                           | unconnected.                                                                      |  |  |  |  |

|                           | Configuration Register I/O                                                        |  |  |  |  |

| SDI                       | Digital Input. Serial Data Input pin.                                             |  |  |  |  |

| SDO                       | Digital Output. Serial Data Output pin.                                           |  |  |  |  |

| SCLK                      | Digital Input. This is the serial data                                            |  |  |  |  |

|                           | clock, used to clock data in through SI                                           |  |  |  |  |

|                           | and out through SDO. SCLK is                                                      |  |  |  |  |

|                           | asynchronous to MCLK. Input data is                                               |  |  |  |  |

|                           | latched and output data is changed or                                             |  |  |  |  |

|                           | the rising edge of SCLK.                                                          |  |  |  |  |

| CS                        | Digital Input. This is the Chip Select                                            |  |  |  |  |

|                           | signal for writing to the Configuration<br>Register through the serial interface. |  |  |  |  |

|                           | This input must be low in order to                                                |  |  |  |  |

|                           | communicate with the Configuration                                                |  |  |  |  |

|                           | Register. This pin is used for serial I/C                                         |  |  |  |  |

|                           | only-it has no effect on any other                                                |  |  |  |  |

|                           | section of the chip.                                                              |  |  |  |  |

|                           | Digital Coefficient I/O                                                           |  |  |  |  |

| CD0 (LSB)-                | Digital Inputs. Correction Coefficient                                            |  |  |  |  |

| CD7 (MSB)                 | Databus. This is the 8-bit data path fo                                           |  |  |  |  |

|                           | the gain adjust PGA, used during line                                             |  |  |  |  |

|                           | scan.                                                                             |  |  |  |  |

| CCLK                  | Digital Output. This is the signal that is<br>used to clock the Gain coefficients into<br>the LM9801. Data is latched on the<br>rising edge of CCLK.                                                                      |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Digital Output I/O                                                                                                                                                                                                        |

| DD0 (LSB)-            | Digital Outputs. Pixel Output Databus.                                                                                                                                                                                    |

| DD7 (MSB)             | This data bus outputs the 8-bit digital output data during line scan.                                                                                                                                                     |

| EOC                   | Digital Output. This is the End of<br>Conversion signal from the ADC                                                                                                                                                      |

|                       | indicating that new pixel data is available.                                                                                                                                                                              |

| RD                    | Digital Input. Taking this input low<br>places the data stored in the output<br>latch on the bus. When this input is high<br>the DD0–DD7 bus is in TRI-STATE.                                                             |

|                       | General Digital I/O                                                                                                                                                                                                       |

| MCLK                  | Digital Input. This is the 20 MHz (typical) master system clock.                                                                                                                                                          |

| SYNC                  | Digital Input. A low-to-high transition on<br>this input begins a line scan operation.<br>The line scan operation terminates<br>when this input is taken low.                                                             |

|                       | Analog Power                                                                                                                                                                                                              |

| V <sub>A</sub>        | This is the positive supply pin for the analog supply. It should be connected to a voltage source of $+5V$ and bypassed to AGND with a 0.1 $\mu$ F monolithic capacitor in parallel with a 10 $\mu$ F tantalum capacitor. |

| AGND                  | This is the ground return for the analog supply.                                                                                                                                                                          |

|                       | Digital Power                                                                                                                                                                                                             |

| V <sub>D</sub>        | This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1 µF monolithic capacitor.                                                        |

| DGND                  | This is the ground return for the digital supply.                                                                                                                                                                         |

| V <sub>D(I/O)</sub>   | This is the positive supply pin for the digital supply for the LM9801's I/O. It should be connected to a voltage source of +3V to +5V and bypassed to $DGND_{(I/O)}$ with a 0.1 $\mu$ F monolithic                        |

|                       | capacitor. If the supply for this pin is different than the supply for $V_A$ and $V_D$ , it should also be bypassed with a 10 $\mu$ F tantalum capacitor.                                                                 |

| DGND <sub>(I/O)</sub> | This is the ground return for the digital supply for the LM9801's I/O.                                                                                                                                                    |

|                       | NC                                                                                                                                                                                                                        |

| NC                    | All pins marked NC (no connect) should<br>be left floating. Do not tie NC pins to<br>ground., power supplies, or any other<br>potential or signal.                                                                        |

· ·

9

12

|      |    |            | TABLE 1       | . Configuration  | Register Addr     | ess Table    |            |                |          |

|------|----|------------|---------------|------------------|-------------------|--------------|------------|----------------|----------|

| 2 A1 | A0 | D7         | D6            | D5               | D4                | D3           | D2         | D1             | D0       |

|      |    | Standard   | _             | _                |                   |              |            |                |          |

|      |    | Mode or    |               | S<br>Ise         | RS                |              |            | an Desition    |          |

| 0 0  | 0  | Even/Odd   |               | dth              | Pulse<br>Polarity |              | KS Pul     | se Position    |          |

|      |    | Mode       |               | aur              | 1 olanty          |              |            |                |          |

|      |    | MODE       | RSW1          | RSW0             | RSPOL             | RSPOS3       | RSPOS2     | RSPOS1         | RSPOS    |

| -    |    |            | Sample Refer  | ence Position    |                   |              |            |                |          |

| 0 0  | 1  |            | (Maximum Regi | ster Value is 14 | )                 |              | Sample S   | ignal Position |          |

|      |    | SR3        | SR2           | SR1              | SR0               | SS3          | SS2        | SS1            | SS0      |

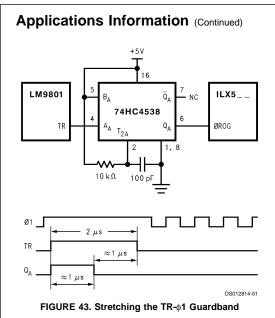

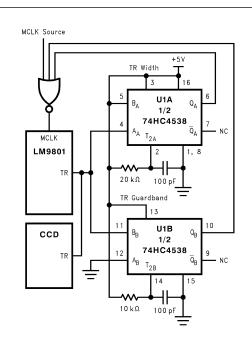

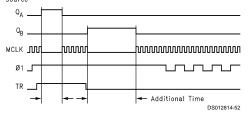

|      |    | φ1         | φ2            | RS               | TR                |              |            | TR–ø1          | TR       |

| 0 1  | 0  | Enable     | Enable        | Enable           | Enable            | TR Pulse     | Width      | Guardband      | Polarit  |

|      | Ū  | φ1EN       | φ2EN          | RSEN             | TREN              | TRW1         | TRW0       | TRGRD          | TRPO     |

|      |    | Signal     | Ψ==ιν         |                  |                   |              |            |                |          |

| D 1  | 1  | Polarity   |               | Dum              | my Pixels (Minir  | mum Register | Value is 2 | 2)             |          |

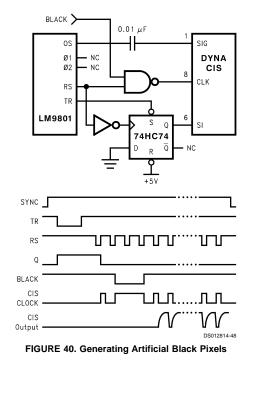

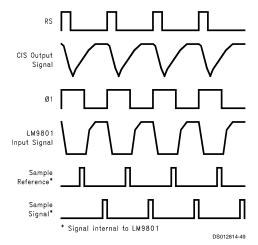

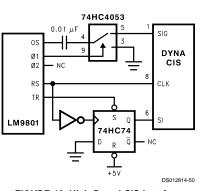

| , i  |    | SIGPOL     | BLS6          | BLS5             | BLS4              | BLS3         | BLS2       | DI C1          | BLS0     |

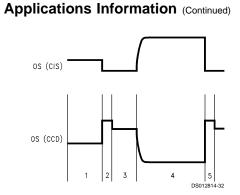

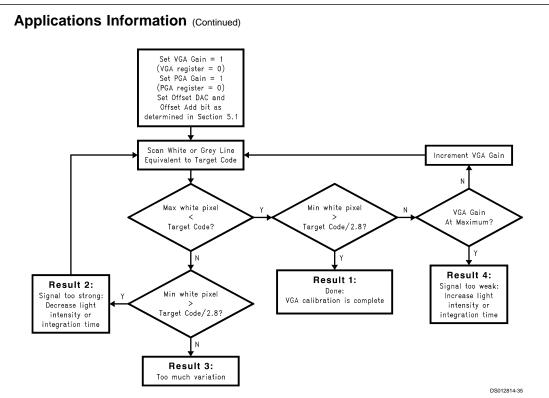

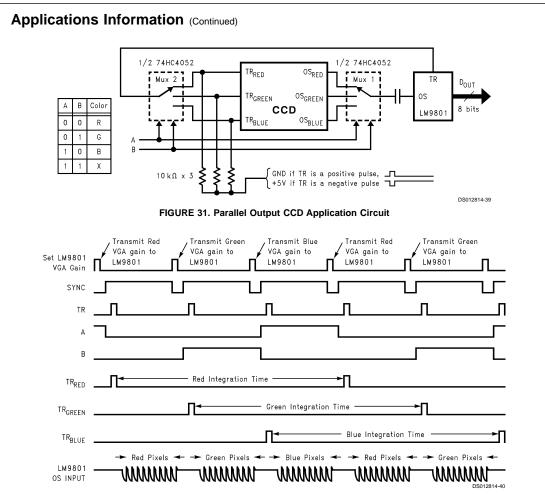

| 1 0  | 0  | SIGFUL     | BLSO          |                  |                   |              |            | BLS1           | BLOU     |