# QUADRUPLE BISTABLE LATCH | \$5477

N7477

S5477W • N7477W

DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

The S5477Q/N7477Q is a monolithic, quadruple, bistable latch with Q outputs. Information present at a data (D) input is transferred to the Q output when the clock is high, and the Q output will follow the data input as long as the clock remains high. When the clock goes low, the information (that was present at the data input at the time the transition occurred) is retained at the Q output until the clock is permitted to go high.

This latch is ideally suited for use as temporary storage for binary information between processing units and input/output or indicator units.

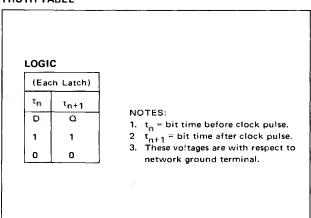

#### **TRUTH TABLE**

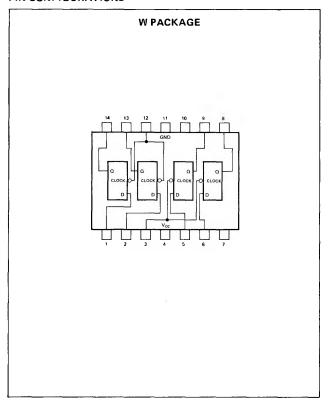

#### **PIN CONFIGURATIONS**

#### RECOMMENDED OPERATING CONDITIONS

|                                                             | MIN  | NOM | MAX  | UNIT |

|-------------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> (See Note 3): S5477 Circuits | 4.5  | 5   | 5.5  | V    |

| N7477 Circuits                                              | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out from each Output, N                      |      | 1   | 10   |      |

| Operating Free-Air Temperature Range, TA: S5477 Circuits    | -55  | 25  | 125  | °C   |

| N7477 Circuits                                              | 0    | 25  | 70   | °c   |

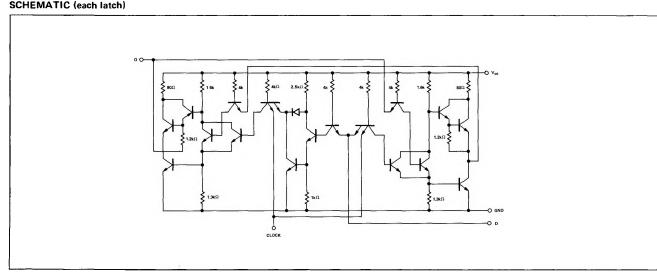

## SCHEMATIC (each latch)

## SIGNETICS DIGITAL 54/74 TTL SERIES - S5477 ● N7477

ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER          |                                                                              | TE                                                 | TEST CONDITIONS*                                 |                | MIN        | TYP**    | MAX        | UNIT     |

|--------------------|------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|----------------|------------|----------|------------|----------|

| V <sub>in(1)</sub> | Input voltage required<br>to ensure logical 1 level<br>at any input terminal | V <sub>CC</sub> = MIN                              |                                                  |                | 2          |          |            | ٧        |

| V <sub>in(0)</sub> | Input voltage required to ensure logical O level at any input terminal       | V <sub>CC</sub> = MIN                              |                                                  |                |            |          | 8.0        | V        |

| $V_{out(1)}$       | Logical 1 output voltage                                                     | V <sub>CC</sub> = MIN,                             | $I_{load} = -400\mu A$                           |                | 2.4        |          |            | V        |

| $V_{out(0)}$       | Logical 0 output voltage                                                     | V <sub>CC</sub> = MIN,                             | $I_{sink} = 16mA$                                |                |            |          | 0.4        | V        |

| lin(0)             | Logical 0 level input<br>current at D                                        | V <sub>CC</sub> = MAX,                             | $V_{in} = 0.4V$                                  |                |            |          | -3.2       | m/       |

| <sup>1</sup> in(0) | Logical 0 level input<br>current at clock                                    | V <sub>CC</sub> = MAX,                             |                                                  |                |            |          | -6.4       | m/       |

| lin(1)             | Logical 1 level input current at D                                           | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX,   | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | 80<br>1    | μA<br>mA |

| lin(1)             | Logical 1 level input<br>current at clock                                    | V <sub>CC</sub> = MAX,<br>V <sub>in</sub> = 2.4V,  |                                                  |                |            |          | 160        | μΑ       |

|                    |                                                                              | V <sub>CC</sub> = MAX,                             | v <sub>in</sub> = 5.5V                           |                |            |          | 1          | m/       |

| los                | Short circuit output current†                                                | $V_{\text{CC}} = \text{MAX},$ $V_{\text{out}} = 0$ |                                                  | S5477<br>N7477 | -20<br>-18 |          | -75<br>-75 | m/<br>m/ |

| lcc                | Supply current                                                               | V <sub>CC</sub> = MAX,                             |                                                  | S5477<br>N7477 |            | 32<br>32 | 46<br>53   | m/<br>m/ |

# SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

|                       | PARAMETER                                                                    | 1                      | EST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----------------------|------------------------------------------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| t <sub>setup1</sub>   | Minimum logical 1 level input setup time at D input                          | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 7   | 20  | ns   |

| <sup>t</sup> setup0   | Minimum logical 0 level<br>input setup time at D<br>input                    | C <sub>L</sub> = 15pF, | $R_L = 400\Omega$     |     | 14  | 20  | ns   |

| <sup>t</sup> hold1    | Maximum logical 1<br>level input hold time<br>required at D input            | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 0   | 15¶ |     | ns   |

| <sup>t</sup> hold0    | Maximum logical 0<br>level input hold time<br>required at D input            | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 0   | 6¶  |     | ns   |

| <sup>t</sup> pd1(D-Q) | Propagation delay time<br>to logical 1 level from<br>D input to Q output     | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 16  | 30  | ns   |

| (D-Q)                 | Propagation delay time<br>to logical O level from<br>D input to Q output     | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 14  | 25  | ns   |

| <sup>t</sup> pd1(C-Q) | Propagation delay time<br>to logical 1 level from<br>clock input to Q output | C <sub>L</sub> = 15pF, | $R_L = 400\Omega$     |     | 16  | 30  | ns   |

| <sup>t</sup> pd0(C-Q) | Propagation delay time<br>to logical O level from<br>clock input to Q output | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω |     | 7   | 15  | ns   |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

<sup>\*\*</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

† Not more than one output should be shorted at a time.

<sup>¶</sup> These typical times indicate that period occurring prior to the fall of clock pulse (t<sub>0</sub>) below 1.5V when data at the D input will still be recognized and stored.