# 4-BIT RIGHT-SHIFT | S5495 **LEFT-SHIFT REGISTER**

S5495-A,F • N7495-A,F

# DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

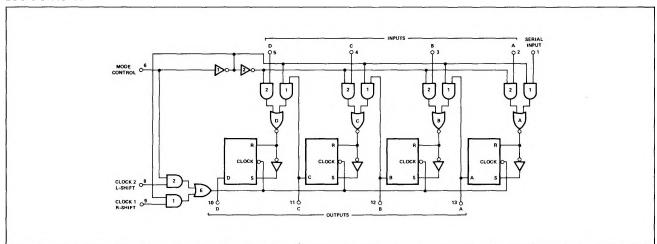

The 54/7495 is a monolithic universal 4-Bit Shift Register designed with standard TTL techniques. The circuit layout consists of 4 R-S master-slave flip-flops, 4 AND-OR-INVERT gates, and 6 inverters configured to form a versatile register which will perform right-shift, left-shift, or parallel-in, parallel-out operations depending on the logical input level to the mode control.

Right-shift operations are performed when a logical 0 level is applied to the mode control. Serial data is entered at the serial input D<sub>S</sub> and shifted one position right on each clock 1 pulse. In this mode, clock 2 and parallel inputs  $\mathsf{D}_A$  thru  $\mathsf{D}_D$  are inhibited.

Parallel-in, parallel-out operations are performed when a logical 1 level is applied to the mode control. Parallel data is entered at parallel inputs  $D_A$  thru  $D_D$  and is transferred to the data outputs Ao thru Do on each clock 2 pulse. In this mode, shift-left operations may be implemented by externally tying the output of each flipflop to the parallel input of the previous flip-flop (D $_0$  to D $_C$  and etc.), with serial data entry at input D<sub>D</sub>.

Information must be present at the R-S inputs prior to clocking and transfer of data occurs on the falling edge of the clock pulse.

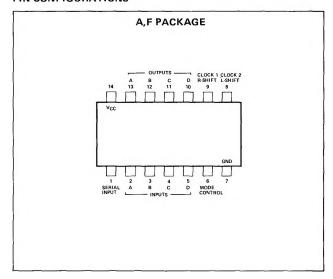

#### **PIN CONFIGURATIONS**

#### **LOGIC DIAGRAM**

## RECOMMENDED OPERATING CONDITIONS

|                                              |                  | MIN  | NOM | MAX  | UNIT |

|----------------------------------------------|------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> (See Note 1): | S5495 Circuits   | 4.5  | 5   | 5.5  | V    |

| 3 CC                                         | N7495 Circuits   | 4.75 | 5   | 5.25 | l v  |

| Normalized Fan-Out From Each Output          |                  | 1    |     | 10   |      |

| Width of Clock Pulse tp(clock)               | S5495 Circuits   | 20   | 10  | l .  | ns   |

|                                              | N7495 Circuits   | 15   | 10  | Ĭ    | ns   |

| Setup Time Required at Serial, A, B, C, o    | 10               | 10   | l   | ns   |      |

| Hold Time Required at Serial, A, B, C, o     | r D Inputs thold | 0    | 10  | 1    | ns   |

| Logical O Level Setup Time Required at       |                  |      |     | l .  |      |

| (With Respect to Clock 1 inputs)             |                  | 15   |     | 1    | ns   |

| Logical 1 level Setup Time Required at M     | Node Control     |      |     | l    |      |

| (With Respect to Clock 2 input)              |                  | 15   |     | 1    | ns   |

| Logical 0 Level Setup Time Required at       | Mode Control     |      |     | i .  |      |

| (With Respect to Clock 2 input)              |                  | 5    |     | ł    | ns   |

| Logical 1 Level Setup Time Required at       | Mode Control     |      |     |      |      |

| (With Respect to Clock 1 input)              |                  | 5    |     |      | ns   |

### NOTES:

- 1. Voltage values are with respect to network ground terminal.

- 2. Input voltages must be zero or positive with respect to network ground terminal.

# SIGNETICS DIGITAL 54/74 TTL SERIES - \$5495 ● N7495

## ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER           |                                                                  | TEST CONDITIONS*                                                                               | MIN | TYP** | MAX     | UNIT     |

|---------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-------|---------|----------|

| V <sub>in(1)</sub>  | Input voltage required to ensure logical 1 at any input terminal | V <sub>CC</sub> = MIN                                                                          | 2   |       | -       | V        |

| V <sub>in (0)</sub> | Input voltage required to ensure logical 0 at any input terminal | V <sub>CC</sub> = MIN                                                                          |     |       | 8.0     | V        |

| V <sub>out(1)</sub> | Logical 1 output voltage                                         | $V_{CC} = MIN$ , $I_{load} = -400\mu A$                                                        | 2.4 |       |         | v        |

| V <sub>out(0)</sub> | Logical 0 output voltage  Logical 0 level input current          | V <sub>CC</sub> = MIN, I <sub>sink</sub> = 16mA                                                | *   |       | 0.4     | \ \ \ \  |

| <sup>1</sup> in(0)  | at any input except mode control                                 | $V_{CC} = MAX, V_{in} = 0.4V$                                                                  |     |       | -1.6    | mA       |

| lin(0)              | Logical 0 level input current at mode control                    | V <sub>CC</sub> = MAX, V <sub>in</sub> = 0.4V                                                  |     |       | -3.2    | mA       |

| <sup>(</sup> in(1)  | Logical 1 level input current at any input except mode control   | V <sub>CC</sub> = MAX, V <sub>in</sub> = 2.4V<br>V <sub>CC</sub> = MAX, V <sub>in</sub> = 5.5V |     |       | 40<br>1 | μA<br>mA |

| I <sub>in(1)</sub>  | Logical 1 level input current                                    | V <sub>CC</sub> = MAX, V <sub>in</sub> = 2.4V                                                  |     |       | 80      | μΑ       |

|                     | at mode control                                                  | V <sub>CC</sub> = MAX, V <sub>in</sub> = 5.5V                                                  |     |       | 1       | mA       |

| os                  | Short-circuit output current†                                    | V <sub>CC</sub> = MAX                                                                          | -18 |       | -57     | mA       |

| <sup>I</sup> cc     | Supply current                                                   | V <sub>CC</sub> = MAX N7495                                                                    | 39  | 50    | 63      | mA       |

# SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

| PARAMETER        |                                                        | TE                     | TEST CONDITIONS        |    | TYP | MAX | UNIT |

|------------------|--------------------------------------------------------|------------------------|------------------------|----|-----|-----|------|

| f <sub>max</sub> | Maximum shift frequency                                | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω  | 25 | 36  |     | MHz  |

| t <sub>pd1</sub> | Propagation delay time to logical 1 level from clock 1 | C <sub>L</sub> = 15pF, | $R_1 = 400\Omega$      |    | 18  | 27  | ns   |

| Par              | or clock 2 to outputs                                  |                        | L                      |    |     |     |      |

|                  | Propagation delay time to                              |                        |                        |    |     |     |      |

| <sup>t</sup> pd0 | logical 0 level from clock 1 or clock 2 to outputs     | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400 Ω |    | 21  | 32  | ns   |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable circuit type.

<sup>\*\*</sup>All typical values are at  $V_{CC}$  = 5V,  $T_A$  = 25°C.

†Not more than one output should be shorted at a time.