# J-K MASTER-SLAVE FLIP-FLOP | S54H72

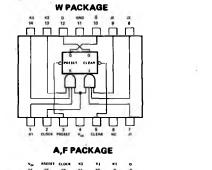

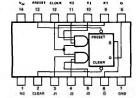

PIN CONFIGURATIONS

# N74H72

\$54H72\_A,F,W . N74H72\_A,F

## DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

These J-K flip-flops are based on the master-slave principle. The AND gate inputs for entry into the master section are controlled by the clock pulse. The clock pulse also regulates the circuitry which connects the master and slave sections. The sequence of operation is as follows:

- 1. Isolate slave from master

- 2. Enter information from AND gate inputs to master

- 3. Disable AND gate inputs

- 4. Transfer information from master to slave.

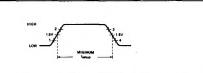

Logical state of J and K inputs must not be allowed to change when the clock pulse is in a high state

#### TRUTH TABLE

| '(Eac | ch Flip | -Flop) |                                                                                                                             |

|-------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| tn    |         | tn+1   |                                                                                                                             |

| J     | к       | ٩      |                                                                                                                             |

| 0     | 0       | an     | NOTES:                                                                                                                      |

| 0     | 1       | 0      | 1. J = J1 · J2 · J3                                                                                                         |

| 1     | 0       | 1      | 2. K = K1 · K2 · K3                                                                                                         |

| 1     | 1       | مما    | <ul> <li>3. t<sub>n</sub> = bit time before clock pulse</li> <li>4. t<sub>n+1</sub> = bit time after clock pulse</li> </ul> |

#### CLOCK WAVEFORM

#### POSITIVE LOGIC

Low Input to preset sets Q to logical 1 Low input to clear sets Q to logical 0 Preset and clear are independent of clock

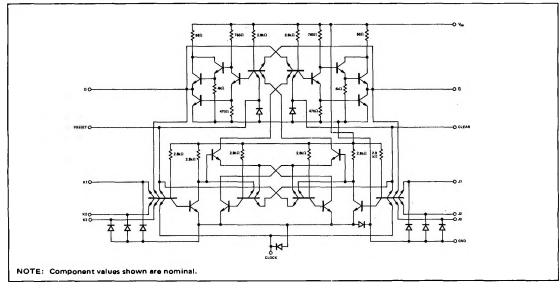

#### SCHEMATIC DIAGRAM

#### RECOMMENDED OPERATING CONDITIONS

|                                                                                        | MIN                         | NOM | MAX  | UNIT |

|----------------------------------------------------------------------------------------|-----------------------------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S54H72 Circuits                                       | 4.5                         | 5   | 5.5  | v -  |

| N74H72 Circuits                                                                        | 4.75                        | 5   | 5.25 | v    |

| Operating Free-Air Temperature Range, $T_{\Delta}$ : S54H72 Circuits                   | -55                         | 25  | 125  | °c   |

| N74H72 Circuits                                                                        | 0                           | 25  | 70   | °C   |

| Normalized Fan-Out from each Output, N                                                 |                             |     | 10   |      |

| Width of Clock Pulse, t <sub>p(clock)</sub>                                            | 12                          |     |      | ns   |

| Width of Preset Pulse, to (preset)                                                     | 16                          |     |      | ns   |

| Width of Clear Pulse, tp(clear)                                                        | 16                          |     |      | ns   |

| Input Setup Time, t <sub>setup</sub> (See above)<br>Input Hold Time, t <sub>hold</sub> | <sup>≥t</sup> p(clock)<br>0 |     |      |      |

#### ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER           |                                                                          | TEST CONDITIONS*                                 |                                                  | MIN TYP | TYP <sup>†</sup> MAX | UNIT     |

|---------------------|--------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------|----------------------|----------|

| V <sub>in(1)</sub>  | Input voltage required<br>to ensure logical 1 at<br>any input terminal   | V <sub>CC</sub> = MIN                            |                                                  | 2       |                      | v        |

| V <sub>in(0)</sub>  | Input voltage required<br>to ensure logical O at<br>any input terminal   | V <sub>CC</sub> = MIN,                           |                                                  |         | 8.0                  | v        |

| V <sub>out(1)</sub> | Logical 1 output<br>voltage                                              | V <sub>CC</sub> = MIN,                           | l <sub>load</sub> = ~500µA                       | 2.4     |                      | v        |

| V <sub>out(0)</sub> | Logical O output<br>voltage                                              | V <sub>CC</sub> = MIN                            | l <sub>sink</sub> ∍ 20mA                         |         | 0.4                  | v        |

| lin(0)              | Logical 0 level input<br>current at J1, J2, J3,<br>K 1, K2, K3, or clock | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |         | -2                   | mA       |

| lin(0)              | Logical O level input<br>current at preset or<br>clear                   | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4∨                           |         | -4                   | mA       |

| lin(1)              | Logical 1 level input<br>current at J1, J2, J3,<br>K1, K2, or K3         | $V_{CC} = MAX,$<br>$V_{CC} = MAX,$               | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |         | 50<br>1              | μA<br>mA |

| <sup>1</sup> in(1)  | Logical 1 level input<br>current at clock                                | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |         | 50<br>1              | μA<br>mA |

| lin(1)              | Logical 1 level input<br>current at preset or<br>clear                   | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |         | 100<br>1             | μA<br>mA |

| los                 | Short circuit output<br>current**                                        | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0                              | -40     | -100                 | mA       |

| 'cc                 | Supply current                                                           | V <sub>CC</sub> = MAX,                           |                                                  | 16      | 25                   | mA       |

### SWITCHING CHARACTERISTICS, $V_{CC} = 5V$ , $T_A = 25^{\circ}$ C, N = 10

| PARAMETER         |                                                                                | TEST CONDITIONS        |                       | MIN | TYP | MAX | UNIT |

|-------------------|--------------------------------------------------------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| fclock            | Maximum clock<br>frequency                                                     | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω | 25  | 30  |     | MHz  |

| <sup>t</sup> pd 1 | Propagation delay time<br>to logical 1 level from<br>clear or preset to output | С <sub>L</sub> = 25рF, | RL = 280Ω             |     | 6   | 13  | ns   |

| <sup>t</sup> pd0  | Propagation delay time<br>to logical 0 level from<br>clear or preset to output | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω |     | 12  | 24  | ns   |

| <sup>t</sup> pd 1 | Propagation delay time<br>to logical 1 level from<br>clock to output           | C <sub>L</sub> = 25pF, | R <sub>L</sub> = 280Ω |     | 16  | 21  | ns   |

| <sup>t</sup> pd0  | Propagation delay time<br>to logical 0 level from<br>clock to output           | CL = 25pF,             | RL = 280Ω             |     | 22  | 27  | ns   |

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

\*\* Not more than one output should be shorted at a time, and duration of short circuit test should not exceed 1 second.

† All typical values are at  $V_{CC}$  = 5V,  $T_A$  = 25°C.