# 2.5V / 3.3V Low Noise Multi-Rate Clock Generator

#### Description

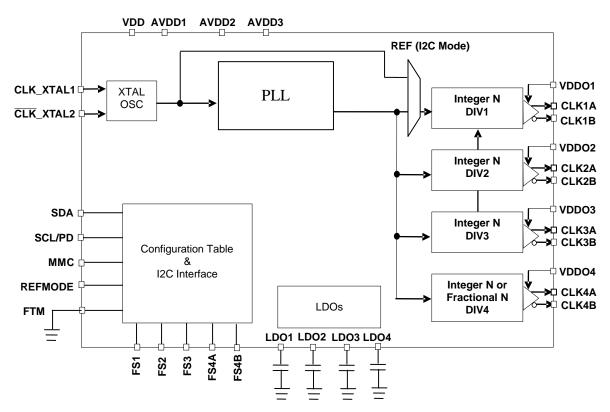

The NB3H5150–01 is a high performance Multi–Rate Clock generator which simultaneously synthesizes up to four different frequencies from a single PLL using a 25 MHz input reference. The reference frequency can be provided by a crystal, LVCMOS/LVTTL, LVPECL, HCSL or LVDS differential signals. The REFMODE pin will select the reference source.

Three output banks (CLK1A/CLK1B to CLK3A/CLK3B) produce user selectable frequencies of: 33.33 MHz, 50 MHz, 100 MHz, 125 MHz, or 156.25 MHz and have ultra—low noise/jitter performance of less than 0.3 ps.

The fourth output bank (CLK4A/CLK4B) can produce the following integer and FRAC-N frequencies in pin-strap mode: 25 MHz, 33.33 MHz, 66.66 MHz, 100 MHz, 125 MHz, 133.33 MHz, 156.25 MHz or 161.1328 MHz.

Each output block can create two single-ended in-phase LVCMOS outputs or one differential pair of LVPECL outputs.

Each of the four output blocks is independently powered by a separate VDDO, 2.5 V/3.3 V for LVPECL, 1.8 V/2.5 V/3.3 V for LVCMOS.

The serial (I<sup>2</sup>C and SMBUS) interface can be used to load register files into the NB3H5150–01 to program a variety of functions including the frequencies and output levels of each output which can be individually enabled and disabled.

#### **Features**

- Flexible Input Reference 25 MHz Crystal, Oscillator, Single–Ended or Differential Clock

- Four Independent User–Programmable Clock Frequencies from 25 MHz to 250 MHz

- Independently Configurable Outputs:

Up to Eight LVCMOS Single Ended outputs or,

Up to Four Differential LVPECL Outputs or any combination of LVCMOS and LVPECL

- Flexible Input/Core and Output Power Supply Combinations:

VDD (Core) = 3.3 V  $\pm 5\%$  or 2.5 V  $\pm 5\%$ VDDO<sub>n</sub> (Outputs) = 3.3 V  $\pm 5\%$  or 2.5 V  $\pm 5\%$  or 1.8 V  $\pm 5\%$  (LVCMOS Only)

- Independent Power Supply for each Output Bank

- 300 ps max Output Rise and Fall Times, LVPECL

- 1000 ps max Output Rise and Fall Times, LVCMOS

- 300 fs maximum RMS Phase Jitter Interger–N (CLK1:4) 156.25 MHz

#### ON Semiconductor®

www.onsemi.com

#### MARKING DIAGRAM\*

QFN32 MN SUFFIX CASE 485CE NB3H 5150–01 AWLYYWWG

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

\*For additional marking information, refer to Application Note AND8002/D.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 18 of this data sheet.

- 1 ps maximum RMS Phase Jitter FRAC-N (CLK4)

161.1328 MHz

- I<sup>2</sup>C / SMBus Compatible Interface

- -40°C to +85°C Ambient Operating Temperature

- Zero ppm Multiplication Error

- Fractional Divide Ratios for Implementing Arbitrary FEC/Inverse–FEC Ratios

- For Additional Pin-strap Frequency and Output Type Combinations, Contact ON Semiconductor Sales Office

- 32-Pin QFN, 5 mm x 5 mm

- This is a Pb-Free Device

#### **Applications**

- Telecom

- Networking

- Ethernet

- SONET

Figure 1. Simplified Block Diagram of NB3H5150-01

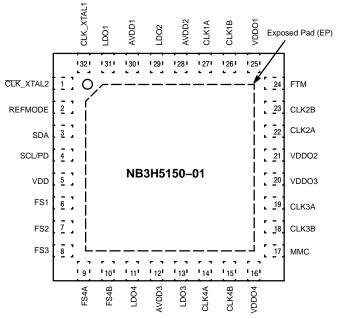

Figure 2. 32-Lead QFN Pinout (Top View)

**Table 1. PIN DESCRIPTION**

| Pin | Name      | I/O                                | Description                                                                                                                                                                                                                   |

|-----|-----------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CLK_XTAL2 | Crystal or<br>LVPECL/LVDS<br>Input | Crystal Output or Differential Clock Input (complementary); If CLK_XTAL1 is used as single–ended input, CLK_XTAL2 must be connected to ground. See Table 2.                                                                   |

| 2   | REFMODE   | LVTTL/LVCMOS<br>Input              | Reference Input Select to either use a crystal, or overdrive with a single-ended or differential input; see Table 2. Internal pull-down.                                                                                      |

| 3   | SDA       | LVTTL/LVCMOS<br>Input              | Serial Data Input for I2C/SMBus compatible; Defaults High when left open; internal pull-up. 5V tolerant.                                                                                                                      |

| 4   | SCL/PD    | LVTTL/LVCMOS<br>Input              | Serial Clock Input for I2C/SMBus compatible; Defaults High when left open; internal pull–up. SCL/PD is also a device power–down pin (when High) in pin–strap mode only. 5V tolerant.                                          |

| 5   | VDD       | Power                              | 3.3 V / 2.5 V Positive Supply Voltage for the Inputs and Core                                                                                                                                                                 |

| 6   | FS1       | LVTTL/LVCMOS<br>Input              | Frequency Select 1 for DIV1, CLK1A & CLK1B; Three–level input buffer; Default is mid–logic level; internal RPull–up and RPull–down. See Table 3.                                                                              |

| 7   | FS2       | LVTTL/LVCMOS<br>Input              | Frequency Select 2 for DIV2, CLK2A & CLK2B; Three–level input buffer; Default is mid–logic level; internal RPull–up and RPull–down. See Table 3.                                                                              |

| 8   | FS3       | LVTTL/LVCMOS<br>Input              | Frequency Select 3 for DIV3, CLK3A, & CLK3B; Three–level input buffer; Default is mid–logic level; internal RPull–up and RPull–down. See Table 3.                                                                             |

| 9   | FS4A      | LVTTL/LVCMOS<br>Input              | Frequency Select 4A for DIV4, CLK4A & CLK4B; Three–level input buffer; Default is mid–logic level; internal RPull–up and RPull–down. See Table 4.                                                                             |

| 10  | FS4B      | LVTTL/LVCMOS<br>Input              | Frequency Select 4B for DIV4, CLK4A & CLK4B; Three–level input buffer; Default is mid–logic level; internal RPull–up and RPull–down. See Table 4.                                                                             |

| 11  | LDO4      | Power                              | 1.8 V LDO – Install Power Conditioning Bypass Capacitor to Ground                                                                                                                                                             |

| 12  | AVDD3     | Power                              | 3.3 V / 2.5 V Positive Supply Voltage for Analog circuits. AVDD3 = VDD.                                                                                                                                                       |

| 13  | LDO3      | Power                              | 1.8V LDO – Install Power Conditioning Bypass Capacitor to Ground                                                                                                                                                              |

| 14  | CLK4A     | Output                             | LVCMOS (single-ended) or Non- Inverted Differential LVPECL Clock A for Channel 4 Output                                                                                                                                       |

| 15  | CLK4B     | Output                             | LVCMOS (single-ended) or Inverted Differential LVPECL Clock B for Channel 4 Output                                                                                                                                            |

| 16  | VDDO4     | Power                              | 3.3 V / 2.5 V / 1.8 V Positive Supply Voltage for the CLK4A/4B Outputs                                                                                                                                                        |

| 17  | MMC       | LVTTL/LVCMOS<br>Input              | Mix Mode Control Pin for use as a combination of FSn settings and I2C setting for the CLK(n) outputs in the I2C mode; see Table 6. No logic level default; use a RPull–up resistor for High or a RPull–down resistor for Low. |

| 18  | CLK3B     | Output                             | LVCMOS (single-ended) or Inverted Differential LVPECL Clock B for Channel 3 Output                                                                                                                                            |

| 19  | CLK3A     | Output                             | LVCMOS (single-ended) or Non-Inverted Differential LVPECL Clock A for Channel 3 Output                                                                                                                                        |

| 20  | VDDO3     | Power                              | 3.3 V / 2.5 V / 1.8 V Positive Supply Voltage for the CLK3A/3B Outputs                                                                                                                                                        |

| 21  | VDDO2     | Power                              | 3.3 V / 2.5 V / 1.8 V Positive Supply Voltage for the CLK2A/2B Outputs                                                                                                                                                        |

| 22  | CLK2A     | Output                             | LVCMOS (single-ended) or Non- Inverted Differential LVPECL Clock A for Channel 2 Output                                                                                                                                       |

| 23  | CLK2B     | Output                             | LVCMOS (single-ended) or Inverted Differential LVPECL Clock B for Channel 2 Output                                                                                                                                            |

| 24  | FTM       |                                    | Factory Test Mode. Must connect this pin to Ground.                                                                                                                                                                           |

| 25  | VDDO1     | Power                              | 3.3 V / 2.5 V / 1.8 V Positive Supply Voltage for the CLK1A/1B Outputs                                                                                                                                                        |

| 26  | CLK1B     | Output                             | LVCMOS (single-ended) or Inverted Differential LVPECL Clock B for Channel 1 Output                                                                                                                                            |

| 27  | CLK1A     | Output                             | LVCMOS (single-ended) or Non-Inverted Differential LVPECL Clock A for Channel 1 Output                                                                                                                                        |

| 28  | AVDD2     | Power                              | 3.3 V / 2.5 V Positive Supply Voltage for Analog circuits. AVDD2 = VDD.                                                                                                                                                       |

| 29  | LDO2      | Power                              | 1.8 V LDO – Install Power Conditioning Bypass Capacitor to Ground                                                                                                                                                             |

| 30  | AVDD1     | Power                              | 3.3 V / 2.5 V Positive Supply Voltage for Analog circuits. AVDD1 = VDD.                                                                                                                                                       |

| 31  | LDO1      | Power                              | 1.8 V LDO – Install Power Conditioning Bypass Capacitor to Ground                                                                                                                                                             |

|     |           |                                    |                                                                                                                                                                                                                               |

**Table 1. PIN DESCRIPTION**

| Pin | Name        | I/O                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32  | CLK_XTAL1   | Crystal or<br>LVTTL/LVCMOS<br>or LVPECL/LVDS<br>Input | Crystal Input or Single–Ended or Differential Clock Input; If CLK_XTAL1 is used as single–ended input, CLK_XTAL2 must be connected to ground. See Table 2.                                                                                                                                                                                                                                     |

| EP  | Exposed Pad | Ground                                                | Ground – Negative Power Supply is connected via the Exposed Pad .  The Exposed Pad (EP) on the QFN–32 package bottom is thermally connected to the die for improved heat transfer out of package. The exposed pad must be attached to a heat sinking conduit. The pad is electrically connected to the die,carries all power supply return currents and must be electrically connected to GND. |

<sup>1.</sup> All VDD, AVDDn, VDDOn, EP (GND) pins must be externally connected to a power supply for proper operation. VDD and AVDDn must all be at the same voltage.

#### **NB3H5150-01 BASIC OPERATION**

#### Introduction

The NB3H5150–01 is a Multi–Rate Clock Generator. The clock reference for the PLL can be either a 25 MHz crystal, single–ended LVCMOS or LVTTL signal or a differential LVPECL, LVDS or HCSL signal.

There are two modes of operation for the NB3H5150–01, Pin–Strap and  $I^2C$ .

In the **Pin–Strap Mode**, the user can select any of the defined output frequencies for each of the four output banks as specified in Tables 3 and 4 via the three–level Frequency Select pins: FS1, FS2, FS3, FS4A and FS4B.

In the **I**<sup>2</sup>**C mode**, the user can select one of the approved register files in Table 5. Each register file is an expanded selection of output frequencies and level combinations, output enable/disable and bypass mode functions.

### CLKnA & CLKnB – Output Frequency and Output Level Selection

There are four output banks: CLK1A&B, CLK2A&B and CLK3A&B are integer only divider outputs, whereas CLK4A&B can be set or programmed as an integer or fractional divider.

The output levels for each output bank can be LVPECL (differential) or LVCMOS (two single-ended). Output Enable / Disable functions are available in I<sup>2</sup>C only.

CLK1, 2, 3 and 4 outputs are not phase–aligned, in PLL or PLL bypass modes.

#### Power-On Output Default

Upon power–up, all four outputs will be forced to and held at static LVPECL levels (CLKnA = Low, CLKnB = High) until the PLL is stable. The PLL will be stable before any of the output Clocks, CLKnx, are enabled.

#### SDA & SCL/PD - Serial Data Interface - I2C

The NB3H5150–01 incorporates a two-wire Serial Data Interface to expand the flexibility and function of the NB3H5150–01 clock generator.

The I<sup>2</sup>C interface pins, SCL and SDA, are used to load register files into the NB3H5150–01.

These register files will configure the internal registers to achieve an expanded selection of output frequencies and levels combinations for each of the four output blocks.

Subsequent changes in the registers can then be performed with another register file to modify any of the output frequencies or output modes.

#### **OE, Output Enable**

An OE, Output Enable/Disable function is available only in the I<sup>2</sup>C mode by loading a register file, such that any individual output bank can be enabled or disabled. In LVCMOS modes outputs will disable LOW for CLKnA and CLKnB, while the LVPECL mode outputs will disable CLKnA = Low and CLKnB = High.

#### **Mixed Mode Control (MMC)**

In the I<sup>2</sup>C mode, the Mixed Mode Control (MMC) pin is used for a combination of FSn settings and I<sub>2</sub>C settings to control the CLK(n) outputs' function as defined in Table 7.

## **REFMODE – Select a Crystal or External Clock Input Interface** (See Table 2)

The REFMODE pin will select the reference input for the CLK\_XTAL1 and CLK\_XTAL2 pins to use either a crystal, an overdriven single–ended or differential input.

When using a crystal, set the REFMODE pin to a LOW. The CLK\_XTAL1 and CLK\_XTAL2 input pins will accept a 25 MHz crystal.

When using a direct-coupled differential input, set the REFMODE pin to a HIGH.

When REFMODE is HIGH, the CLK\_XTAL1 and CLK\_XTAL2 differential input pins have internal AC coupling capacitors selected with self—bias circuity for the differential input buffer. This differential buffer will directly accept any differential signal including LVPECL, LVDS, HCSL or CML. Drive the CLK\_XTAL1 pin with the true

signal and the  $\overline{\text{CLK}}$ \_XTAL2 pin with the complementary signal.

When overdriving the CLK\_XTAL1 input pin with a single-ended signal set REFMODE to a HIGH, and connect CLK\_XTAL2 to Ground. The input has internal AC coupling capacitor with self-bias circuitry.

Table 2. CRYSTAL INPUT INTERFACE AND REFMODE TRUTH TABLE

| Input Mode Crystal/External Clock | REFMODE | CLK_XTAL1                 | CLKb_XTAL2                         |

|-----------------------------------|---------|---------------------------|------------------------------------|

| Crystal                           | LOW     | Use a Crystal             | Use a Crystal                      |

| Any Differential Input            | HIGH    | Overdrive with True Input | Overdrive with Complementary Input |

| Single-Ended Input                | HIGH    | Overdrive                 | Connect to Ground                  |

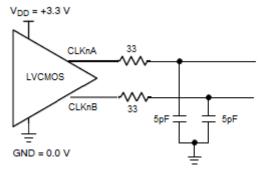

#### **LVCMOS Outputs**

LVCMOS outputs are powered with VDDOn = 3.3 V, 2.5 V or 1.8 V

A 33  $\Omega$  series terminating resistor may be used on each clock output if the metal trace is longer than one inch.

Any unused LVCMOS output can be left floating, but there should be no metal trace attached to the package pin.

#### **LVPECL Differential Outputs**

The differential LVPECL outputs are powered with VDDO = 3.3 V or 2.5 V and must be properly loaded. See Figure 10.

Any unused differential output pair should either be left floating or terminated.

#### **REF Out**

In the PLL bypass mode available via I<sup>2</sup>C, the input reference frequency can be routed to CLK1A and CLK1B as phase aligned LVCMOS or differential LVPECL outputs with the same frequency. The output frequency and duty cycle equals the input frequency and duty cycle.

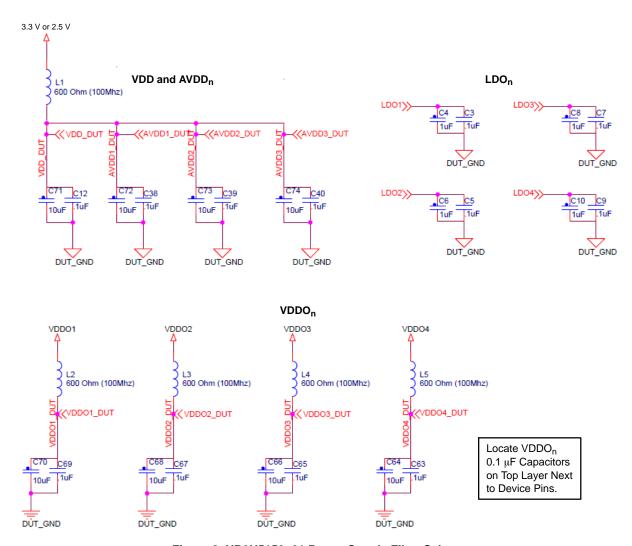

#### **Power Supplies**

The NB3H5150–01 has several power supply pins:

- VDD is the supply voltage for the input and digital core circuitry.

- AVDD1, AVDD2 and AVDD3 powers the core analog circuits. VDD = AVDD1 = AVDD2 = AVDD3.

- VDDO1, VDDO2, VDDO3 and VDDO4 are individual power supplies for each of the four CLKnA/B output banks.

Upon power–up, all four VDDOn pins must be connected to a power supply, even if only one output is being used.

Any combination of VDD and VDDOn power supply voltages is allowed.

A power supply filtering scheme in Figure 8 is recommended for best device performance.

When all VDD, AVDDn and VDDOn pins reach their minimum voltage per Table 10, the NB3H5150-01 will operate at the proper output frequencies.

#### **EP Exposed Pad**

The exposed pad on the bottom side of the package must be connected to Ground.

#### **LDO Pins**

The NB3H5150-01 has integrated low noise 1.8 V Low-Drop-Out (LDO) voltage regulators which provide power internal to the NB3H5150-01.

The LDOs require decoupling capacitors in the range of  $1 \mu F$  to  $10 \mu F$  for compensation and high frequency PSR.

When powered-down, the device turns off the LDOs and enters a low power shutdown mode consuming less than 1 mA.

#### **FTM**

This is a Factory Test Mode pin and must be connected to the Ground of the application for proper operation.

### <u>PIN-STRAP / FSn Frequency Select MODE:</u> (see Tables 3 and 4)

The NB3H5150-01 can be configured to operate in pin-strap mode where the control pins FSnA/B can be set to generate the necessary clock outputs of the device.

#### Prerequisites:

- ◆ SDA and SCL/PD must be Low at all times while in pin-strap mode to enable FS control. If SDA ever goes High, pin-strap is exited and the only way to go back is to power cycle the device.

- Mixed Mode Control pin (MMC) level will be IGNORED.

#### Sequencing:

- 1. Upon device power-up (assuming SCL is LOW)

- a. All four CLK(n) frequency and output type selections will be pre-loaded according to the FS pin settings, but all four outputs will be held at static LVPECL levels (CLKnA = Low, CLKnB = High) until the PLL has become stable

- b. After the PLL is stable, all CLK(n) output type selections (i.e. LVPECL or LVCMOS) will

- become effective and will begin to output the selected frequencies.

- 2. Subsequent changes to any FS pin(s) will cause the associated CLK(n) output(s) to momentarily go to static levels, and then to resume at the new frequency; CLK(n) will follow the FS(n) pin programmable Tables 3 and 4 for output frequencies and interface levels. Note that in changing from LVPECL to LVCMOS (or vice-versa), output logic levels cannot be guaranteed. This is because the receiver inputs are not likely to change in a given application, and the LVPECL output loading in the application will also not change. It is logical to presume that the output type will be predetermined and fixed. Therefore, in a system/application, the user should

- be aware that subsequent change to the FS pin should only change frequency, and not output type.

- 3. Power off/on cycle will repeat the entire sequence

#### 4. Power Down

To initiate the Power–Down mode, the SDA pin must be LOW and remain LOW. If the SCL/PD pin is taken HIGH at any time, the device enters a complete power–down mode with a current consumption of less than 1 mA for the entire device. When SCL/PD is subsequently taken LOW, the device will function as though power were removed and re–applied. That is, sequencing will begin at #1.

Power–down is also available via I<sup>2</sup>C with a register file.

#### FS(n) Pin Programmable Selection of Output Frequencies and Levels

Table 3. NB3H5150-01MNTXG - CLK1A:3A & CLK1B:3B OUTPUT FREQUENCY SELECT TABLE WITH 25 MHz CRYSTAL

| Logic Level  | FS1 (CLK1)<br>(MHz) | FS2 (CLK2)<br>(MHz) | FS3 (CLK3)<br>(MHz) |

|--------------|---------------------|---------------------|---------------------|

| Low          | 156.25 (LVPECL)     | 156.25 (LVPECL)     | 156.25 (LVPECL)     |

| Mid / Float* | 25.00 (LVPECL)      | 100.00 (LVPECL)     | 125.00 (LVPECL)     |

| High         | 50.00 (LVPECL)      | 125.00 (LVPECL)     | 50.00 (LVPECL)      |

<sup>\*(</sup>Default)

Table 4. NB3H5150-01MNTXG - CLK4A & CLK4B OUTPUT FREQUENCY SELECT TRUTH TABLE (MHz) WITH 25 MHz CRYSTAL\*

| FS4A         | FS4B         | CLK4 (MHz)        | Divider Type |

|--------------|--------------|-------------------|--------------|

| Low          | Low          | 33.33 (LVCMOS)    | Integer      |

| Low          | Mid / Float  | 66.66 (LVCMOS)    | Fractional   |

| Low          | High         | 133.33 (LVCMOS)   | Fractional   |

| Mid / Float  | Low          | 133.33 (LVPECL)   | Fractional   |

| Mid / Float* | Mid / Float* | 156.25 (LVPECL)   | Integer      |

| Mid / Float  | High         | 125.00 (LVPECL)   | Integer      |

| High         | Low          | 25.00 (LVPECL)    | Integer      |

| High         | Mid / Float  | 100.00 (LVPECL)   | Integer      |

| High         | High         | 161.1328 (LVPECL) | Fractional   |

<sup>\*(</sup>Default)

#### I<sup>2</sup>C MODE: (see Table 6)

Some features that are not available in pin-strap mode can be obtained in I2C mode, such as Output Enable/Disable, By-Pass mode and Power-Down. In addition, output frequency and output levels can also be I2C controlled.

The NB3H5150–01 I2C Programming Guide can be found on the NB3H5150–01 web site. This application note provides details on configuring the NB3H5150–01 by writing to registers in the NB3H5150–01 with approved register files through the I2C/SMBus interface.

http://www.onsemi.com/pub/Collateral/NB3H5150-01%2 0I2C%20PROGRAMMING%20GUIDE%20%20..PDF

The user can select a Register File from the ON Semiconductor website from the NB3H5150–01 I2C Register Files folder. Additional Register Files can be generated by the factory upon request.

http://www.onsemi.com/pub/Collateral/NB3H5150-01%2012C%20REGISTER%20FILES.ZIP

#### Prerequisites:

- SDA and SCL must be connected to I<sup>2</sup>C SMBus

- SDA must be logic High.

- 1. Upon device power-up.

- a. All four frequencies and output type selections will be preloaded according to the FSn pin settings, but all four outputs will be held at static LVPECL levels until the PLL has become stable.

- **NOTE:** After power up, changes to FS pins will be blocked from controlling device operation.

- b. Once the PLL is stable, the Mixed Mode Control pin (MMC) is checked:

- i. If MMC is LOW, all CLK(n) outputs will remain at static LVPECL levels.

- ii. If MMC is HIGH and FS4A is LOW, CLK1, CLK2, and CLK3 outputs will remain at static LVPECL levels.

- CLK4A/4B output frequency and output levels will become active after PLL stabilization time according to FS4A and FS4B pin selection in Table 4.

- After power up, changes to all pins will be ignored.

- iii. If MMC is HIGH and FS4A MID or HIGH, CLK1, CLK2, and CLK3 output frequency and type will become active after PLL

stabilization time according to their respective FS1, FS2 and FS3 pin selection in Table 3.

CLK4A/4B outputs remain at Static LVPECL Levels.

- After power up, changes to all pins will be ignored except the SDA and SCL inputs.

- iv. The FS4A and FS4B pins set the bus address when MMC pin is LOW (see Table 6, I2C Device Address Table).

- c. The I<sup>2</sup>C interface can now be used to load register files into the NB3H5150–01. In I<sup>2</sup>C Mode, configuration of Output Enables, output frequency, output levels of each output, specific block power–down control, bypass mode, etc. are all possible.

- d. Any outputs which were held in static level mode (described above) will be released for operation.

CLK(n) outputs will be active at the programmed frequencies and levels.

CLK(n) outputs will react to any subsequent changes to the I<sup>2</sup>C bus.

If any output channel is not programmed, then output is loaded from FSn pins.

A Power Cycle will clear all previous register information and I<sup>2</sup>C mode will repeat to number 1 in the power up sequence.

To simplify device configuration, ON Semiconductor provides desktop software, that can be downloaded from http://www.onsemi.com/pub/Collateral/NB3H5150-01\_G UI.ZIP which will operate in conjunction with the NB3H5150-01 evaluation board (EVB). The NB3H5150-01 GUI manual can also be found on the web site.

When the software is connected to an NB3H5150-01 EVB, it can control the selection of numerous clock output frequencies for each of the four CLK outputs and the output type as well as Output Enable/Disable.

### I<sup>2</sup>C Programmable Selection of Output Frequency and Level

Table 5 contains register files that produce various combinations of output frequencies and output types.

Each register file can be loaded from GUI into the demo board, or loaded into the I<sup>2</sup>C port of the device.

Table 5. I<sup>2</sup>C OUTPUT FREQUENCY AND MODE SELECTION REGISTERS

| Reg.FILE# | CLK1 (MHz)    | CLK2 (MHz)    | CLK3 (MHz)    | CLK4 (MHz)    |

|-----------|---------------|---------------|---------------|---------------|

| 1         | 100 LVPECL    | 125 LVPECL    | 156.25 LVPECL | 155.52 LVPECL |

| 2         | 100 LVPECL    | 100 LVPECL    | 125 LVPECL    | 125 LVPECL    |

| 3         | 25 LVCMOS     | Disabled      | 156.25 LVPECL | 70.656 LVPECL |

| 4         | 25 LVCMOS     | Disabled      | 100 LVPECL    | Disabled      |

| 5         | 25 LVCMOS     | 156.25 LVPECL | 156.25 LVPECL | 156.25 LVPECL |

| 6         | 25 LVCMOS     | 100 LVPECL    | 100 LVPECL    | Disabled      |

| 7         | 156.25 LVPECL | 156.25 LVPECL | 156.25 LVPECL | 156.25 LVPECL |

| 8         | 50.00 LVPECL  | 125.00 LVPECL | 156.25 LVPECL | 133.33 LVCMOS |

| 9         | Bypass LVCMOS | 156.25 LVPECL | 100.00 LVPECL | 156.25 LVPECL |

| 10        | Bypass LVPECL | 156.25 LVPECL | 156.25 LVPECL | 156.25 LVPECL |

| 11        | Bypass LVCMOS | 156.25 LVPECL | 156.25 LVPECL | 156.25 LVPECL |

| 12        | Disabled      | Disabled      | Disabled      | Disabled      |

Table 6. SDA, SCL AND MMC CONTROL PINS FOR OUTPUT FUNCTION

|                              |             |             |                       |                                                             | Outputs                       | (Note 2)                        |

|------------------------------|-------------|-------------|-----------------------|-------------------------------------------------------------|-------------------------------|---------------------------------|

| Mode                         | SDA         | SCL/PD      | ммс                   | Comments                                                    | CLK1, CLK2,<br>CLK3           | CLK4                            |

| Pin-Strap FS Mode            | L           | L           | Х                     | Normal Operation                                            | Toggle per Table 3            | Toggle per Table 4              |

| Power-Down                   | L           | Н           | Х                     |                                                             | Off                           | Off                             |

| I <sup>2</sup> C<br>(Note 3) | Dynamic     | Dynamic     | Х                     | I2C Mode Is Active After<br>Mixed Mode Power–Up<br>Sequence | Active Per I2C Map            | Active Per I <sup>2</sup> C Map |

|                              | H<br>Note 4 | H<br>Note 4 | L                     |                                                             | Static LVPECL<br>Logic Levels | Static LVPECL<br>Logic Levels   |

| Mixed Mode                   | H<br>Note 4 | H<br>Note 4 | H<br>FS4A = L         |                                                             | Static LVPECL<br>Logic Levels | Active per Table 4              |

|                              | H<br>Note 4 | H<br>Note 4 | H<br>FS4A =<br>M or H |                                                             | Active per Table 3            | Static LVPECL<br>Logic Levels   |

**Table 7. ATTRIBUTES**

|                    | Characteristics                                          | Value                        |

|--------------------|----------------------------------------------------------|------------------------------|

| ESD Protection     | Human Body Model<br>Machine Model<br>Charge Device Model | > 2 kV<br>> 150 V<br>> 500 V |

| Moisture Sensitivi | ty (Note 5) 32-QFN                                       | Level 1                      |

| Flammability Ratin | ng Oxygen Index: 28 to 34                                | UL 94 V-0 @ 0.125 in         |

| Transistor Count   |                                                          | 245, 894                     |

| Meets or exceeds   | JEDEC Spec EIA/JESD78 IC Latchup Test                    |                              |

<sup>5.</sup> For additional information, see Application Note AND8003/D.

All outputs are static until after the PLL is stable.

Any changes to the device configuration after power-up are made by reading and writing to registers through the I2C interface.

Don't care state unless device address is matched by controller address.

X = don't care

**Table 8. MAXIMUM RATINGS**

| Symbol            | Parameter                                         |                  | Condition          | Rating                          | Unit         |

|-------------------|---------------------------------------------------|------------------|--------------------|---------------------------------|--------------|

| $V_{DD}$          | Positive Power Supply – Core                      |                  | GND = 0 V          | 3.63                            | V            |

| $AV_{DDn}$        | Positive Power Supply – Analog                    |                  | GND = 0 V          | 3.63                            | V            |

| $V_{DDOn}$        | Positive Power Supply – Outputs                   |                  | GND = 0 V          | 3.63                            | V            |

| V <sub>IO</sub>   | Positive Input/Output Voltage                     |                  | GND = 0 V          | -0.5 to V <sub>DD</sub><br>+0.5 | V            |

| VI                | Positive Input Voltage SDA and SCL                |                  | GND = 0 V          | 5.5                             | V            |

| T <sub>A</sub>    | Operating Temperature Range                       |                  | QFN-32             | -40 to +85                      | °C           |

| T <sub>stg</sub>  | Storage Temperature Range                         |                  |                    | -65 to +150                     | °C           |

| $\theta_{J}$      | Maximum Junction Temperature                      |                  |                    | 125                             | °C           |

| $\theta_{JA}$     | Thermal Resistance (Junction-to-Ambient) (Note 6) | QFN-32<br>QFN-32 | 0 lfpm<br>500 lfpm | 31<br>27                        | °C/W<br>°C/W |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case) (Note 6)    | QFN-32           |                    | 12                              | °C/W         |

| TJ                | Maximum Junction Temperature                      |                  |                    | 125                             | °C           |

| T <sub>sol</sub>  | Wave Solder Pb-Free, 10 sec                       |                  |                    | 265                             | °C           |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

6. JEDEC standard multilayer board – 2S2P (2 signal, 2 power).

#### **Table 9. DC CHARACTERISTICS**

$V_{DD} = AV_{DD0} = 3.3 \text{ V} + 5\% \text{ or } 2.5 \text{ V} + 5\% \text{: } V_{DD00} = 3.3 \text{ V} + 5\% \text{ or } 2.5 \text{ V} + 5\% \text{ or } 1.8 \text{ V} + 5\% \text{: } GND = 0 \text{ V} : T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$

| Symbol                                                  | Characteristic                                                                                                                                                                                                                                                                                               | Min                                      | Тур                             | Max                                      | Unit |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------|------------------------------------------|------|

| POWER SU                                                | PPLY / CURRENT (Note 12)                                                                                                                                                                                                                                                                                     |                                          |                                 |                                          |      |

| V <sub>DD</sub> /AV <sub>DDn</sub><br>V <sub>DDOn</sub> | $\begin{array}{c} \text{Core Power Supply} & \text{$V_{DD} = AV_{DDn} = 3.3 \text{ V}$} \\ \text{$V_{DD} = AV_{DDn} = 2.5 \text{ V}$} \\ \text{Output Power Supply} & \text{$V_{DDOn} = 3.3 \text{ V}$} \\ \text{$V_{DDOn} = 2.5 \text{ V}$} \\ \text{$V_{DDOn} = 1.8 \text{ V (LVCMOS only)}$} \end{array}$ | 3.135<br>2.375<br>3.135<br>2.375<br>1.71 | 3.3<br>2.5<br>3.3<br>2.5<br>1.8 | 3.465<br>2.625<br>3.465<br>2.625<br>1.89 | V    |

| I <sub>DD</sub> /I <sub>ADDn</sub>                      | Core and Input Power Supply Current for $V_{DD}$ and $A_{VDDn}$ CLK4 Integer CLK4 Frac-N $V_{DD}$ = 2.5 V CLK4 Integer CLK4 Frac-N                                                                                                                                                                           |                                          | 60<br>75<br>55<br>70            | 75<br>90<br>70<br>85                     | mA   |

| I <sub>DDOn</sub>                                       | Output Buffer Power Supply Current for $V_{DDOn}$ Incremental $I_{DDO}$ Current by One Output Bank and Output Type LVPECL – One differential LVPECL output pair (CLKnA & CLKnB) Frequency Independent $V_{DDO} = 3.3 \text{ V}$ $V_{DDO} = 2.5 \text{ V}$                                                    |                                          | 40<br>40                        | 50<br>50                                 | mA   |

|                                                         | LVCMOS – Two LVCMOS outputs (CLKnA & CLKnB)<br>$f = 50 \text{ MHz}$ $V_{DDO} = 3.3 \text{ V}$ $V_{DDO} = 2.5 \text{ V}$ $V_{DDO} = 1.8 \text{ V}$                                                                                                                                                            |                                          | 20<br>17<br>15                  | 25<br>23<br>21                           |      |

| I <sub>DD</sub> PWRDN                                   | Power Down Current SCL/PD = High                                                                                                                                                                                                                                                                             |                                          | 100                             |                                          | μΑ   |

| LVPECL OU                                               | <b>TPUTS</b> (Note 7 and 8) $V_{DDOn}$ = 3.3 $V \pm 5\%$ or 2.5 $V \pm 5\%$ ; See Figure 10                                                                                                                                                                                                                  | )                                        |                                 |                                          |      |

| V <sub>OH</sub>                                         | Output HIGH Voltage                                                                                                                                                                                                                                                                                          | V <sub>DDO</sub> – 1.200                 |                                 | V <sub>DDO</sub> - 0.895                 | V    |

| V <sub>OH</sub>    | Output HIGH Voltage                  | V <sub>DDO</sub> – 1.200 |     | V <sub>DDO</sub> – 0.895 | V  |

|--------------------|--------------------------------------|--------------------------|-----|--------------------------|----|

| V <sub>OL</sub>    | Output LOW Voltage                   | V <sub>DDO</sub> – 2.000 |     | V <sub>DDO</sub> – 1.600 | V  |

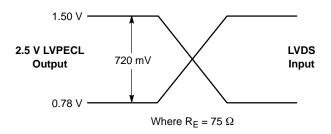

| V <sub>SWING</sub> | V <sub>OUT PK-PK</sub> Voltage Swing | 550                      | 720 | 900                      | mV |

#### **Table 9. DC CHARACTERISTICS**

$V_{DD} = AV_{DDn} = 3.3 \text{ V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 5\%; V_{DDOn} = 3.3 \text{ V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 5\% \text{ or } 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C} = 1.8 \text{ V} \pm 1.8 \text$

| Symbol             | Characteristic                                                                                | Min                    | Тур | Max                     | Unit |

|--------------------|-----------------------------------------------------------------------------------------------|------------------------|-----|-------------------------|------|

| LVCMOS O           | UTPUT; See Figure 12                                                                          |                        | •   | •                       |      |

| V <sub>OH</sub>    | Output HIGH Voltage IOH = 12 mA                                                               | V <sub>DDO</sub> – 0.5 |     | $V_{DDO}$               | V    |

| V <sub>OL</sub>    | Output LOW Voltage IOL = 12 mA                                                                | GND                    |     | 0.5                     | V    |

| R <sub>OUT</sub>   | Output Impedance                                                                              |                        | 15  |                         | Ω    |

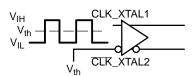

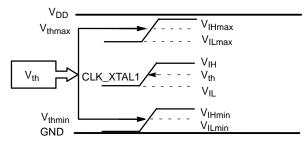

|                    | NPUT DRIVEN SINGLE-ENDED (REFMODE = 1) (see Figure 3 and 5)                                   | (Note 9)               |     |                         |      |

| V <sub>IHSE</sub>  | CLK_XTAL1 Single-Ended Input HIGH Voltage                                                     | 200                    |     | V <sub>DD</sub> + 300   | mV   |

| V <sub>ILSE</sub>  | CLK_XTAL1 Single–Ended Input LOW Voltage                                                      | GND – 300              |     | V <sub>IHSE</sub> – 200 | mV   |

| V <sub>th</sub>    | Input Threshold Reference Voltage Range                                                       | 100                    |     | V <sub>DD</sub> – 100   | mV   |

| V <sub>ISE</sub>   | Single-Ended Input Voltage (V <sub>IH</sub> - V <sub>IL</sub> )                               | 200                    |     | V <sub>DD</sub> + 600   | mV   |

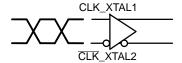

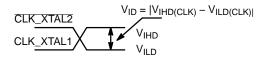

| CRYSTAL I          | NPUTS DRIVEN DIFFERENTIALLY (REFMODE = 1) (see Figure 4 and                                   | 6) (Note 11)           |     | •                       |      |

| V <sub>IHD</sub>   | Differential Input HIGH Voltage                                                               | 100                    |     | $V_{DD}$                | mV   |

| V <sub>ILD</sub>   | Differential Input LOW Voltage                                                                | GND                    |     | V <sub>IHD</sub> – 100  | mV   |

| V <sub>ID</sub>    | Differential Input Voltage (V <sub>IHD</sub> – V <sub>ILD</sub> )                             | 100                    |     | V <sub>DD</sub>         | mV   |

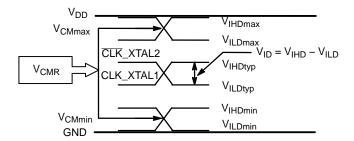

| V <sub>CMR</sub>   | Input Common Mode Range (Differential Configuration) (Note 10) (Figure 8)                     | 50                     |     | V <sub>DD</sub> – 50    | mV   |

| I <sub>IH</sub>    | Input HIGH Current CLK_XTAL1 and CLKb_XTAL2                                                   | -10                    |     | 10                      | μА   |

| I <sub>IL</sub>    | Input LOW Current CLK_XTAL1 & CLKb_XTAL2                                                      | -10                    |     | 10                      | μΑ   |

| LVCMOS -           | CONTROL AND SDA & SCL/PD INPUTS                                                               |                        |     |                         |      |

| V <sub>IH</sub>    | Input HIGH Voltage for MMC & REFMODE Pins $V_{DD} = 3.3 \text{ V}$ $V_{DD} = 2.5 \text{ V}$   | 2.1<br>1.75            |     | V <sub>DD</sub> + 0.3   | V    |

| V <sub>IH</sub>    | Input HIGH Voltage for SDA & SCL/PD Pins $V_{DD} = 3.3 \text{ V}$ $V_{DD} = 2.5 \text{ V}$    | 2.1<br>1.75            |     | 5.5                     | V    |

| V <sub>IL</sub>    | Input LOW Voltage for Control Pins and SDA & SCL/PD $$ V $_{DD}$ = 3.3 V $$ V $_{DD}$ = 2.5 V | GND – 0.3              |     | 0.7<br>0.7              | V    |

| I <sub>IH</sub>    | Input HIGH Current                                                                            | <b>–150</b>            |     | 150                     | μΑ   |

| I <sub>IL</sub>    | Input LOW Current                                                                             | <b>–150</b>            |     | 150                     | μΑ   |

| VIH <sub>tri</sub> | Tri-Level Input High Voltage (FSn pins)                                                       | V <sub>DD</sub> x 75%  |     | $V_{DD}$                |      |

|                    | V <sub>DD</sub> = 3.3 V                                                                       | 2.48                   |     | $V_{DD}$                | V    |

|                    | V <sub>DD</sub> = 2.5 V                                                                       | 1.88                   |     | V <sub>DD</sub>         |      |

| VIM <sub>tri</sub> | Tri-Level Input Med Voltage (FSn pins)                                                        | V <sub>DD</sub> x 40%  |     | V <sub>DD</sub> x 60%   |      |

|                    | V <sub>DD</sub> = 3.3 V                                                                       | 1.32                   |     | 1.98                    | V    |

|                    | V <sub>DD</sub> = 2.5 V                                                                       | 1.00                   |     | 1.67                    | 1    |

| VIL <sub>tri</sub> | Tri-Level Input Low Voltage (FSn pins)                                                        | GND                    |     | V <sub>DD</sub> x 25%   | V    |

|                    | V <sub>DD</sub> = 3.3 V                                                                       | 0.00                   |     | 0.83                    | .,   |

|                    | V <sub>DD</sub> = 2.5 V                                                                       | 0.00                   |     | 0.63                    | V    |

| RIN                | Input Impedance                                                                               |                        | 10  |                         | kΩ   |

| CIN                | Input Capacitance – Crystal pins; REFMODE = H                                                 |                        | 2   |                         | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

- 7. LVPECL Outputs loaded with 50  $\Omega$  to V<sub>DDO</sub> 2 V for proper operation. 8. LVPECL Output parameters vary 1:1 with V<sub>DDO</sub>.

- 9. VIH, VIL, V<sub>th</sub>, and VISE parameters must be complied with simultaneously. 10. V<sub>CMR</sub> min varies 1:1 with GND, V<sub>CMR</sub> max varies 1:1 with V<sub>DD</sub>. 11. V<sub>IHD</sub>, V<sub>ILD</sub>, V<sub>ID</sub> and V<sub>CMR</sub> parameters must be complied with simultaneously. 12. I<sub>DD</sub> / V<sub>DD</sub> is independent of I<sub>DDOn</sub>/ V<sub>DDOn</sub>

#### Table 10. AC CHARACTERISTICS

$V_{DD} = AV_{DDn} = 3.3 \text{ V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 5\%; V_{DDO} = 3.3 \text{V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 5\% \text{ or } 1.8 \text{ V} \pm 5\%; \text{ GND} = 0 \text{ V}; T_{A} = -40^{\circ}\text{C to } 85^{\circ}\text{C (Note } 13)$

| Symbol                | Characteristic                                                                                                                                                                                                                 | Min                | Тур                                                    | Max                | Unit |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------|--------------------|------|

| f <sub>CLKIN</sub>    | External Clock / Crystal Input Frequency – PLL Mode                                                                                                                                                                            |                    | 25                                                     | +1000 ppm          | MHz  |

| f <sub>INBP</sub>     | External Clock Input Frequency – PLL Bypass Mode I <sup>2</sup> C Mode; $f_{in} = f_{out}$                                                                                                                                     | 1                  |                                                        | 50                 | MHz  |

| f <sub>CLK1,2,3</sub> | CLK1, CLK2, CLK3 Typical Output Clock Frequencies; f <sub>in</sub> = 25 MHz                                                                                                                                                    |                    | 25<br>50<br>100<br>125<br>156.25                       |                    | MHz  |

| fCLK4                 | CLK4 Outputs Typical Output Clock Frequencies; $f_{in}$ = 25 MHz Resolution of 1 Hz Integer                                                                                                                                    |                    | 25<br>33.33<br>100<br>125<br>156.25<br>66.66<br>133.33 |                    | MHz  |

|                       |                                                                                                                                                                                                                                |                    | 161.1328                                               |                    |      |

| fSDA/SCL              | Serial Data and Clock Rates                                                                                                                                                                                                    |                    | 100k                                                   |                    | bps  |

| t <sub>PWSCL</sub>    | Serial Clock Pulse Width                                                                                                                                                                                                       | 1                  |                                                        |                    | μS   |

| $t_{w\mu}$            | Time SCL/PD Pin must be Held Low to "Wake-up" the Device                                                                                                                                                                       | 100                |                                                        |                    | ns   |

| t <sub>DC</sub>       | Output Clock Duty Cycle (Crystal or Reference Duty Cycle = 50%) PLL Mode; <1 ns $t_f$ / $t_f$ LVPECL $t_{out}$ = 156.25 MHz LVCMOS $t_{out}$ = 33.33 MHz PLL Bypass Mode; Input Duty Cycle = 50%, $t_{INPP} \ge 1.2 \text{ V}$ | 47.5<br>47.5<br>45 | 50<br>50                                               | 52.5<br>52.5<br>55 | %    |

| $\Phi_{N}$            | Phase Noise (Integer–N)  fout = 156.25 MHz, fin = 25 MHz Crystal, LVPECL  1 kHz 10 kHz 100 kHz 1 MHz 10 MHz 20 MHz                                                                                                             |                    | -115<br>-130<br>-140<br>-145<br>-153<br>-153           |                    | dBc  |

| $\Phi_{N}$            | Phase Noise (Integer–N) fout = 100 MHz, fin = 25 MHz Crystal, LVCMOS  1 kHz 10 kHz 100 kHz 1 MHz 10 MHz 20 MHz                                                                                                                 |                    | -120<br>-136<br>-142<br>-145<br>-156                   |                    | dBc  |

| $\Phi_{N}$            | Phase Noise (Frac-N) fout = 161.1328 MHz, fin = 25 MHz Crystal, LVPECL  1 kHz 10 kHz 100 kHz 1 MHz 10 MHz 20 MHz                                                                                                               |                    | -118<br>-128<br>-130<br>-132<br>-153<br>-153           |                    | dBc  |

| $\Phi_{N}$            | Phase Noise (Frac-N) fout = 133.33 MHz, fin = 25 MHz Crystal, LVCMOS  1 kHz 10 kHz 100 kHz 1 MHz 10 MHz 20 MHz                                                                                                                 |                    | -117<br>-126<br>-126<br>-131<br>-153<br>-153           |                    | dBc  |

| $tjit(\Phi)$          | RMS Phase Jitter – 25 MHz Crystal (Note 15)<br>Integration Range:12 kHz – 20 MHz<br>fout = 156.25 MHz, Integer CLK <sub>n</sub><br>fout = 161.1328 MHz; Frac–N CLK4                                                            |                    |                                                        | 300<br>1000        | fs   |

#### **Table 10. AC CHARACTERISTICS**

$V_{DD} = AV_{DDn} = 3.3 \text{ V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 5\%; V_{DDO} = 3.3 \text{V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 5\% \text{ or } 1.8 \text{ V} \pm 5\%; \text{GND} = 0 \text{ V}; T_{A} = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C} \text{ (Note 13)} = 1.8 \text{ V} \pm 5\%; \text{Comparison} = 1.8 \text{ V} \pm 5\%;$

| Symbol                         | Characteristic                                                                                                                                                                                                   | Min        | Тур              | Max         | Unit |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-------------|------|

| tjit(Φ)                        | Additive RMS Phase Jitter (PLL Bypass in I <sup>2</sup> C Mode) Integration Range:12 kHz – 5 MHz fout = 25 MHz, CLK1  LVCMOS                                                                                     |            | 50               |             | fs   |

| tpd                            | Input to Output Propagation Delay (PLL Bypass in I <sup>2</sup> C Mode) 25 MHz                                                                                                                                   |            | 5                |             | ns   |

| PSRR                           | Ripple Induced Phase Spur Level 100 kHz & 1 MHz, 100 mVpp, Ripple Injected on $V_{DD}/AV_{DDn} \le$ 100 MHz                                                                                                      |            | -60              |             | dBc  |

| t <sub>r</sub> /t <sub>f</sub> | Output Rise/Fall Times (CLKnA/CLKnB), 20% – 80% of VDDO <sub>n</sub> fout = 156.25 MHz LVPECL fout = 33.33 MHz @ VDDO = 3.3 V LVCMOS – 5 pF                                                                      | 120<br>500 | 200<br>800       | 300<br>1000 | ps   |

| V <sub>INPP</sub>              | Input Voltage Swing (Differential Configuration) (Note 14)                                                                                                                                                       | 100        |                  | 1200        | mV   |

| Stabilization<br>Time          | Stabilization Time From Power–up VDD = 3.3 V to First Edge Out Upon Reprogram – (Pin–Strap mode), Change of Configuration Power–up to Static Output Levels – (Pin–Strap mode) Power–up to I <sup>2</sup> C Ready |            | 5<br>3<br>1<br>5 | 6           | ms   |

| t <sub>PWRDWN</sub>            | Time to Power Down, SCL/PD Low-to-High                                                                                                                                                                           | 50         | 100              | 200         | μs   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

Figure 3. Differential Input Driven Single-Ended

Figure 4. Differential Inputs Driven Differentially

Figure 5. V<sub>th</sub> Diagram

Figure 6. Differential Inputs Driven Differentially

<sup>13.</sup> Measured by using a 25 MHz crystal as clock source. All LVPECL outputs are loaded with an external  $R_L = 50 \Omega$  to  $V_{DDO} - 2 V$  (Figure 9); LVCMOS outputs loaded with  $R_S=33~\Omega$ ,  $C_L=5~pF$ ,  $5"50~\Omega$  trace, (Figure 11). 14. Input and output voltage swings are single–ended measurements operating in a differential mode. 15.  $V_{DD}=3.3~V$ ,  $V_{DDO}=2.5~V$  (LVPECL) or 1.8 V (LVCMOS).

Figure 7. V<sub>CMR</sub> Diagram

Figure 8. NB3H5150-01 Power Supply Filter Scheme

Table 11. RECOMMENDED CRYSTAL SPECIFICATIONS

| Crystal                      | Fundamental AT-Cut |

|------------------------------|--------------------|

| Frequency                    | 25 MHz             |

| Load Capacitance             | 16 pF – 20 pF      |

| Shunt Capacitance, C0        | 7 pF Max           |

| Equivalent Series Resistance | 50 Ω Max           |

| Initial Accuracy at 25°C     | ± 20 ppm           |

| Temperature Stability        | ± 30 ppm           |

| Aging                        | ± 20 ppm           |

| C0/C1 Ratio                  | 250 Max            |

| Crystal max Drive Level      | 100 μW             |

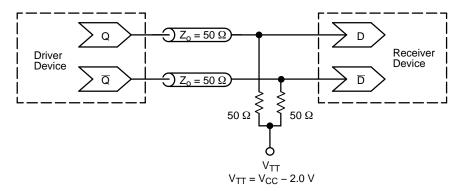

Figure 9. Typical Termination for LVPECL Output Driver and Device Evaluation (See Application Note AND8020/D – Termination of ECL Logic Devices.)

Figure 10. Optional LVPECL output Loading and Termination

Figure 11. Typical LVCMOS Output Test Setup for Evaluation

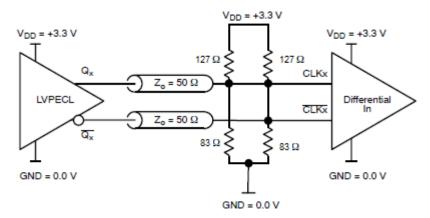

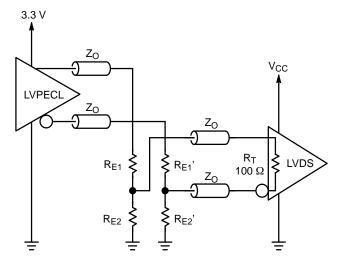

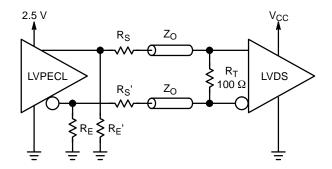

#### Interfacing from 3.3 V LVPECL to LVDS

Since the output levels  $V_{OH}$  and  $V_{OL}$  of 3.3 V LVPECL are more positive than the input range of LVDS receiver, a special interface is required. (See Figures 12 and 13). Furthermore, the open emitter design of the ECL output structure needs proper termination, which can be implemented with a resistor divider network to generate proper LVDS DC levels (eq. 1).

$$R_{E1} + R_{E2} = R_E$$

(eq. 1)

The resistor divider network will divide the output common mode voltage of LVPECL ( $V_{CM}(LVPECL)$ ) to input common mode voltage of LVDS ( $V_{CM}(LVDS)$ ).

$$\frac{R_{E2}}{R_{E1}+R_{E2}} = \frac{V_{CM}(LVDS)}{V_{CM}(LVPECL)} \tag{eq. 2} \label{eq. 2}$$

Where:

$R_{E1}$  = partial emitter current bias resistor

$R_{E2}$  = partial emitter current bias resistor

$R_E = R_{E1} + R_{E2}$ , the total emitter current bias resistor (see AND8020)

V<sub>CM</sub>(LVPECL) = Common Mode Voltage

$V_{CM}(LVDS) = Common Mode Voltage$

3.3 V LVPECL output will be able to drive an LVDS receiver with or without an internal 100  $\Omega$  termination resistor.

Figure 12. Interfacing 3.3 V LVPECL to LVDS

Figure 13. Interfacing LVPECL to LVDS with Internal 100  $\Omega$  Termination Resistor

Examples:

For 50  $\Omega$  controlled impedance, the resistor values for 3.3V LVPECL converted to LVDS voltage levels are as follows:

$R_{E1} = 55 \Omega$

$R_{E2} = 95 \Omega$

$R_{E1}+R_{E2}=R_E=150\;\Omega$

$R_T=100\;\Omega$

$V_{CM}(LVPECL) = 1.9 V$

$V_{CM}(LVDS) = 1.2 \text{ V}$

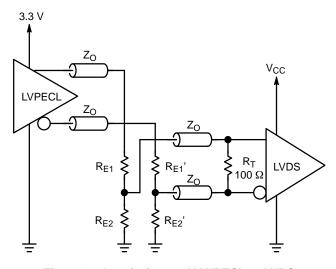

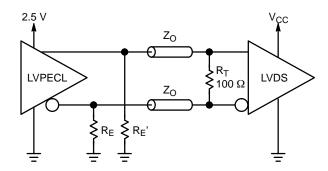

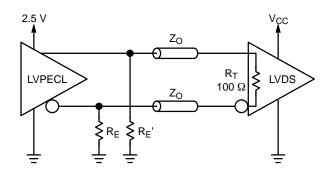

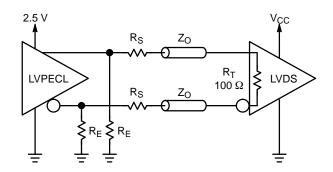

#### Interfacing from 2.5 V LVPECL to LVDS

Provided that the LVDS receiver can tolerate large input voltage peak to peak amplitude, the 2.5 V LVPECL output can be directly interfaced to an LVDS receiver using proper ECL termination. The 2.5 V LVPECL output will be able to drive an LVDS receiver with or without internal 100  $\Omega$  termination resistor. (See Figures 14, 15 and 16).

Figure 14. Interfacing 2.5 V LVPECL to LVDS with External 100  $\Omega$  Termination Resistor

Figure 15. Interfacing 2.5 V LVPECL to LVDS with Internal 100  $\Omega$  Termination Resistor

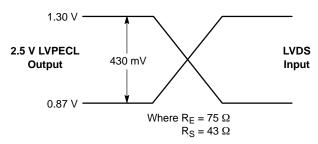

Figure 16. PSPICE Simulation Levels of 2.5V LVPECL to LVDS Interface with Example Resistor Values

Furthermore, a series termination can be used to reduce the amplitude of the signal as described in AND8020 application note, by placing R<sub>S</sub> resistor between the driver and the transmission line. (See Figures 17, 18 and 19).

Figure 17. Interfacing 2.5 V LVPECL to LVDS with Series  $R_S$  and External 100  $\Omega$  Termination Resistor

Figure 18. Interfacing 2.5 V LVPECL to LVDS with Series  $R_S$  and Internal 100  $\Omega$  Termination Resistor

Figure 19. PSPICE Simulation Levels of 2.5V LVPECL to LVDS Interface with Series R<sub>S</sub> Resistor

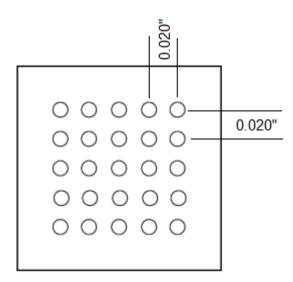

Figure 20. Via Layout Recommendation for Exposed Pad, QFN-32 Package

The exposed pad on the NB3H5150–01 QFN–32 package carries all of the power supply return currents. It is therefore important that the necessary current capability be satisfied, as well as the thermal transfer from the die to the PCB. Figure 20 shows a recommended via layout pattern for the exposed pad. Via spacing = 0.02", filled vias preferred.

#### **ORDERING INFORMATION**

| Device           | Marking         | Tables | Package             | Shipping <sup>†</sup> |

|------------------|-----------------|--------|---------------------|-----------------------|

| NB3H5150-01MNTXG | NB3H<br>5150-01 | 3 & 4  | QFN-32<br>(Pb-Free) | 1000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

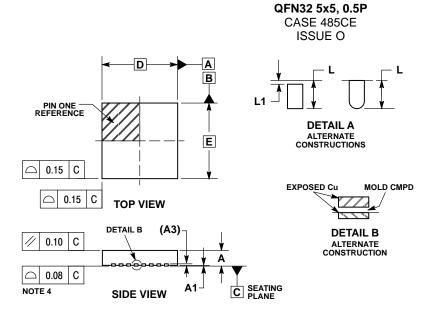

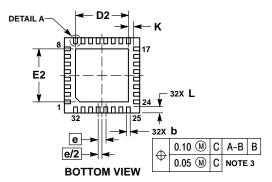

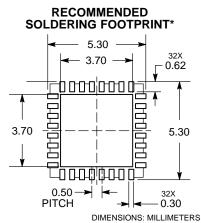

#### PACKAGE DIMENSIONS

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED

- TERMINAL AND IS MEASURED BETWEEN

0.15 AND 0.30 MM FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED

PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.80        | 1.00 |  |

| A1  |             | 0.05 |  |

| А3  | 0.20 REF    |      |  |

| b   | 0.20 0.30   |      |  |

| D   | 5.00 BSC    |      |  |

| D2  | 3.40        | 3.60 |  |

| Е   | 5.00 BSC    |      |  |

| E2  | 3.40        | 3.60 |  |

| е   | 0.50 BSC    |      |  |

| K   | 0.20        |      |  |

| L   | 0.30        | 0.50 |  |

| L1  |             | 0.15 |  |

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative