# 2.5 V, 3.3 V Differential 1:2 **HCSL Fanout Buffer**

#### Description

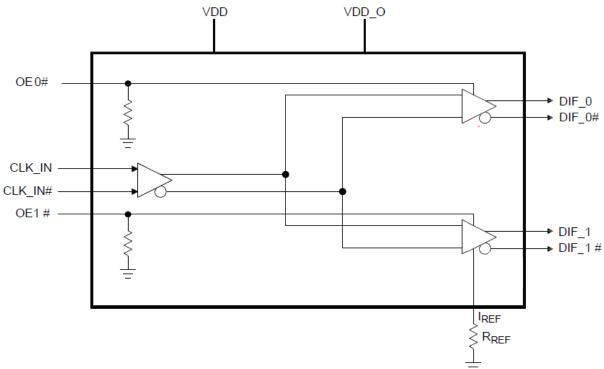

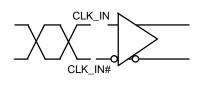

The NB3L202K is a differential 1:2 Clock fanout buffer with High-speed Current Steering Logic (HCSL) outputs. Inputs can directly accept differential LVPECL, LVDS, and HCSL signals. Single-ended LVPECL, HCSL, LVCMOS, or LVTTL levels are accepted with a proper external Vth reference supply per Figures 4 and 6. The input signal will be translated to HCSL and provides two identical copies operating up to 350 MHz.

The NB3L202K is optimized for ultra-low phase noise, propagation delay variation and low output-to-output skew, and is DB200H compliant. As such, system designers can take advantage of the NB3L202K's performance to distribute low skew clocks across the backplane or the motherboard making it ideal for Clock and Data distribution applications such as PCI Express, FBDIMM, Networking, Mobile Computing, Gigabit Ethernet, etc.

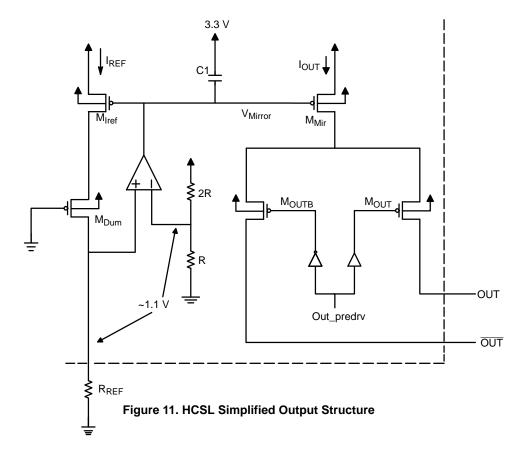

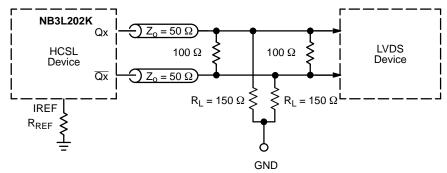

Output drive current is set by connecting a 475  $\Omega$  resistor from IREF (Pin 10) to GND per Figure 11. Outputs can also interface to LVDS receivers when terminated per Figure 12.

#### **Features**

- Maximum Input Clock Frequency > 350 MHz

- 2.5 V ±5% / 3.3 V ±10% Supply Voltage Operation

- 2 HCSL Outputs

- DB200H Compliant

- PCIe Gen 3, Gen 4 Compliant

- Individual OE Control Pin for Each Output

- 100 ps Max Output-to-Output Skew Performance

- 1 ns Typical Propagation Delay

- 500 ps Typical Rise and Fall Times

- 80 fs Maximum Additive RMS Phase Jitter

- -40°C to +85°C Ambient Operating Temperature

- QFN 16-pin Package, 3 mm x 3 mm

- These Devices are Pb-Free and are RoHS Compliant

#### **Typical Applications**

- PCI Express

- FBDIMM

- Mobile Computing

- Networking

- Gigabit Ethernet

#### ON Semiconductor®

www.onsemi.com

#### **MARKING DIAGRAM**

L

Υ

QFN16 3x3 CASE 485FM

NB3L202K = Specific Device Code

= Assembly Location

= Wafer Lot

= Year W

= Work Week

= Pb-Free Package

#### ORDERING INFORMATION

(Note: Microdot may be in either location)

See detailed ordering and shipping information page 13 of this data sheet.

Figure 1. Simplified Block Diagram

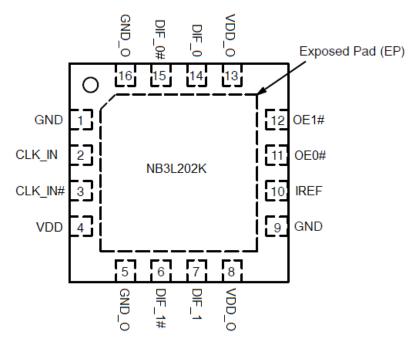

Figure 2. 16-Pin QFN Pinout (Top View)

## **Table 1. PIN DESCRIPTION**

| Pin Number | Pin Name       | I/O     | Description                                                                                                                                                                                                                                                                                                      |  |

|------------|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | GND            | Power   | Ground                                                                                                                                                                                                                                                                                                           |  |

| 2          | CLK_IN         | I, DIF  | Differential True input                                                                                                                                                                                                                                                                                          |  |

| 3          | CLK_IN#        | I, DIF  | Differential Complementary input                                                                                                                                                                                                                                                                                 |  |

| 4          | VDD            | Power   | Core power supply                                                                                                                                                                                                                                                                                                |  |

| 5          | GND_O          | Power   | Ground for outputs                                                                                                                                                                                                                                                                                               |  |

| 6          | DIF_1#         | O, DIF  | 0.7 V Differential Complementary Output                                                                                                                                                                                                                                                                          |  |

| 7          | DIF_1          | O, DIF  | 0.7 V Differential True Output                                                                                                                                                                                                                                                                                   |  |

| 8          | VDD_O          | Power   | Power supply for outputs                                                                                                                                                                                                                                                                                         |  |

| 9          | GND            | Power   | Ground                                                                                                                                                                                                                                                                                                           |  |

| 10         | IREF           | I       | A precision resistor is attached to this pin to set the differential output current. Use R <sub>REF</sub> = 475 $\Omega$ , 1% for 100 $\Omega$ trace, with 50 $\Omega$ termination. Use R <sub>REF</sub> = 412 $\Omega$ , 1% for 85 $\Omega$ trace, with 43 $\Omega$ termination.                                |  |

| 11         | OE0#           | I, SE   | LVTTL / LVCMOS active low input for enabling output DIF_0/0#. 0 enables outputs, 1 disables outputs. Internal pull down.                                                                                                                                                                                         |  |

| 12         | OE1#           | I, SE   | LVTTL / LVCMOS active low input for enabling output DIF_1/1#. 0 enables outputs, 1 disables outputs. Internal pull down.                                                                                                                                                                                         |  |

| 13         | VDD_O          | Power   | Power supply for outputs                                                                                                                                                                                                                                                                                         |  |

| 14         | DIF_0          | O, DIF  | 0.7 V Differential True Output                                                                                                                                                                                                                                                                                   |  |

| 15         | DIF_0#         | O, DIF  | 0.7 V Differential Complementary Output                                                                                                                                                                                                                                                                          |  |

| 16         | GND_O          | Power   | Ground for outputs                                                                                                                                                                                                                                                                                               |  |

| EP         | Exposed<br>Pad | Thermal | The Exposed Pad (EP) on the QFN16 package bottom is thermally connected to the die for improved heat transfer out of package. The exposed pad must be attached to a heat–sinking conduit. The pad is electrically connected to the die, and must be electrically and thermally connected to GND on the PC board. |  |

**Table 2. ATTRIBUTES**

| Characte                                               | Value                  |                      |  |  |

|--------------------------------------------------------|------------------------|----------------------|--|--|

| ESD Protection                                         | Human Body Model       | > 2000 V             |  |  |

| RPD – Pull–down Resistor                               |                        | 50 kΩ                |  |  |

| Moisture Sensitivity (Note 1)                          |                        | Level 1              |  |  |

| Flammability Rating                                    | Oxygen Index: 28 to 34 | UL 94 V-0 @ 0.125 in |  |  |

| Transistor Count                                       | 1344                   |                      |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test |                        |                      |  |  |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                                         | Min                 | Max        | Unit        |      |

|-------------------|-------------------------------------------------------------------|---------------------|------------|-------------|------|

| $V_{DD}$          | Core Supply Voltage                                               | Core Supply Voltage |            |             | V    |

| $V_{DD\_O}$       | I/O Supply Voltage                                                |                     |            | 4.6         | V    |

| V <sub>IH</sub>   | Input High Voltage (Note 2)                                       |                     | -          | 4.6         | V    |

| V <sub>IL</sub>   | Input Low Voltage                                                 | -0.5                | -          | V           |      |

| l <sub>OUT</sub>  | Maximum Output Current                                            | -                   | 24         | mA          |      |

| T <sub>A</sub>    | Operating Temperature Range                                       |                     | -40 to +85 | °C          |      |

| T <sub>stg</sub>  | Storage Temperature Range                                         |                     |            | -65 to +150 | °C   |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction–to–Ambient) (Note 3) 0 Ifpm 500 Ifpm |                     | 42<br>35   |             | °C/W |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case) (Note 3)                    |                     | 4          |             | °C/W |

| T <sub>sol</sub>  | Wave Solder                                                       | 265                 |            | °C          |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. Maximum V<sub>IH</sub> is not to exceed maximum V<sub>DD</sub>.

3. JEDEC standard multilayer board – 2S2P (2 signal, 2 power) with 8 filled thermal vias under exposed pad.

Table 4. DC CHARACTERISTICS  $V_{DD} = V_{DD\_O} = 3.3 \text{ V} \pm 10\%$  or 2.5 V  $\pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$

| Symbol                                 | Characteristics                                                                                              | Min            | Тур         | Max                        | Unit |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|-------------|----------------------------|------|

| POWER SUI                              | PPLY CURRENT                                                                                                 | •              | •           | •                          |      |

| $V_{DD}$                               | Core Power Supply Voltage $ V_{DD} = 3.3 \text{ V} \pm 10\% $ $ V_{DD} = 2.5 \text{ V} \pm 5\% $             | 2.970<br>2.375 | 3.3<br>2.5  | 3.630<br>2.625             | V    |

| $V_{DD\_O}$                            | Output Power Supply Voltage $V_{DD\_O}$ = 3.3 V ±10% $V_{DD\_O}$ = 2.5 V ±5%                                 | 2.970<br>2.375 | 3.3<br>2.5  | 3.630<br>2.625             | V    |

| I <sub>DD</sub> + I <sub>DD_O</sub>    | Total Power Supply Current (all outputs active @ 350 MHz, $R_{REF}$ = 412 $\Omega,$ $R_L$ = 43 $\Omega)$     |                | 80          | 110                        | mA   |

| I <sub>stdby</sub>                     | Standby Current, all OE pins de-asserted with inputs @ 350 MHz                                               |                | 50          | 65                         | mA   |

| l <sub>incr</sub>                      | Incremental output current for additional output; One OE Enabled                                             |                | 15          | 23                         | mA   |

| I <sub>stdby</sub> + I <sub>incr</sub> | Standby Current plus incremental current for one additional differential output;<br>One OE Enabled @ 350 MHz |                | 65          | 88                         | mA   |

| HCSL OUTP                              | UTS (Notes 4, 5)                                                                                             |                |             |                            |      |

| V <sub>OH</sub>                        | Output HIGH Voltage                                                                                          | 660            |             | 850                        | mV   |

| V <sub>OL</sub>                        | Output LOW Voltage                                                                                           | -150           |             |                            | mV   |

| V <sub>OUT</sub>                       | Output Swing (Single-Ended)<br>Output Swing (Differential)                                                   | 400<br>800     | 750<br>1500 |                            | mV   |

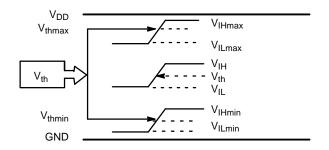

| DIFFERENT                              | IAL INPUT DRIVEN SINGLE-ENDED (Note 6) (Figures 4 and 6)                                                     | •              | •           |                            |      |

| V <sub>IH</sub>                        | CLK_IN/CLK_IN# Single-ended Input HIGH Voltage                                                               | 0.5            |             | $V_{DD}$                   | V    |

| $V_{IL}$                               | CLK_IN/CLK_IN# Single-ended Input LOW Voltage                                                                | GND            |             | V <sub>IH</sub> – 0.3      | V    |

| $V_{th}$                               | Input Threshold Reference Voltage Range (Note 7)                                                             | 0.25           |             | V <sub>DD</sub> – 1.0      | V    |

| V <sub>ISE</sub>                       | Single-ended Input Voltage (V <sub>IH</sub> – V <sub>IL</sub> )                                              | 0.5            |             | Vdd                        | V    |

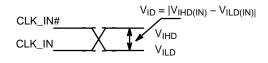

| DIFFERENT                              | IAL INPUTS DRIVEN DIFFERENTIALLY (Note 8) (Figures 5 and 7)                                                  |                |             |                            |      |

| $V_{IHD}$                              | Differential Input HIGH Voltage                                                                              | 0.5            |             | V <sub>DD</sub> – 0.85     | V    |

| $V_{ILD}$                              | Differential Input LOW Voltage                                                                               | 0              |             | V <sub>IHD</sub> –<br>0.25 | V    |

| V <sub>ID</sub>                        | Differential Input Voltage (V <sub>IHD</sub> - V <sub>ILD</sub> )                                            | 0.25           |             | 1.3                        | V    |

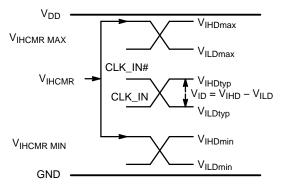

| $V_{IHCMR}$                            | Input Common Mode Range (Differential Configuration) (Note 9) (Figure 8)                                     | 0.5            |             | V <sub>DD</sub> – 0.85     | V    |

| I <sub>IL</sub>                        | Input Leakage Current 0 < V <sub>IN</sub> < V <sub>DD</sub> (Note 10)                                        | -5             |             | 5                          | μΑ   |

| _VTTL / LVC                            | MOS INPUTS (OEx#)                                                                                            |                |             | •                          |      |

| V <sub>IH</sub>                        | Input HIGH Voltage                                                                                           | 2.0            |             | V <sub>DD</sub> + 0.3      | V    |

| V <sub>IL</sub>                        | Input LOW Voltage                                                                                            | -0.3           |             | 0.8                        | V    |

| I <sub>IL</sub>                        | Input LOW Current (V <sub>IN</sub> = GND)                                                                    | -10            |             | +10                        | μΑ   |

| I <sub>IH</sub>                        | Input HIGH Current (V <sub>IN</sub> = V <sub>DD</sub> )                                                      |                |             | 100                        | μΑ   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics for the listed test conditions.

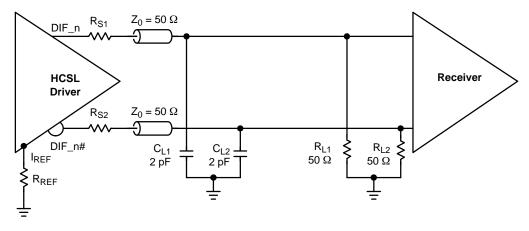

4. Test configuration is R<sub>S</sub> = 33.2 Ω, R<sub>L</sub> = 49.9, C<sub>L</sub> = 2 pF, R<sub>REF</sub> = 475 Ω.

5. Measurement taken from Single–Ended waveform unless specified otherwise.

6. V<sub>IH</sub>, V<sub>IL</sub>, V<sub>th</sub> and V<sub>ISE</sub> parameters must be complied with simultaneously.

7. V<sub>th</sub> is applied to the complementary input when operating in single–ended mode.

- V<sub>IHD</sub>, V<sub>ILD</sub>, V<sub>ID</sub> and V<sub>CMR</sub> parameters must be complied with simultaneously.

The common mode voltage is defined as V<sub>IH</sub>.

- 10. Does not include inputs with pulldown resistors.

Table 5. AC TIMING CHARACTERISTICS  $V_{DD} = V_{DD}$  O = 3.3 V ±10% or 2.5 V ±5%,  $T_A = -40$ °C to 85°C (Note 15)

| Symbol                               | Characteristics                                                                                                                             | Min  | Тур | Max                     | Unit   |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------------------------|--------|

| F <sub>max</sub>                     | Maximum Input Frequency                                                                                                                     | 350  |     |                         | MHz    |

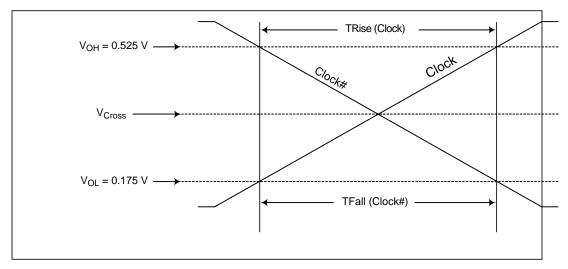

| T <sub>rise</sub> /T <sub>fall</sub> | Rise Time / Fall Time (Notes 13, 17 and 33) (Figure 13)                                                                                     | 175  | 500 | 700                     | ps     |

| Output Slew Rate                     | Output Slew Rate (Notes 13 and 17)                                                                                                          | 0.5  |     | 2.0                     | V/ns   |

| $\Delta T_{rise}/\Delta T_{fall}$    | Rise/Fall Time Variation (Notes 17 and 26)                                                                                                  |      |     | 125                     | ps     |

| Slew Rate Matching                   | (Notes 18, 27 and 28)                                                                                                                       |      |     | 20%                     |        |

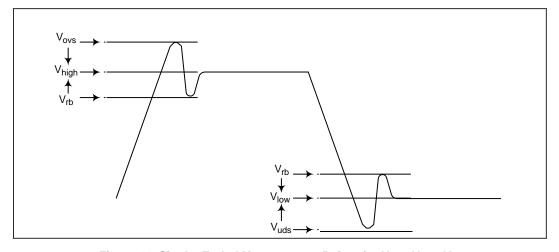

| $V_{high}$                           | Voltage High (Notes 17, and 20) (Figure 14)                                                                                                 | 660  | 700 | 850                     | mV     |

| V <sub>low</sub>                     | Voltage Low (Notes 17, and 21) (Figure 14)                                                                                                  | -150 | 0   | +150                    | mV     |

| Input Slew Rate                      | (Note 29 and 32)                                                                                                                            | 0.35 |     |                         | V/ns   |

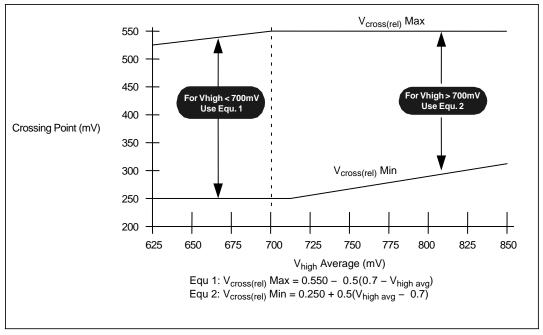

| V <sub>cross</sub> absolute          | Absolute Crossing Point Voltages (Notes 12, 17 and 24) Relative Crossing Point Voltages can be calculated (Notes 16, 17 and 24) (Figure 16) | 250  |     | 550                     | mV     |

| Total ΔV <sub>cross</sub>            | Total Variation of Vcross Over All Edges (Notes 17 and 25)                                                                                  |      |     | 140                     | mV     |

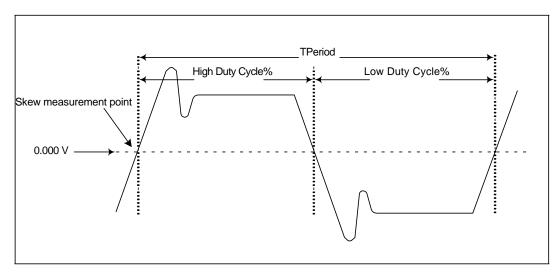

| Duty Cycle                           | (Note 18) (Figure 15)                                                                                                                       | 45   |     | 55                      | %      |

| V <sub>ovs</sub>                     | Maximum Voltage (Overshoot) (Notes 17 and 22) (Figure 14)                                                                                   |      |     | V <sub>high</sub> + 0.3 | V      |

| V <sub>uds</sub>                     | Maximum Voltage (Undershoot) (Notes 17 and 23) (Figure 14)                                                                                  |      |     | V <sub>low</sub> – 0.3  | V      |

| $V_{rb}$                             | Ringback Voltage (Note 17) (Figure 14)                                                                                                      | 0.2  |     | N/A                     | V      |

| T <sub>oe_lat</sub>                  | OE Latency (Note 11)                                                                                                                        | 4    | 6   | 12                      | Cycles |

| t <sub>pd</sub>                      | Input-to-Output Delay CLK_IN, DIF_[1:0] (Note 31)                                                                                           | 0.6  | 1.0 | 1.4                     | ns     |

| tskew                                | Output-to-Output Skew across 2 outputs DIF_[1:0] (Notes 30 and 31)                                                                          | 0    | 5.0 | 20                      | ps     |

| tjitterφ                             | Additive RMS Phase Jitter $f_{carrier}$ = 156.25 MHz, 12 kHz – 20 MHz Integrated Range                                                      |      | 46  | 80                      | fs     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 11. Time from deassertion until outputs are >200 mV.

- 12. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLK#.

- 13. Measured from  $V_{OL} = 0.175 \text{ V}$  to  $V_{OH} = 0.525 \text{ V}$ . Only valid for Rising Clock and Falling Clock#.

- 14. This measurement refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing

- 15. Test configuration is  $R_S$  = 33.2  $\Omega$ ,  $R_P$  = 49.9,  $C_L$  = 2 pF,  $R_{REF}$  = 475  $\Omega$ .

- 16. Vcross(rel) Min and Max are derived using the following, Vcross(rel) Min = 0.250 + 0.5 (Vhigh avg 0.700). Vcross(rel) Max = 0.550 0.5 (0.700 – V<sub>high avg</sub>), (see Figure 16 for further clarification). 17. Measurement taken from Single Ended waveform.

- 18. Measurement taken from differential waveform.

- 19. Unless otherwise noted, all specifications in this table apply to all frequencies.

- 20. V<sub>high</sub> is defined as the statistical average High value as obtained by using the Oscilloscope V<sub>high</sub> Math function. 21. V<sub>low</sub> is defined as the statistical average Low value as obtained by using the Oscilloscope V<sub>low</sub> Math function.

- 22. Overshoot is defined as the absolute value of the maximum voltage.

- 23. Undershoot is defined as the absolute value of the minimum voltage.

- 24. The crossing point must meet the absolute and relative crossing point specifications simultaneously.

- 25. \( \Delta \text{Vcross} \) is defined as the total variation of all crossing voltages of Rising CLOCK and Falling CLOCK#. This is the maximum allowed variance in Vcross for any particular system.

- 26. Measured with oscilloscope, averaging off, using min max statistics. Variation is the delta between min and max.

- 27. Matching applies to rising edge rate for clock and falling edge rate for Clock#. It is measured using a ±75 mV window centered on the average crosspoint where clock rising meets Clock# falling. The median crosspoint is used to calculate the voltage threshold the oscilloscope is to use for the edge rate calculations.

- 28. Slew Rate matching is derived using the following, 2 \*  $(T_{rise} T_{fall}) / (T_{rise} + T_{fall})$ . 29. Input slew rate is based on single ended measurement. This is the minimum input slew rate at which the NB3L202K devices are guaranteed to meet all performance specifications.

- 30. Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

- 31. Measured from differential cross-point to differential cross-point with scope averaging on to find mean value.

- 32. The differential input clock is expected to be sourced from a high performance clock oscillator.

- 33. Measured at 3.3  $\dot{V}$   $\pm$  10% with typical HCSL input levels.

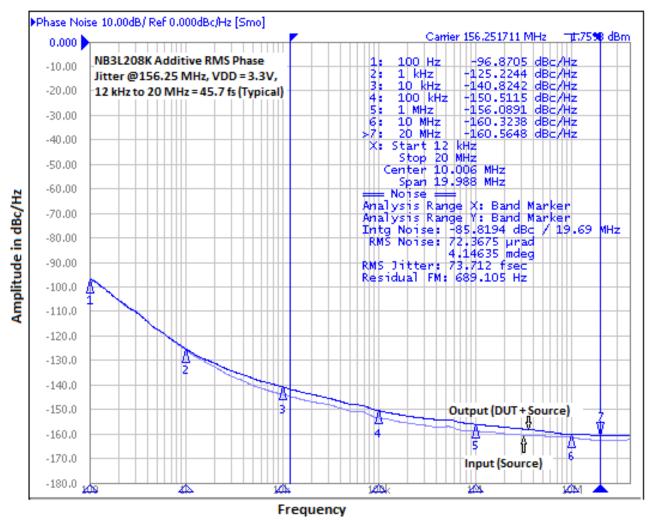

Figure 3. Typical Phase Noise Plot at f<sub>carrier</sub> = 156.25 MHz at an Operating Voltage of 3.3 V, Room Temperature

The above phase noise data was captured using Agilent E5052A/B. The data displays the input phase noise and output phase noise used to calculate the additive phase jitter at a specified integration range. The additive RMS phase jitter contributed by the device (integrated between 12 kHz and 20 MHz) is 45.7 fs.

The additive RMS phase jitter performance of the fanout buffer is highly dependent on the phase noise of the input source. To obtain the most accurate additive phase noise measurement, it is vital that the source phase noise be notably lower than that of the DUT. If the phase noise of the source is similar or greater than the device under test output, the source noise will dominate the additive phase jitter calculation and lead to an artificially low result for the additive phase noise measurement within the integration range.

Additive RMS phase jitter =

$$\sqrt{\text{RMS phase jitter of output}^2 - \text{RMS phase jitter of input}^2}$$

$45.7 \text{ fs} = \sqrt{73.7 \text{ fs}^2 - 57.8 \text{ fs}^2}$

#### Table 6. ELECTRICAL CHARACTERISTICS - PHASE JITTER PARAMETERS

(V<sub>DD</sub> = V<sub>DD\_O</sub> = 3.3 V  $\pm 10\%$  or 2.5 V  $\pm 5\%$ , T<sub>A</sub> =  $-40^{\circ}$ C to  $85^{\circ}$ C)

| Symbol                  | Parameter             | Conditions (Notes 34 and 39)                                                          | Min | Тур  | Max | Unit        |

|-------------------------|-----------------------|---------------------------------------------------------------------------------------|-----|------|-----|-------------|

| t <sub>jphPCleG1</sub>  |                       | PCIe Gen 1 (Notes 35 and 36)                                                          |     |      | 10  | ps (p-p)    |

|                         |                       | PCIe Gen 2 Lo Band<br>10 kHz < f < 1.5 MHz (Notes 35 and 38)                          |     |      | 0.3 | ps<br>(rms) |

| <sup>t</sup> jphPCleG2  |                       | PCIe Gen 2 High Band<br>1.5 MHz < f < Nyquist (50 MHz)<br>(Notes 35 and 38)           |     |      | 0.7 | ps<br>(rms) |

| t <sub>j</sub> PCIeG3   |                       | PCIe Gen 3<br>(PLL BW= 2-4 MHz or 2-5 MHz, CDR = 10 MHz)<br>(Notes 35 and 38)         |     | 0.07 | 0.4 | ps          |

| t <sub>j</sub> PCIeG4   | Additive Phase Jitter | PCIe Gen 4<br>(PLL BW= 2-4 MHz or 2-5 MHz, CDR = 10 MHz)<br>(Notes 35 and 38)         |     | 0.07 | 0.4 | ps          |

|                         |                       | QPI & SMI<br>(100.00 MHz or 133.33 MHz, 4.8 Gb/s,<br>6.4 Gb/s 12UI) (Notes 37 and 38) |     |      | 0.3 | ps<br>(rms) |

| t <sub>jphQPI_SMI</sub> |                       | QPI & SMI<br>(100.00 MHz, 8.0 Gb/s, 12UI) (Notes 37 and 38)                           |     |      | 0.1 | ps<br>(rms) |

|                         |                       | QPI & SMI<br>(100.00 MHz, 9.6 Gb/s, 12UI) (Notes 37 and 38)                           |     |      | 0.1 | ps<br>(rms) |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 34. Applies to all outputs.

<sup>35.</sup> See http://www.pcisig.com for complete specs

<sup>36.</sup> Sample size of at least 100K cycles. This figures extrapolates to 108 ps pk-pk @ 1M cycles for a BER of 1-12.

<sup>37.</sup> Calculated from Intel–supplied Clock Jitter Tool v 1.6.3.

38. For RMS figures, additive jitter is calculated by solving the following equation: (Additive jitter)<sup>2</sup> = (total jitter)<sup>2</sup> - (input jitter)<sup>2</sup>

<sup>39.</sup> Guaranteed by design and characterization, not tested in production

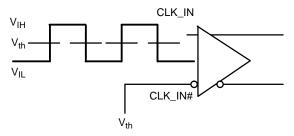

Figure 4. Differential Input Driven Single–Ended

Figure 5. Differential Inputs Driven Differentially

Figure 6. V<sub>th</sub> Diagram

Figure 7. Differential Inputs Driven Differentially

Figure 8. V<sub>IHCMR</sub> Diagram

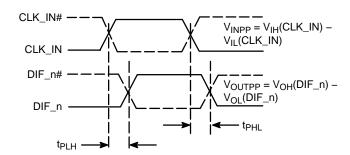

Figure 9. AC Reference Measurement

- A. Connect 475  $\Omega$  resistor RREF from IREF pin to GND.

- **B**.  $R_{S1}$ ,  $R_{S2}$ : 33  $\Omega$  for Test and Evaluation. Select to Minimizing Ringing.

- $\textbf{C}. \ C_{L1}, \ C_{L2} \\ \vdots \ \text{Receiver Input Simulation (for test only not added to application circuit.}$

- ${\bf D}.$   ${\bf R}_{\rm L1},$   ${\bf R}_{\rm L2}$  Termination and Load Resistors Located at Received Inputs.

Figure 10. Typical Termination Configuration for Output Driver and Device Evaluation

Figure 12. HCSL Interface Termination to LVDS

## **MEASUREMENT POINTS FOR DIFFERENTIAL**

Figure 13. Single-Ended Measurement Points for Trise, Tfall

Figure 14. Single–Ended Measurement Points for  $V_{\rm ovs},\,V_{\rm uds},\,V_{\rm rb}$

Figure 15. Differential (CLOCK - CLOCK#) Measurement Points (Tperiod, Duty Cycle)

Figure 16. V<sub>cross</sub> Range Clarification (Note 40)

40. The picture above illustrates the effect of  $V_{high}$  above and below 700 mV on the  $V_{cross}$  range. The purpose of this is to prevent a 250 mV  $V_{cross}$  with an 850 mV  $V_{high}$ . In addition, this prevents the case of a 550 mV  $V_{cross}$  with a 660 mV  $V_{high}$ . The actual specification for  $V_{cross}$  is dependent upon the measured amplitude of  $V_{high}$ .

#### **Signal and Feature Operation**

Table 7. OE# FUNCTIONALITY (Notes 41, 42 and 43)

| CLK_IN / CLK_IN# | OE# (Pin) | DIF     | DIF#    | Notes |

|------------------|-----------|---------|---------|-------|

| Running          | 1         | Low     | Low     | 41    |

| Running          | 0         | Running | Running |       |

| Not Running      | х         | х       | х       |       |

<sup>41.</sup> The outputs are tri-stated, but the termination networks pull them low

#### OE# Assertion (Transition from '1' to '0')

All differential outputs that were tri–stated (low due to termination pull down) will resume normal operation in a glitch free manner. The latency from the assertion to active outputs is 4 - 12 DIF clock periods.

Note: Input clock must remain running for a minimum of 12 clock cycles.

#### OE# De-Assertion (Transition from '0' to '1')

The maximum latency from the de-assertion to tristated (low due to termination pull down) outputs is 12 DIF clock periods.

Table 8. NB3L202K RESISTIVE LUMPED TEST LOADS FOR DIFFERENTIAL CLOCKS

| Board Target Trace/Term Z                          | Reference R, Iref = VDD/(3*R <sub>REF</sub> )            | Output Current                         | V <sub>OH</sub> @ Z | Rs         | Rp         |

|----------------------------------------------------|----------------------------------------------------------|----------------------------------------|---------------------|------------|------------|

| 100 $\Omega$ Differential 50 $\Omega$ Single–Ended | $R_{REF}$ = 475 $\Omega$ 1%, $I_{REF}$ = 2.32 mA         | I <sub>OH</sub> = 6 * I <sub>REF</sub> | 0.7 V @ 50          | 33 Ω<br>5% | 50 Ω<br>5% |

| 85 $\Omega$ Differential 43 $\Omega$ Single–Ended  | $R_{REF} = 412 \Omega, 1\%,$ $I_{REF} = 2.67 \text{ mA}$ | I <sub>OH</sub> = 6 * I <sub>REF</sub> | 0.7V @ 43.2         | 27 Ω<br>5% | 43 Ω<br>5% |

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NB3L202KMNG   | QFN16<br>(Pb-Free) | 123 Units / Rail      |

| NB3L202KMNTXG | QFN16<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>42.</sup> OE# pins are asynchronous asserted-low signals.

<sup>43.</sup> Each OE# pin controls two pair of DIF outputs.

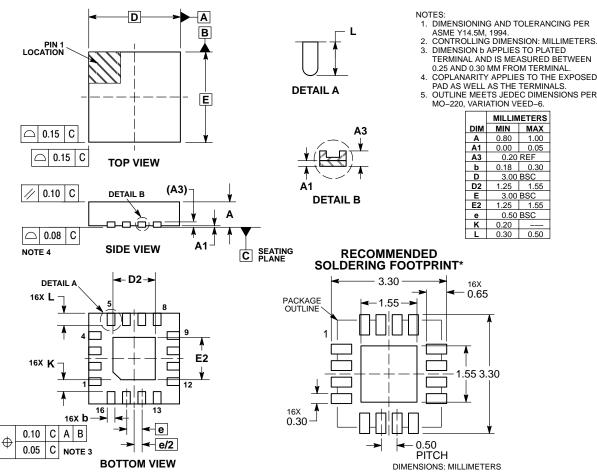

## PACKAGE DIMENSIONS

#### QFN16 3x3, 0.5P CASE 485FM ISSUE A

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative