# Power Factor Corrected Buck LED Driver

The NCL30002 is a switch mode power supply controller intended for low to medium power single stage power factor (PF) corrected LED Drivers. The device operates as a critical conduction mode (CrM) buck controller to regulate LED current at a high power factor for a specific line voltage range. The current limit threshold is tightly trimmed allowing open loop control techniques to reduce parts count while maintaining accurate current regulation and high power factor. CrM operation is particularly suited for LED applications as very high efficiency can be achieved even at low power levels. These are important in LED lighting to comply with regulatory requirements and meet overall system luminous efficacy requirements. In CrM, the switching frequency will vary with line and load. Switching losses are low as recovery losses in the output rectifier are negligible since the current goes to zero prior to reactivating the main MOSFET switch.

The device features a programmable on time limiter, zero current detect sense block, gate driver, trans–conductance error amplifier as well as all PWM control circuitry and protection functions required to implement a CrM switch mode power supply. Moreover, for high efficiency, the device features low startup current enabling fast, low loss charging of the  $V_{\rm CC}$  capacitor. The current sense protection threshold has been set at 485 mV to minimize power dissipation in the external sense resistor. To support the environmental operation range of Solid State Lighting, the device is specified across a wide junction temperature range of  $-40^{\circ}{\rm C}$  to  $125^{\circ}{\rm C}$ .

# Features

- Very Low 24 μA Typical Startup Current

- Cycle-by-Cycle Current Protection

- Tightly Trimmed Low Current Sense Threshold of 485 mV ±2%

- Low 2 mA Typical Operating Current

- Source 500 mA / Sink 800 mA Totem Pole Gate Driver

- Wide Operating Temperature Range

- Enable Function and Overvoltage Protection

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- LED Driver Power Supplies

- LED Based Bulbs

- Commercial and Residential LED Fixtures

# ON Semiconductor®

http://onsemi.com

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

## **PIN CONNECTION**

# **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCL30002DR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

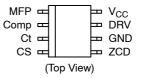

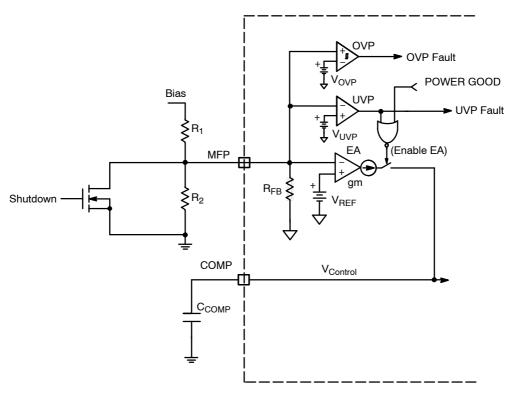

Figure 1. Block Diagram

# **Table 1. PIN FUNCTION DESCRIPTION**

| Pin | Name                                                                                                                                                                                                                                                                 | Function                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | The multi-function pin is connected to the internal error amplifier. By pulling this pin below the V <sub>uvp</sub> threshold, controller is disabled. In addition, this pin also has an over voltage comparator which will disable the controller event of a fault. |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 2   | COMP                                                                                                                                                                                                                                                                 | The COMP pin is the output of the internal error amplifier. A compensation network connected between this pin and ground sets the loop bandwidth.                                                                                                                                                                                                         |  |  |  |

| 3   | Ct                                                                                                                                                                                                                                                                   | The $C_t$ pin sources a regulated current to charge an external timing capacitor. The PWM circuit controls the power switch on time by comparing the $C_t$ voltage to an internal voltage derived from $V_{Control}$ . The $C_T$ pin discharges the external timing capacitor at the end of the on time cycle.                                            |  |  |  |

| 4   | CS                                                                                                                                                                                                                                                                   | The CS input threshold is precisely trimmed to accurately sense the instantaneous switch current in the external MOSFET. This signal is conditioned by an internal leading edge blanking circuit. The current limit threshold is tightly trimmed for precise peak current control.                                                                        |  |  |  |

| 5   | ZCD                                                                                                                                                                                                                                                                  | The voltage of an auxiliary zero current detection winding is sensed at this pin. When the ZCD control block circuit detects that the winding current has gone to zero, a control signal is sent to the gate drive block to turn on the external MOSFET.                                                                                                  |  |  |  |

| 6   | GND                                                                                                                                                                                                                                                                  | This is the analog ground for the device. All bypassing components should be connected to the GND pin with a short trace length.                                                                                                                                                                                                                          |  |  |  |

| 7   | DRV                                                                                                                                                                                                                                                                  | The high current capability of the totem pole gate drive ( $\pm 0.5/-0.8$ A) makes it suitable to effectively drive high gate charge power MOSFETs. The driver stage provides both passive and active pull down circuits that force the output to a voltage less than the turn–on threshold voltage of the power MOSFET when $V_{CC(on)}$ is not reached. |  |  |  |

| 8   | V <sub>CC</sub>                                                                                                                                                                                                                                                      | This pin is the positive supply of the controller. The circuit starts to operate when $V_{CC}$ exceeds $V_{CC(on)}$ , nominally 12 V and turns off when $V_{CC}$ goes below $V_{CC(off)}$ , typically 9.5 V. After startup, the operating range is 10.2 V up to 20 V.                                                                                     |  |  |  |

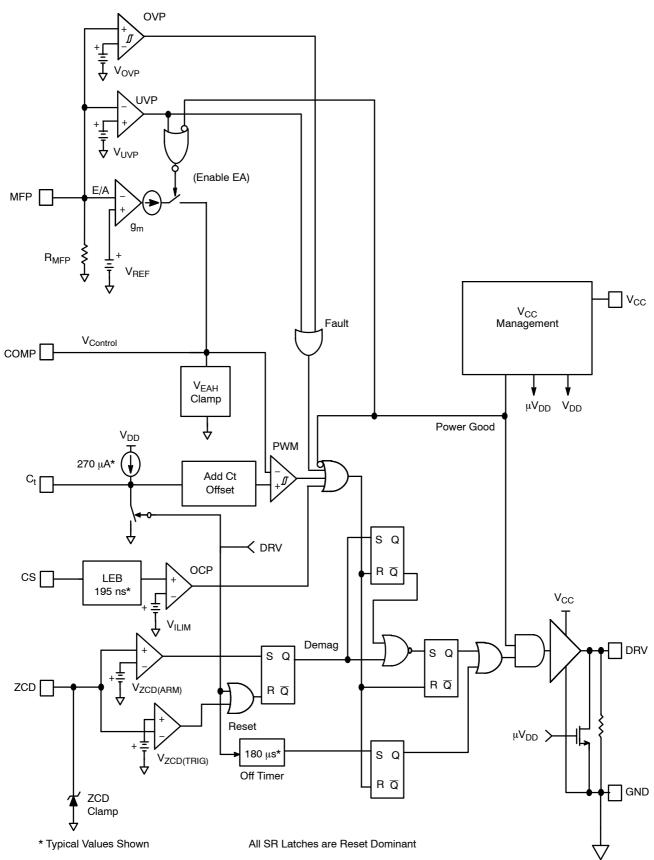

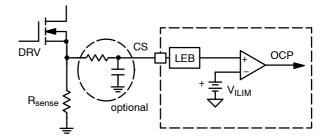

Figure 2. Simplified PFC Buck Application

## Overview

Figure 2 illustrates the basic NCL30002 architecture for a non-isolated low power high power factor LED driver. One of the notable features of this architecture is the open loop control. Notice that there is no direct measurement of the LED current. Tight peak current control coupled with line feed-forward compensation to vary the on-time allows for accurate LED drive current. Fortunately in the vast majority of LED bulb and luminaire applications, the LED forward voltage range is well bounded and the line voltage may be limited to one operating range. This is a huge advantage which makes the simplicity of open loop control possible.

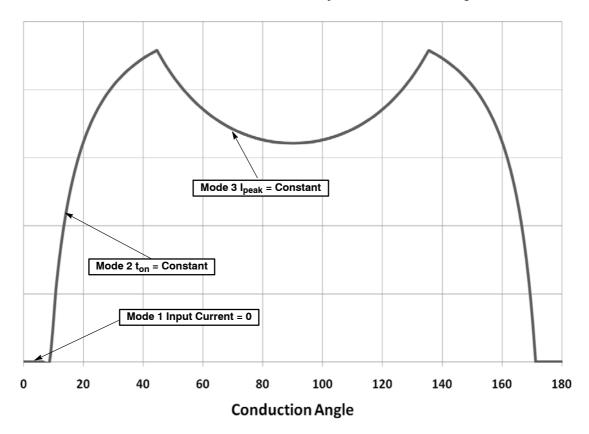

Buck switching on the low side eliminates a floating gate drive but references the LED to the HV rail. Buck converters only produce output when the input voltage exceeds the load voltage. Consequently, the input current goes to zero near the zero crossing of the line. The exact phase angle of this event depends on the LED string voltage and the line voltage. Unlike the boost PFC, the buck PFC has increased distortion near the zero crossing. However even with cross over distortion, high power factor and acceptable harmonics can be achieved.

**Table 2. MAXIMUM RATINGS**

| Rating                                                                                                                                                                                | Symbol                                                               | Value                   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|------|

| MFP Voltage                                                                                                                                                                           | $V_{MFP}$                                                            | -0.3 to 10              | V    |

| MFP Current                                                                                                                                                                           | I <sub>MFP</sub>                                                     | ±10                     | mA   |

| COMP Voltage                                                                                                                                                                          | V <sub>Control</sub>                                                 | -0.3 to 6.5             | V    |

| COMP Current                                                                                                                                                                          | I <sub>Control</sub>                                                 | –2 to 10                | mA   |

| Ct Voltage                                                                                                                                                                            | V <sub>Ct</sub>                                                      | -0.3 to 6               | V    |

| Ct Current                                                                                                                                                                            | I <sub>Ct</sub>                                                      | ±10                     | mA   |

| CS Voltage                                                                                                                                                                            | V <sub>CS</sub>                                                      | -0.3 to 6               | V    |

| CS Current                                                                                                                                                                            | I <sub>CS</sub>                                                      | ±10                     | mA   |

| ZCD Voltage                                                                                                                                                                           | $V_{ZCD}$                                                            | -0.3 to 10              | V    |

| ZCD Current                                                                                                                                                                           | I <sub>ZCD</sub>                                                     | ±10                     | mA   |

| DRV Voltage                                                                                                                                                                           | $V_{DRV}$                                                            | −0.3 to V <sub>CC</sub> | V    |

| DRV Sink Current                                                                                                                                                                      | I <sub>DRV(sink)</sub>                                               | 800                     | mA   |

| DRV Source Current                                                                                                                                                                    | I <sub>DRV(source)</sub>                                             | 500                     | mA   |

| Supply Voltage                                                                                                                                                                        | V <sub>CC</sub>                                                      | -0.3 to 20              | V    |

| Supply Current                                                                                                                                                                        | Icc                                                                  | ±20                     | mA   |

| Power Dissipation (TA = 70°C, 2.0 Oz Cu, 55 mm <sup>2</sup> Printed Circuit Copper Clad)                                                                                              | P <sub>D</sub>                                                       | 450                     | mW   |

| Thermal Resistance Junction-to-Ambient (2.0 Oz Cu, 55 mm² Printed Circuit Copper Clad) Junction-to-Air, Low conductivity PCB (Note 3) Junction-to-Air, High conductivity PCB (Note 4) | $egin{array}{c} R_{	hetaJA} \ R_{	hetaJA} \ R_{	hetaJA} \end{array}$ | 178<br>168<br>127       | °C/W |

| Operating Junction Temperature Range                                                                                                                                                  | TJ                                                                   | -40 to 125              | °C   |

| Maximum Junction Temperature                                                                                                                                                          | $T_{J(MAX)}$                                                         | 150                     | °C   |

| Storage Temperature Range                                                                                                                                                             | T <sub>STG</sub>                                                     | -65 to 150              | °C   |

| Lead Temperature (Soldering, 10 s)                                                                                                                                                    | TL                                                                   | 300                     | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. This device series contains ESD protection and exceeds the following tests:

- Pins 1– 8: Human Body Model 2000 V per JEDEC Standard JESD22–A114E.

Machine Model Method 200 V per JEDEC Standard JESD22–A115–A.

- 2. This device contains Latch–Up protection and exceeds ± 100 mA per JEDEC Standard JESD78.

- 3. As mounted on a 40x40x1.5 mm FR4 substrate with a single layer of 80 mm<sup>2</sup> of 2 oz copper traces and heat spreading area. As specified for a JEDEC 51 low conductivity test PCB. Test conditions were under natural convection or zero air flow.

- 4. As mounted on a 40 x 40 x 1.5 mm FR4 substrate with a single layer of 650 mm<sup>2</sup> of 2 oz copper traces and heat spreading area. As specified for a JEDEC 51 high conductivity test PCB. Test conditions were under natural convection or zero air flow.

$\begin{tabular}{lll} \textbf{Table 3. ELECTRICAL CHARACTERISTICS} \\ V_{MFP} = 2.4 \text{ V, } V_{Control} = 4 \text{ V, Ct} = 1 \text{ nF, } V_{CS} = 0 \text{ V, } V_{ZCD} = 0 \text{ V, } C_{DRV} = 1 \text{ nF, } V_{CC} = 12 \text{ V, unless otherwise specified (For typical values, } T_J = 25^{\circ}\text{C. For min/max values, } T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C, unless otherwise specified)} \\ \end{tabular}$

| Characteristic                                     | Test Conditions                                                                                                           | Symbol                                                                  | Min             | Тур              | Max              | Unit |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|------------------|------------------|------|

| STARTUP AND SUPPLY CIRCUITS                        |                                                                                                                           |                                                                         | I               | I                |                  |      |

| Startup Voltage Threshold                          | V <sub>CC</sub> Increasing                                                                                                | V <sub>CC(on)</sub>                                                     | 11              | 12               | 12.5             | V    |

| Minimum Operating Voltage                          | V <sub>CC</sub> Decreasing                                                                                                | V <sub>CC(off)</sub>                                                    | 8.8             | 9.5              | 10.2             | V    |

| Supply Voltage Hysteresis                          |                                                                                                                           | H <sub>UVLO</sub>                                                       | 2.2             | 2.5              | 2.8              | V    |

| Startup Current Consumption                        | 0 V < V <sub>CC</sub> < V <sub>CC(on)</sub> - 200 mV                                                                      | I <sub>cc(startup)</sub>                                                | -               | 24               | 35               | μΑ   |

| No Load Switching<br>Current Consumption           | $C_{DRV}$ = open, 70 kHz Switching, $V_{CS}$ = 2 V                                                                        | I <sub>cc1</sub>                                                        | -               | 1.4              | 1.7              | mA   |

| Switching Current Consumption                      | 70 kHz Switching, V <sub>CS</sub> = 2 V                                                                                   | I <sub>cc2</sub>                                                        | -               | 2.1              | 2.6              | mA   |

| Fault Condition Current Consumption                | No Switching, V <sub>MFP</sub> = 0 V                                                                                      | I <sub>cc(fault)</sub>                                                  | -               | 0.75             | 0.95             | mA   |

| OVERVOLTAGE AND UNDERVOLTAGE                       | E PROTECTION                                                                                                              |                                                                         |                 |                  |                  |      |

| Overvoltage Detect Threshold                       | V <sub>MFP</sub> = Increasing                                                                                             | V <sub>OVP</sub>                                                        | 2.5             | 2.67             | 2.85             | V    |

| Overvoltage Hysteresis                             |                                                                                                                           | V <sub>OVP(HYS)</sub>                                                   | 20              | 60               | 100              | mV   |

| Overvoltage Detect Threshold<br>Propagation Delay  | V <sub>MFP</sub> = 1 V to 3 V step,<br>V <sub>MFP</sub> = V <sub>OVP</sub> to V <sub>DRV</sub> = 10%                      | t <sub>OVP</sub>                                                        | _               | 500              | 800              | ns   |

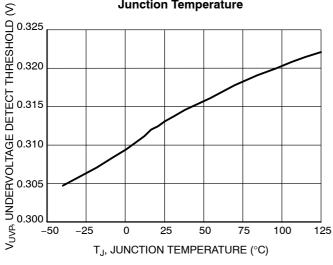

| Undervoltage Detect Threshold                      | V <sub>MFP</sub> = Decreasing                                                                                             | V <sub>UVP</sub>                                                        | 0.25            | 0.31             | 0.4              | V    |

| Undervoltage Detect Threshold<br>Propagation Delay | $V_{MFP} = 2 \text{ V to 0 V step},$<br>$V_{MFP} = V_{UVP} \text{ to V}_{DRV} = 10\%$                                     | t <sub>UVP</sub>                                                        | 80              | 200              | 320              | ns   |

| ERROR AMPLIFIER                                    |                                                                                                                           | •                                                                       |                 |                  |                  |      |

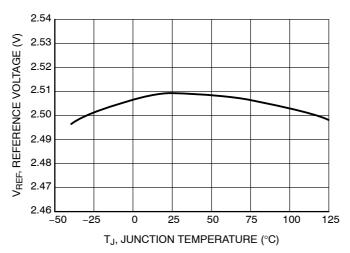

| Voltage Reference                                  | $T_{J} = 25^{\circ}C$ $T_{J} = -40^{\circ}C \text{ to } 125^{\circ}C$                                                     | V <sub>REF</sub>                                                        | 2.397<br>2.359  | 2.510<br>2.510   | 2.623<br>2.661   | V    |

| Voltage Reference Line Regulation                  | V <sub>CC(on)</sub> + 200 mV < V <sub>CC</sub> < 20 V                                                                     | V <sub>REF(line)</sub>                                                  | -10             | -                | 10               | mV   |

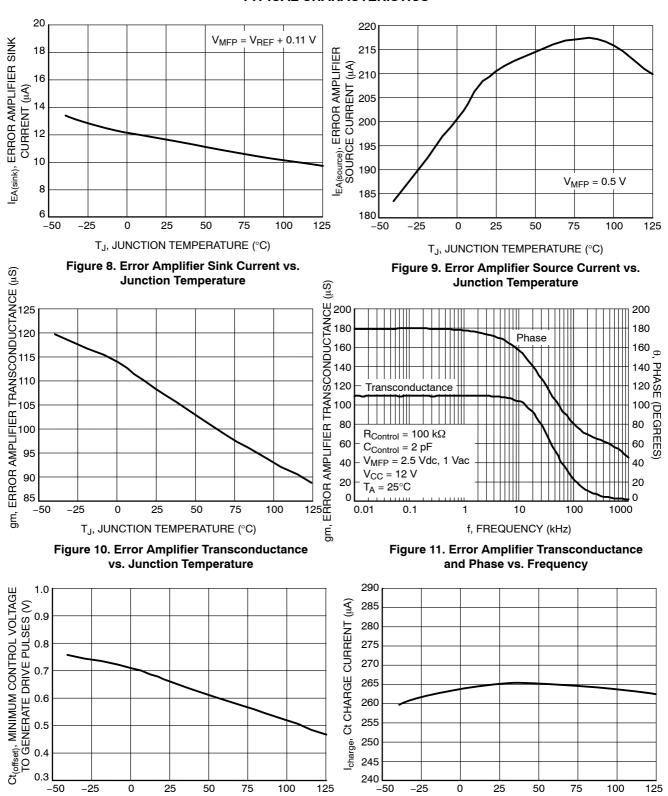

| Error Amplifier Current Capability                 | $V_{MFP} = V_{REF} + 0.11 \text{ V}$ $V_{MFP} = 1.08*V_{REF}$ $V_{MFP} = 0.5 \text{ V}$                                   | I <sub>EA(sink)</sub> I <sub>EA(sink)</sub> OVP I <sub>EA(source)</sub> | 6<br>10<br>–110 | 10<br>20<br>–210 | 20<br>30<br>–250 | μΑ   |

| Transconductance                                   | $V_{MFP} = V_{REF} \pm 100 \text{ mV}$ $T_{J} = 25^{\circ}\text{C}$ $T_{J} = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ | gm                                                                      | 90<br>70        | 110<br>110       | 120<br>135       | μS   |

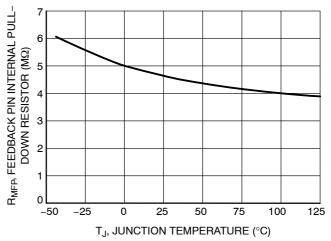

| Feedback Pin Internal Pull-Down<br>Resistor        | $V_{MFP} = V_{UVP}$ to $V_{REF}$                                                                                          | R <sub>MFP</sub>                                                        | 2               | 4.6              | 10               | ΜΩ   |

| Feedback Bias Current                              | V <sub>MFP</sub> = 2.5 V                                                                                                  | I <sub>MFP</sub>                                                        | 0.25            | 0.54             | 1.25             | μΑ   |

| Control Bias Current                               | V <sub>MFP</sub> = 0 V                                                                                                    | I <sub>Control</sub>                                                    | -1              | -                | 1                | μΑ   |

| Maximum Control Voltage                            | $I_{Control(pullup)} = 10 \mu A,$ $V_{MFP} = V_{REF}$                                                                     | V <sub>EAH</sub>                                                        | 5               | 5.5              | 6                | V    |

| Minimum Control Voltage to Generate Drive Pulses   | $V_{Control}$ = Decreasing until $V_{DRV}$ is low, $V_{Ct}$ = 0 V                                                         | Ct <sub>(offset)</sub>                                                  | 0.37            | 0.65             | 0.88             | V    |

| Control Voltage Range                              | V <sub>EAH</sub> - Ct <sub>(offset)</sub>                                                                                 | V <sub>EA(DIFF)</sub>                                                   | 4.5             | 4.9              | 5.3              | V    |

$\begin{tabular}{lll} \textbf{Table 3. ELECTRICAL CHARACTERISTICS} & (Continued) \\ V_{MFP} = 2.4 \text{ V, } V_{Control} = 4 \text{ V, Ct} = 1 \text{ nF, } V_{CS} = 0 \text{ V, } V_{ZCD} = 0 \text{ V, } C_{DRV} = 1 \text{ nF, } V_{CC} = 12 \text{ V, unless otherwise specified (For typical values, $T_J = 25^{\circ}$C. For min/max values, $T_J = -40^{\circ}$C to $125^{\circ}$C, unless otherwise specified) } \end{tabular}$

| Characteristic                                | Test Conditions                                                                                                                                                 | Symbol                             | Min            | Тур            | Max            | Unit |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|----------------|------|--|

| RAMP CONTROL                                  |                                                                                                                                                                 |                                    |                |                |                |      |  |

| Ct Peak Voltage                               | V <sub>COMP</sub> = open                                                                                                                                        | V <sub>Ct(MAX)</sub>               | 4.535          | 4.93           | 5.25           | V    |  |

| On Time Capacitor Charge Current              | $V_{COMP} = open$<br>$V_{Ct} = 0 V to V_{Ct(MAX)}$                                                                                                              | I <sub>charge</sub>                | 240            | 270            | 292            | μΑ   |  |

| Ct Capacitor Discharge Duration               | $V_{COMP}$ = open $V_{Ct} = V_{Ct(MAX)}$ -100 mV to 500 mV                                                                                                      | t <sub>Ct(discharge)</sub>         | -              | 50             | 150            | ns   |  |

| PWM Propagation Delay                         | $\begin{array}{c} \text{dV/dt} = 30 \text{ V/}\mu\text{s} \\ \text{V}_{Ct} = \text{V}_{Control} - \text{Ct}_{(offset)} \\ \text{to V}_{DRV} = 10\% \end{array}$ | t <sub>PWM</sub>                   | -              | 130            | 220            | ns   |  |

| ZERO CURRENT DETECTION                        |                                                                                                                                                                 | •                                  |                | •              |                |      |  |

| ZCD Arming Threshold                          | V <sub>ZCD</sub> = Increasing                                                                                                                                   | V <sub>ZCD(ARM)</sub>              | 1.25           | 1.4            | 1.55           | V    |  |

| ZCD Triggering Threshold                      | V <sub>ZCD</sub> = Decreasing                                                                                                                                   | V <sub>ZCD(TRIG)</sub>             | 0.6            | 0.7            | 0.83           | V    |  |

| ZCD Hysteresis                                |                                                                                                                                                                 | V <sub>ZCD(HYS)</sub>              | 500            | 700            | 900            | mV   |  |

| ZCD Bias Current                              | V <sub>ZCD</sub> = 5 V                                                                                                                                          | I <sub>ZCD</sub>                   | - 2            | -              | + 2            | μΑ   |  |

| Positive Clamp Voltage                        | I <sub>ZCD</sub> = 3 mA                                                                                                                                         | V <sub>CL(POS)</sub>               | 9.8            | 10             | 12             | V    |  |

| Negative Clamp Voltage                        | I <sub>ZCD</sub> = -2 mA                                                                                                                                        | V <sub>CL(NEG)</sub>               | -0.9           | -0.7           | -0.5           | V    |  |

| ZCD Propagation Delay                         | $V_{ZCD}$ = 2 V to 0 V ramp,<br>$dV/dt$ = 20 V/ $\mu$ s<br>$V_{ZCD}$ = V <sub>ZCD(TRIG)</sub> to V <sub>DRV</sub> = 90%                                         | t <sub>ZCD</sub>                   | -              | 100            | 170            | ns   |  |

| Minimum ZCD Pulse Width                       |                                                                                                                                                                 | t <sub>SYNC</sub>                  | _              | 70             | -              | ns   |  |

| Maximum Off Time in Absence of ZCD Transition | Falling V <sub>DRV</sub> = 10% to<br>Rising V <sub>DRV</sub> = 90%                                                                                              | t <sub>start</sub>                 | 75             | 165            | 300            | μs   |  |

| DRIVE                                         |                                                                                                                                                                 | •                                  |                | •              |                |      |  |

| Drive Resistance                              | I <sub>source</sub> = 100 mA<br>I <sub>sink</sub> = 100 mA                                                                                                      | R <sub>OH</sub><br>R <sub>OL</sub> | -              | 12<br>6        | 20<br>13       | Ω    |  |

| Rise Time                                     | 10% to 90%                                                                                                                                                      | t <sub>rise</sub>                  | -              | 35             | 80             | ns   |  |

| Fall Time                                     | 90% to 10%                                                                                                                                                      | t <sub>fall</sub>                  | -              | 25             | 70             | ns   |  |

| Drive Low Voltage                             | $V_{\rm CC}$ = $V_{\rm CC(on)}$ -200 mV,<br>$I_{\rm sink}$ = 10 mA                                                                                              | V <sub>out(start)</sub>            | -              | -              | 0.2            | V    |  |

| CURRENT SENSE                                 |                                                                                                                                                                 | •                                  |                |                |                |      |  |

| Current Sense Voltage Threshold               | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = -40°C to 125°C                                                                                                        | V <sub>ILIM</sub>                  | 0.475<br>0.470 | 0.485<br>0.485 | 0.495<br>0.500 | V    |  |

| Leading Edge Blanking Duration                | V <sub>CS</sub> = 2 V, V <sub>DRV</sub> = 90% to 10%                                                                                                            | t <sub>LEB</sub>                   | 100            | 195            | 350            | ns   |  |

| Overcurrent Detection Propagation Delay       | $dV/dt = 10 V/\mu s$ $V_{CS} = V_{ILIM} \text{ to } V_{DRV} = 10\%$                                                                                             | t <sub>CS</sub>                    | 40             | 100            | 170            | ns   |  |

| Current Sense Bias Current                    | V <sub>CS</sub> = 2 V                                                                                                                                           | I <sub>CS</sub>                    | -1             | -              | 1              | μΑ   |  |

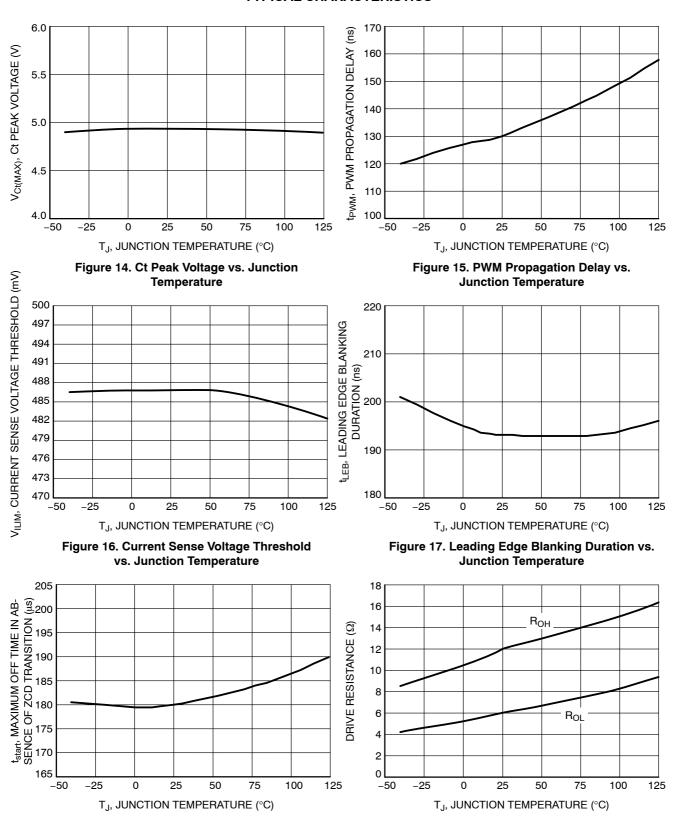

# TYPICAL CHARACTERISTICS

Figure 3. Overvoltage Detect Threshold vs. Junction Temperature

Figure 4. Overvoltage Hysteresis vs. Junction Temperature

Figure 5. Undervoltage Detect Threshold vs.

Junction Temperature

Figure 6. MFP Pin Internal Pull-Down Resistor vs. Junction Temperature

Figure 7. Reference Voltage vs. Junction Temperature

# **TYPICAL CHARACTERISTICS**

T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 12. Minimum Control Voltage to Generate

Drive Pulses vs. Junction Temperature

T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 13. On Time Capacitor Charge Current

vs. Junction Temperature

# TYPICAL CHARACTERISTICS

Figure 19. Drive Resistance vs. Junction

**Temperature**

Figure 18. Maximum Off Time in Absence of

**ZCD Transition vs. Junction Temperature**

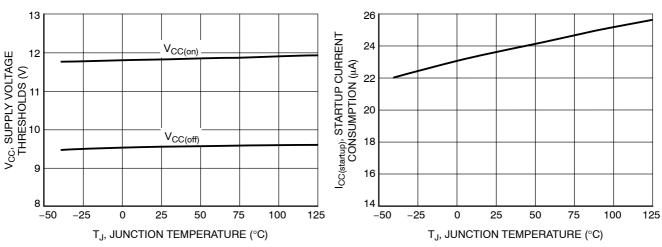

# **TYPICAL CHARACTERISTICS**

Figure 20. Supply Voltage Thresholds vs. Junction Temperature

Figure 21. Startup Current Consumption vs. Junction Temperature

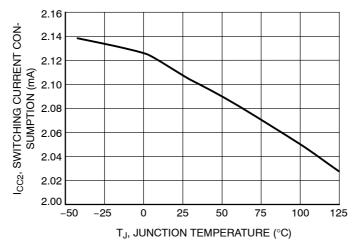

Figure 22. Switching Current Consumption vs. Junction Temperature

## THEORY OF OPERATION

High power factor, high efficiency, and small size are key parameters for LED drivers in the incandescent replacement market. The NCL30002 has all the features required to accomplish that is in a compact SOIC-8 package. Power factor is broadly defined as:

$$PF = \frac{P_{in}(avg)}{V_{in}(rms) \times I_{in}(rms)}$$

This differs from the classical definition where there is a phase angle difference between the input voltage and current. However, the underlying concept of optimizing power delivery by minimizing line current is the same. Ideally, current would be directly proportional to the voltage which is the case when the load is a resistor. Offline power converters are active devices which are not purely resistive, capacitive, or inductive often drawing distorted current waveforms from the power lines. This distortion reduces power factor by increasing input RMS current. Preregulators using boost converters are the most common method to correcting the distortion and making the offline power supply appear to be a resistor as far as the power line is concerned. Their performance is excellent achieving power factor greater than 0.99. Regrettably, this two stage approach negatively impacts efficiency and board area. Fortunately, power factors greater than 0.9 are acceptable in the general lighting market and in some applications like US Energystar™ Integral LED bulbs, the minimum acceptable power factor is 0.7. So a certain amount of distortion can be accepted while maintaining high power factor. This buck topology meets the requirements for PF greater than 0.9 and regulate LED current in a single power stage. Unlike the boost converter, the NCL30002 buck controller operates in several different modes over the line cycle.

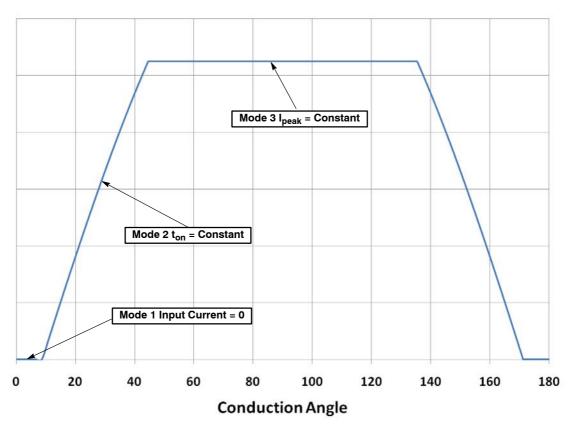

#### **Buck Modes**

- "Zero" Input Current (I<sub>in</sub>=0) Buck converters cannot deliver power when Vin is less than Vout. The "dead time" where no current flows around the zero crossing is dependent on the line voltage and the load voltage.

- Constant On-Time (T<sub>on</sub> = constant) This is the same as the boost converter. Constant T<sub>on</sub> forces the peak current to be proportional to the input voltage which is key to improved PF.

- 3. Constant Peak Current (I<sub>peak</sub> = constant) The NCL30002 limits the peak inductor and thus the LED current. In this region, the unique nature of the CrM buck means that the average output current is equal to half the peak current. Also the off time is fixed is this mode since the peak current and the output voltage are virtually constant.

In the example below (Figure 23) in spite of the distortion, the power factor is 0.97. The corresponding pre-filtered output current is shown in Figure 24.

Figure 23. Theoretical Average Input Current over one half line cycle (conduction angle)

Figure 24. Theoretical Average Output Current over one half line cycle (conduction angle)

An output capacitor filters the output current in the LED string. The dynamic LED resistance, line frequency, and the size of the filter capacitance determine the exact LED ripple.

The NCL30002 operates as a CrM controller. The controller draws very low currents while the Vcc filter capacitor charges to the start-up threshold. Since CrM operation is not clocked at a fixed frequency and depends on the state of the power circuit to initiate a new switching cycle, a kick start timer turns on the gate driver to start a new cycle. The kick start timer will do this anytime the driver is off for more than about 180 µsec as long as none of the protection circuits are disabling the gate driver output.

The NCL30002 (refer to the block diagram – Figure 1) is composed of 4 key functional blocks along with protection circuitry to ensure reliable operation of the controller.

- On-Time Control

- Zero Current Detection Control

- MOSFET Gate Driver

- Startup and V<sub>CC</sub> Management

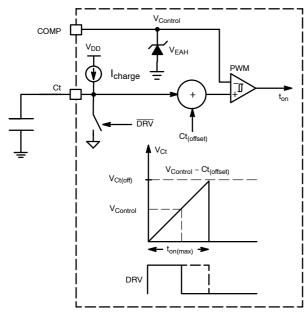

# **On Time Control**

The on–time control circuitry (Figure 25) consists of a precision current source which charges up an external capacitor  $(C_t)$  in a linear ramp. The voltage on  $C_t$  (after removing an internal offset) is compared to an external control voltage and the output of the comparator is used to turn off the output driver thus terminating the switching cycle. A signal from the driver is fed back to the on–time control block to discharge the  $C_t$  capacitor thus preparing the circuit for the start of the next switching cycle.

The state of  $V_{control}$  is determined by the external regulation loop. The range of on–time is determined by the charging slope of the  $C_t$  capacitor and is clamped at 4.93 V nominal. The  $C_t$  capacitor is sized to ensure that the required on–time is reached at maximum output power and the minimum input line voltage condition.

Figure 25. On Time Control

# **Off Time Sequence**

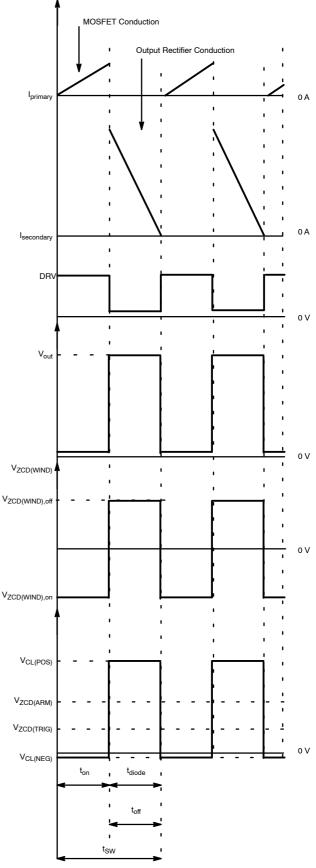

The off time is determined by the peak inductor current, the inductance and the output voltage. In mode 2, the off time is variable because the peak inductor current is not fixed. However in mode 3, the off time is constant since the peak current and the output voltage are both fixed. The auxiliary winding used to provide bias to the NCL30002 is also used to detect when the current has dropped to zero. This is illustrated in Figure 26.

Figure 26. Ideal CrM Waveforms with ZCD Winding

## **ZCD Detection Block**

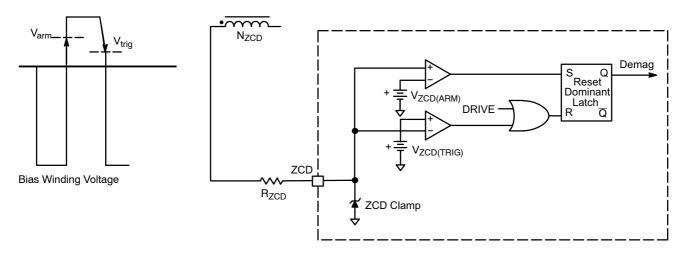

A dedicated circuit block is necessary to implement the zero current detection. The NCL30002 provides a separate input pin to signal the controller to turn the power switch back on just after inductor current reaches zero. When the output winding current reaches zero the winding voltage will reverse. Since all windings of the inductor reflect the same voltage characteristic this voltage reversal appears on the bias winding. Coupling the winding voltage to the ZCD input of the NCL30002 allows the controller to start the next switching cycle at the precise time. To avoid false triggering,

the ZCD input has a dual comparator input structure to arm the latch when the ZCD detect voltage rises above  $1.4~\rm V$  (nominal) thus setting the latch. When the voltage on ZCD falls below  $0.7~\rm V$  (nominal) a zero current event is detected and a signal is asserted which initiates the next switching cycle. This is illustrated in Figure 27. The input of the ZCD has an internal circuit which clamps the positive and negative voltage excursions on this pin. The current into or out of the ZCD pin must be limited to  $\pm 10~\rm mA$  with an external resistor.

Figure 27. ZCD Operation

At startup, there is no energy in the ZCD winding and no voltage signal to activate the ZCD comparators. To enable the controller to start under these conditions, an internal watchdog timer is provided which initiates a switching cycle in the event that the output drive has been off for more than  $180~\mu s$  (nominal).

The timer is deactivated only under an OVP or UVP fault condition which will be discussed in the next section.

# CS

The dedicated CS pin of the NCL30002 senses the current through the MOSFET switch and the output inductor. If the voltage of the CS pin exceeds  $V_{\rm ILIM}$ , the internal comparator will detect the event and turn off the MOSFET. The peak switch current is calculated using Equation 1:

$$I_{SW(peak)} = \frac{V_{ILIM}}{R_{sense}} \tag{eq. 1} \label{eq:sw}$$

To avoid false detection, the NCL30002 incorporates leading edge blanking circuit (LEB) which masks the CS signal for a nominal time of 190 ns. If required, an optional RC filter can be added between  $R_{\text{sense}}$  and CS to provide additional filtering. This is illustrated below.

Figure 28. CS Circuitry with Optional External RC Filter

# MFP Input

The multi-function pin connects to the inverting terminal of the transconductance amplifier, the undervoltage and overvoltage protection comparators. This allows this pin to perform several functions. To place the device in standby, the MFP pin should be pulled below the  $V_{uvp}$  threshold. This is illustrated in Figure 29. Additionally, raising the MFP pin above  $V_{ovp}$  will also suspend switching activity but not place the controller in the standby mode. This can be used implement overvoltage monitoring on the bias winding and add an additional layer of fault protection.

Figure 29. Multi-Function Pin Operation

The positive input of the transconductance amplifier is connected to a 2.51 V (nominal) reference. A filtered line feed-forward signal (see Figure 2) is connected to the negative input of the error amplifier and used to control the on-time of controller.

# **V<sub>CC</sub> Management**

The NCL30002 incorporates a supervisory circuitry to manage the startup and shutdown of the circuit. By managing the startup and keeping the initial startup current at less than 35  $\mu A$ , a startup resistor connected between the rectified ac line and  $V_{CC}$  charges the  $V_{CC}$  capacitor to  $V_{CC(on)}$ . Turn on of the device occurs when the startup voltage has exceeded 12 V (nominal) when the internal reference and switching logic are enabled. A UVLO comparator with a hysteresis of 2.5 V nominal gives ample time for the device to start switching and allow the bias from the auxiliary winding to supply  $V_{CC}$ .

# **Design Tool**

The NCL30002 implements a unique control method to achieve high power and superior current regulation even though the average current is not directly sensed. There are a number of design tradeoffs that can be made between peak switch current, inductor size, and desired power factor that can impact the current regulation accuracy, efficiency, and physical size. These tradeoffs can be made by adjusting the amount of line feed forward applied, selecting the amount of time where the controller is operating in mode 2 and 3, as well as factoring in the LED forward voltage range. To simplify the component selection process and allow the to interactively make these tradeoffs, ON Semiconductor has developed an EXCEL™ based Design Guide which allows step-by-step analysis. This tool is available at onsemi.com along with a supporting application note that illustrates a complete design and provides typical application performance.

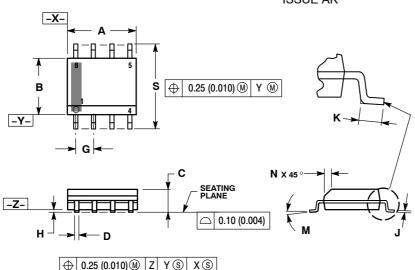

#### PACKAGE DIMENSIONS

# SOIC-8 NB CASE 751-07 **ISSUE AK**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B DO NOT INCLUDE

- MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR

- DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

751-01 THRU 751-06 ARE OBSOLETE. NEW

- STANDARD IS 751-07.

|     | MILLIN   | IETERS | INC       | IES   |  |

|-----|----------|--------|-----------|-------|--|

| DIM | MIN      | MAX    | MIN       | MAX   |  |

| Α   | 4.80     | 5.00   | 0.189     | 0.197 |  |

| В   | 3.80     | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35     | 1.75   | 0.053     | 0.069 |  |

| D   | 0.33     | 0.51   | 0.013     | 0.020 |  |

| G   | 1.27 BSC |        | 0.050 BSC |       |  |

| Н   | 0.10     | 0.25   | 0.004     | 0.010 |  |

| J   | 0.19     | 0.25   | 0.007     | 0.010 |  |

| K   | 0.40     | 1.27   | 0.016     | 0.050 |  |

| M   | 0 °      | 8 °    | 0 °       | 8 °   |  |

| N   | 0.25     | 0.50   | 0.010     | 0.020 |  |

| S   | 5.80     | 6.20   | 0.228     | 0.244 |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) . Solitude services are inject to make triangles without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative