# **3:1 High Speed USB Switch with Audio and MHL Capability**

The NCN1188 allows portable systems to share a single USB 2.0 or 3.0 receptacle to transmit and receive paired signals from three separate locations. All of the three differential channels are compliant to High Speed USB 2.0, Full Speed USB 1.1, Low Speed USB 1.0 and any generic UART protocol. The two dedicated high speed data paths also support Mobile High Definition Link (MHL) video up to resolutions of 1080i (2.25 Gbps) and 1080p (3 Gbps in Packed Pixel mode). The multi–purpose audio path is capable of passing signals with negative voltages as low as 2 V below ground and features shunt resistors to reduce Pop and Click noise in the audio system. The NCN1188 is housed in a space saving, ultra low profile 2.0 x 1.7 x 0.5 mm, 12 pins UQFN package.

#### Features

- High Bandwidth of 1.8 GHz

- V<sub>CC</sub> Operating Range from 2.7 V to 5.5 V

- V<sub>IS</sub> Signal from 0 V to 3.7 V for Data Transfer

- V<sub>IS</sub> Signal from –2 V to 2 V for Stereo Headphone Connection

- Audio Shunt resistor for Pop & Click Noise Reduction

- V<sub>IO</sub> Control Pins Compatible to 1.8V Interfaces

- Low Power Consumption of 23 µA

- Small UQFN 2.0 x 1.7 x 0.5 mm Package

- These Devices are Pb–Free and are RoHS Compliant **Typical Applications**

- USB 2.0 / 3.0 Micro-B Applications

- USB to HDMI Video Interfaces via MHL

- Features Phones and Smart Phones

- Digital Cameras

- Handset Media Players

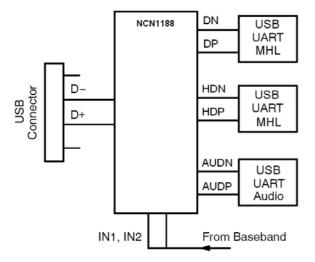

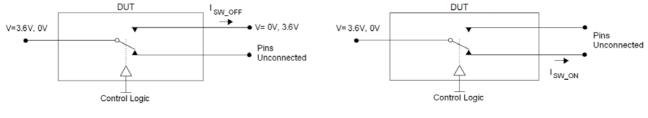

Figure 1. NCN1188 Typical Application Schematic

### **ON Semiconductor®**

http://onsemi.com

|   |                                   | MARKING<br>DIAGRAM |

|---|-----------------------------------|--------------------|

|   | UQFN12<br>MU SUFFIX<br>CASE 523AE | AGM<br>⊖ ■         |

| A | G = Specific Devic<br>= Date Code | ce Code            |

= Pb-Free Package

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCN1188MUTAG | UQFN12<br>(Pb-Free) | 3000 /<br>Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### NCN1188 TRUTH TABLE

| Function    | IN1 | IN2 | Shunt   |

|-------------|-----|-----|---------|

| Hi–Z        | 0   | 0   | Enable  |

| DN / DP     | 0   | 1   | Enable  |

| AUDN / AUDP | 1   | 0   | Disable |

| HDN / HDP   | 1   | 1   | Enable  |

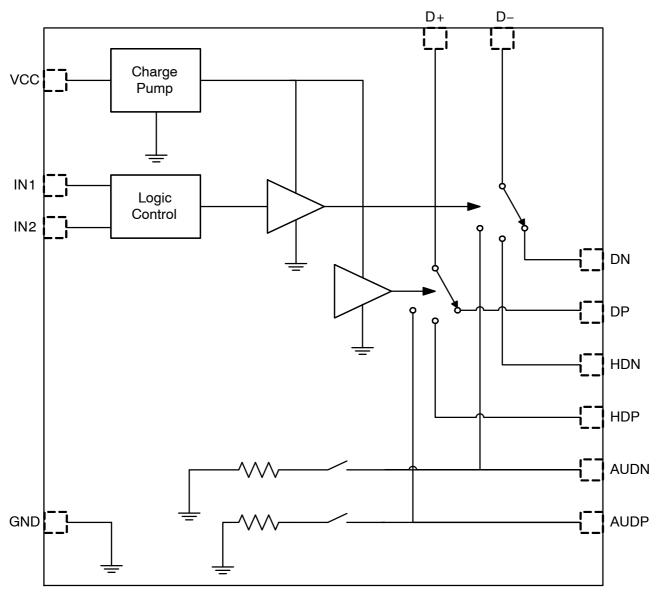

### SIMPLIFIED BLOCK DIAGRAM

Figure 2. Simplified Block Diagram

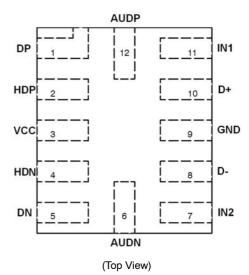

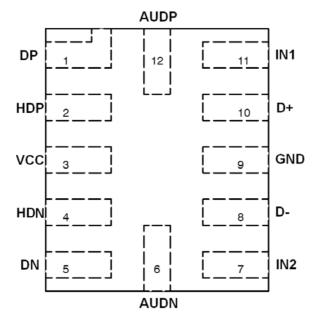

### **PIN DIAGRAM**

Figure 3. Pin Assignments (Top View)

#### PIN DESCRIPTION

| Name | Pin | Description                                                                                                                                                                                                                   |

|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP   | 1   | USB Positive Path. If active, this pin is connected to D+ pin.                                                                                                                                                                |

| HDP  | 2   | HD Positive Path. If active, this pin is connected to D+ pin.                                                                                                                                                                 |

| VCC  | 3   | <b>Analog Supply</b> . This pin is the analog and digital supply of the device. A 100 nF ceramic capacitor or larger must bypass this input to the ground. This capacitor should be placed as close a possible to this input. |

| HDN  | 4   | HD Negative Path. If active, this pin is connected to D- pin.                                                                                                                                                                 |

| DN   | 5   | USB Negative Path. If active, this pin is connected to D- pin.                                                                                                                                                                |

| AUDN | 6   | Audio N. If active, this pin is connected to D- pin.                                                                                                                                                                          |

| IN2  | 7   | Input Selection 2. Do not float this pin.                                                                                                                                                                                     |

| D-   | 8   | Negative data line. Must be connected to the D- pin of USB receptacle.                                                                                                                                                        |

| GND  | 9   | Ground Reference. Must be connected to the system ground.                                                                                                                                                                     |

| D+   | 10  | Positive data line. Must be connected to the D+ pin of USB receptacle.                                                                                                                                                        |

| IN1  | 11  | Input Selection 1. Do not float this pin.                                                                                                                                                                                     |

| AUDP | 12  | Audio P. If active, this pin is connected to D+ pin.                                                                                                                                                                          |

#### MAXIMUM RATINGS (Note 1)

| Rating                                                       | Symbol              | Value                         | Unit |

|--------------------------------------------------------------|---------------------|-------------------------------|------|

| Maximum Supply Voltage Range on VCC pin                      | V <sub>CCMAX</sub>  | – 0.3 to 6.0                  | V    |

| Maximum Analog Signal Voltage Range on DN, DP, HDN, HDP pins | VISMAX              | – 0.3 to 5.5                  | V    |

| Maximum Analog Signal Voltage Range on D+, D- pins           | V <sub>COMMAX</sub> | – 2.5 to 5.5                  | V    |

| Maximum Analog Signal Voltage Range on IN1, IN2 pins         | V <sub>IOMAX</sub>  | –0.3 to V <sub>CC</sub> + 0.3 | V    |

| Maximum Analog Signal Voltage Range on AUDN, AUDP pins       | V <sub>AUDMAX</sub> | –2.5 to V <sub>CC</sub> + 0.3 | V    |

| Latch up Current (Note 2)                                    | I <sub>LU</sub>     | ±100                          | mA   |

| Human Body Model (HBM) ESD Rating (Note 3)                   | ESD HBM             | 4000                          | V    |

| Machine Model (MM) ESD Rating (Note 3)                       | ESD MM              | 100                           | V    |

| Maximum Junction Temperature                                 | T <sub>JMAX</sub>   | +150                          | °C   |

| Storage Temperature Range                                    | T <sub>STG</sub>    | –55 to + 150                  | °C   |

| Moisture Sensitivity (Note 4)                                | MSL                 | Level 1                       |      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = 25°C.

2. Latch up Current Maximum Rating: ±100 mA per JEDEC standard: JESD78.

This device series contains ESD protection and passes the following tests: Human Body Model (HBM) ±4.0 kV per JEDEC standard: JESD22–A114 for all pins. Machine Model (MM) ±100 V per JEDEC standard: JESD22–A115 for all pins.

4. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                            | Conditions      | Min | Тур | Max | Unit |

|-----------------|--------------------------------------|-----------------|-----|-----|-----|------|

| VOLTAGE         | RANGES                               |                 |     |     |     |      |

| V <sub>CC</sub> | VCC pin operating range              |                 | 2.7 | -   | 5.5 | V    |

| V <sub>IS</sub> | Analog Signal Voltage range (Note 5) | High Speed Data | 0   | -   | 3.7 | V    |

Audio

-2.0

2.0

#### **TEMPERATURE RANGES**

| T <sub>A</sub> | Operating Ambient Temperature  | -40 | - | 85  | °C |

|----------------|--------------------------------|-----|---|-----|----|

| TJ             | Operating Junction Temperature | -40 | - | 125 | °C |

5. If the audio channel is not in use, it is recommended that no signals are applied on the audio inputs AUDN and AUDP

#### **ELECTRICAL CHARACTERISTICS**

Min and Max limits apply for T<sub>A</sub> from  $-40^{\circ}$ C to  $+85^{\circ}$ C (unless otherwise noted). Typical values are referenced to V<sub>CC</sub> = 3.6 V, T<sub>A</sub> =  $+25^{\circ}$ C (unless otherwise noted).

| Symbol            | Parameter                    | Conditions                                               | Min               | Тур         | Max               | Unit |

|-------------------|------------------------------|----------------------------------------------------------|-------------------|-------------|-------------------|------|

| CURRENT           | CONSUMPTION                  |                                                          |                   |             |                   |      |

| I <sub>CC</sub>   | Product Supply Current       | $V_{CC} = 4.2 \text{ V}, \text{ I}_{IS} = 0$             | -                 | 23          | 35                | μΑ   |

| CONTROL           | LOGIC (IN1, IN2 pins)        |                                                          |                   |             |                   |      |

| V <sub>IL</sub>   | Low Voltage Input Threshold  | $V_{CC} = 2.7 V$<br>$V_{CC} = 3.6 V$<br>$V_{CC} = 4.2 V$ |                   | -<br>-<br>- | 0.4<br>0.4<br>0.4 | V    |

| V <sub>IH</sub>   | High Voltage Input Threshold | $V_{CC} = 2.7 V$<br>$V_{CC} = 3.6 V$<br>$V_{CC} = 4.2 V$ | 1.3<br>1.4<br>1.5 | -<br>-<br>- | -<br>-<br>-       | V    |

| V <sub>IHYS</sub> | Voltage Input Hysteresis     |                                                          | -                 | 250         | -                 | mV   |

| I <sub>IN</sub>   | Leakage Current              |                                                          | -                 | -           | ±100              | nA   |

### **ELECTRICAL CHARACTERISTICS**

Min and Max limits apply for T<sub>A</sub> from -40°C to +85°C (unless otherwise noted). Typical values are referenced to V<sub>CC</sub> = 3.6 V, T<sub>A</sub> = +25°C (unless otherwise noted).

| Symbol              | Parameter                         | Conditions                                                                                                                     | Min | Тур  | Max  | Unit |  |  |  |

|---------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--|--|--|

| DATA SWIT           | DATA SWITCHES DC CHARACTERISCTICS |                                                                                                                                |     |      |      |      |  |  |  |

| R <sub>ON</sub>     | On Resistance                     | $V_{CC}$ = 3.0 V $V_{IS}$ from 0 V to 2.4 V, $I_{IS}$ = 15 mA                                                                  | -   | 5    | 7.5  | Ω    |  |  |  |

| R <sub>ON_MAT</sub> | On Resistance Matching            | $V_{CC}$ = 3.0 V $V_{IS}$ from 0 V to 1.7 V, $I_{IS}$ = 15 mA                                                                  | -   | 0.09 | -    | Ω    |  |  |  |

| R <sub>ON_FLT</sub> | On Resistance Flatness            | $\label{eq:V_CC} \begin{array}{l} V_{CC} = 3.0 \ V \\ V_{IS} \ \text{from 0 V to 1.7 V, } I_{IS} = 15 \ \text{mA} \end{array}$ | -   | 0.06 | -    | Ω    |  |  |  |

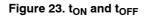

| I <sub>SW_OFF</sub> | Off State Leakage                 | V <sub>CC</sub> = 3.6 V<br>V <sub>IS</sub> From 0 V to 3.6 V                                                                   | -   | -    | 200  | nA   |  |  |  |

| I <sub>SW_ON</sub>  | On State Leakage                  | V <sub>CC</sub> = 3.6 V<br>V <sub>IS</sub> From 0 V to 3.6 V                                                                   | -   | -    | ±200 | nA   |  |  |  |

| DATA SWIT           | CHES AC CHARACTERISTICS           |                                                                                                                                |     |      |      |      |  |  |  |

| C <sub>ON</sub>    | Equivalent On Capacitance     | Switch ON, f = 1 MHz                                                          | - | 4.5                  | - | pF |

|--------------------|-------------------------------|-------------------------------------------------------------------------------|---|----------------------|---|----|

| C <sub>OFF</sub>   | Equivalent Off Capacitance    | Switch OFF, f = 1 MHz                                                         | - | 3                    | - | pF |

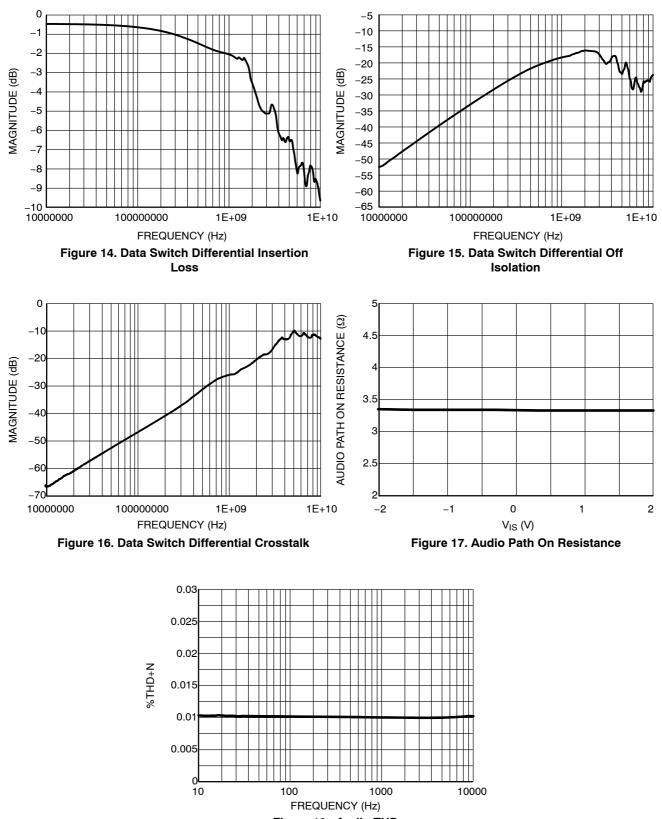

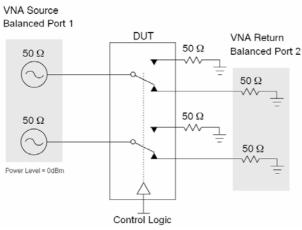

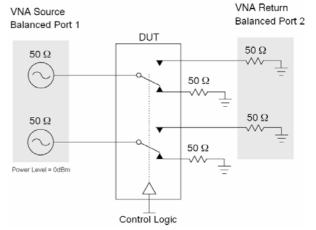

| D <sub>IL</sub>    | Differential Insertion Loss   | f = 10 MHz<br>f = 800 MHz<br>f = 1.1 GHz                                      | - | -0.5<br>-1.8<br>-2.1 | - | dB |

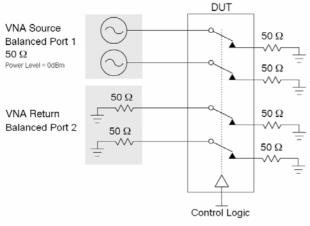

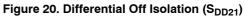

| D <sub>ISO</sub>   | Differential Off Isolation    | f = 10 MHz<br>f = 800 MHz<br>f = 1.1 GHz                                      | - | -53<br>-19<br>-18    | - | dB |

| D <sub>СТК</sub>   | Differential Crosstalk        | f = 10 MHz<br>f = 800 MHz<br>f = 1.1 GHz                                      | _ | -55<br>-20<br>-18    | - | dB |

| PSRR <sub>SW</sub> | Power Supply Ripple Rejection | From V <sub>CC</sub> onto D+ / D–<br>f = 217 Hz, R <sub>L</sub> = 50 $\Omega$ | - | 90                   | - | dB |

#### AUDIO SWITCHES DC CHARACTERISCTICS

| R <sub>ON</sub>     | On Resistance          | $V_{CC}$ = 3.0 V $V_{IS}$ from –2.0 V to 2.0 V, $I_{IS}$ = 50 mA | - | 3    | 5   | Ω |

|---------------------|------------------------|------------------------------------------------------------------|---|------|-----|---|

| R <sub>ON_MAT</sub> | On Resistance Matching | $V_{CC}$ = 3.0 V $V_{IS}$ from –2.0 V to 2.0 V, $I_{IS}$ = 50 mA | - | 0.04 | _   | Ω |

| R <sub>ON_FLT</sub> | On Resistance Flatness | $V_{CC}$ = 3.0 V $V_{IS}$ from –2.0 V to 2.0 V, $I_{IS}$ = 50 mA | - | 0.02 | -   | Ω |

| R <sub>SH</sub>     | Shunt Resistance       | V <sub>CC</sub> = 3.6 V                                          | - | 125  | 200 | Ω |

### AUDIO SWITCHES AC CHARACTERISTICS

| THD <sub>AUD</sub>  | Audio THD                     | From 20 Hz to 20 kHz $V_{IS}$ = 0.4 $V_{RMS}$ , DC bias = 0V, Load = 16 $\Omega$ | _ | 0.01 | _ | %  |

|---------------------|-------------------------------|----------------------------------------------------------------------------------|---|------|---|----|

| PSRR <sub>AUD</sub> | Power Supply Ripple Rejection | From V <sub>CC</sub> onto AUDN / AUDP f = 217 Hz, R <sub>L</sub> = 16 $\Omega$   | - | 90   | - | dB |

#### **ELECTRICAL CHARACTERISTICS**

Min and Max limits apply for  $T_A$  from -40°C to +85°C (unless otherwise noted). Typical values are referenced to  $V_{CC}$  = 3.6 V,  $T_A = +25^{\circ}C$  (unless otherwise noted).

| Symbol                           | Parameter               | Conditions                                                        | Min | Тур  | Max | Unit |  |  |  |

|----------------------------------|-------------------------|-------------------------------------------------------------------|-----|------|-----|------|--|--|--|

| SWITCHES TIMING CHARACTERISCTICS |                         |                                                                   |     |      |     |      |  |  |  |

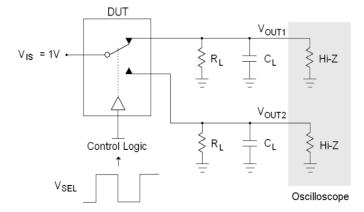

| t <sub>PD</sub>                  | Propagation Delay       | (Notes 6 and 7)                                                   | -   | 0.25 | -   | ns   |  |  |  |

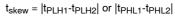

| t <sub>ON</sub>                  | Turn On Time            | $V_{IS}$ = 1 V, $R_L$ = 50 $\Omega$ , $C_L$ = 7 pF (fixture only) | -   | 2.2  | -   | μs   |  |  |  |

| t <sub>OFF</sub>                 | Turn Off Time           | $V_{IS}$ = 1 V, $R_L$ = 50 $\Omega$ , $C_L$ = 7 pF (fixture only) | -   | 67   | -   | ns   |  |  |  |

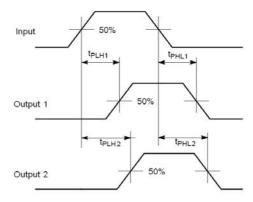

| t <sub>b-b</sub>                 | Bit-to-Bit Skew         | Within the same differential channel                              | -   | 5    | -   | ps   |  |  |  |

| t <sub>ch-ch</sub>               | Channel-to-Channel Skew | Maximum skew between all<br>channels                              | -   | 15   | -   | ps   |  |  |  |

Specification guarantee by design

No other delays than the RC network formed by the load resistance and the load capacitance of the switch are added on the bus. For a 10 pF load, this delay is 5 ns which is much smaller than rise and fall time of typical driving systems. Propagation delays on the bus are determined by the driving circuit on the driving side and its interactions with the load of the driven side.

#### **TABLE OF GRAPHS**

| Symbol                                      | Parameter                                           |                     | Figure |  |

|---------------------------------------------|-----------------------------------------------------|---------------------|--------|--|

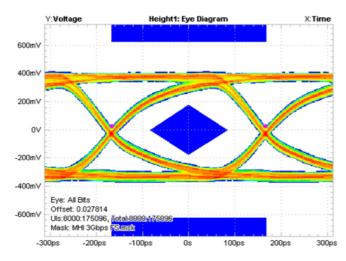

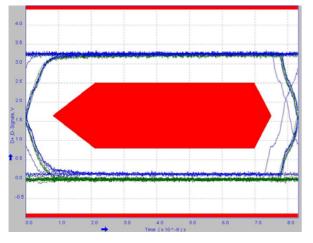

| 1080p <sub>EYE</sub>                        | MHL Video Eye Diagram at 3 Gbps (1080p)             |                     | 4      |  |

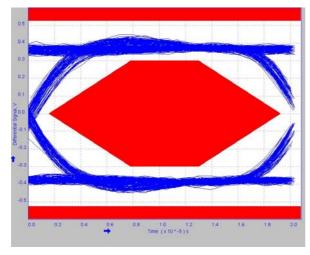

| 720p <sub>EYE</sub><br>1080i <sub>EYE</sub> | MHL Video Eye Diagram at 2.25 Gbps<br>(720p, 1080i) |                     | 5      |  |

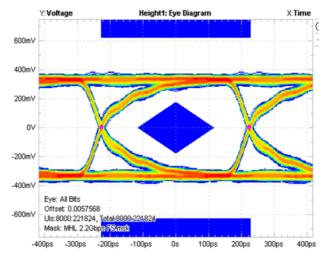

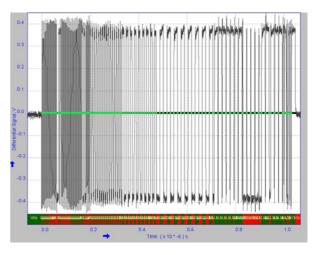

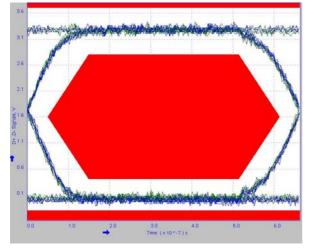

| USB2.0 <sub>EYE</sub>                       | USB 2.0 High Speed 480 Mbps Eye Diagram             |                     | 6, 7   |  |

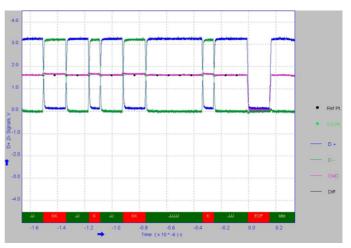

| USB1.1 <sub>EYE</sub>                       | USB 1.1 Full Speed 12 Mbps Eye Diagram              |                     | 8, 9   |  |

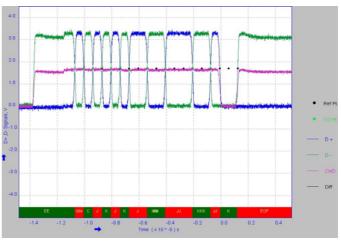

| USB1.0 <sub>EYE</sub>                       | USB 1.0 Low Speed 1.5 Mbps Eye Diagram              |                     | 10, 11 |  |

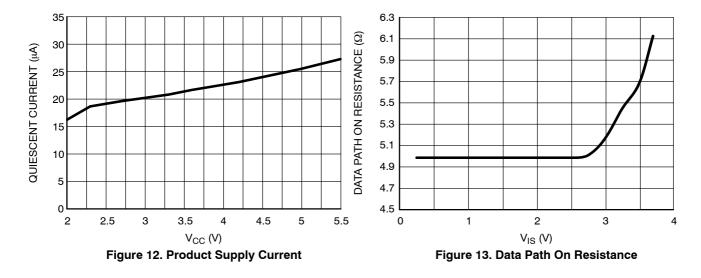

| Icc                                         | Product Supply Current                              | vs. V <sub>CC</sub> | 12     |  |

| R <sub>ON</sub>                             | Data Path On Resistance                             | vs. V <sub>IS</sub> | 13     |  |

| D <sub>IL</sub>                             | Data Switch Differential Insertion Loss             | vs. Frequency       | 14     |  |

| D <sub>ISO</sub>                            | Data Switch Differential Off Isolation              | vs. Frequency       | 15     |  |

| D <sub>CTK</sub>                            | Data Switch Differential Crosstalk                  | vs. Frequency       | 16     |  |

| R <sub>ON</sub>                             | Audio Path On Resistance                            | vs. V <sub>IS</sub> | 17     |  |

| THD <sub>AUD</sub>                          | Audio THD                                           | vs. Frequency       | 18     |  |

### **TYPICAL OPERATING CHARACTERISTICS**

Figure 4. MHL Video Eye Diagram at 3 Gbps (1080p)

Figure 6. USB 2.0 High Speed Eye Diagram

Figure 5. MHL Video Eye Diagram at 2.25 Gbps (720p, 1080i)

Figure 7. USB 2.0 High Speed Pattern

### **TYPICAL OPERATING CHARACTERISTICS**

Figure 8. USB 1.1 Full Speed Eye Diagram

Figure 10. USB 1.0 Low Speed Eye Diagram

Figure 9. USB 1.0 Full Speed Pattern

Figure 11. USB 1.0 Low Speed Pattern

### **TYPICAL OPERATING CHARACTERISTICS**

Figure 18. Audio THD

#### PARAMETER MEASUREMENT INFORMATION

Figure 24. Off State Leakage

Figure 25. On State Leakage

#### **DETAILED APPLICATION**

The NCN1188 voltage range and high bandwidth performance permits switching between audio, video and data signals on a portable device. It allows D+ and D- data pins of a single USB connector to be used for many different functions as pictured by Figure 1:

- USB 2.0 data transfer with backward compatibility to USB 1.1 and USB 1.0

- MHL high definition video transfer up to 3 Gbps for 1080p resolutions

- Audio headset with negative voltage capability to connect true ground audio amplifier

- UART to address programming and testing in factory

- Any other analog or digital data sources within the recommended operating conditions

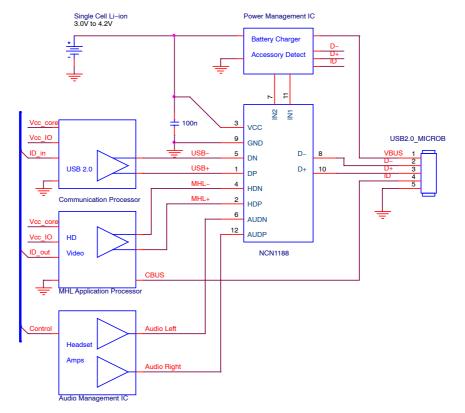

Figures 26 and 27 detail two design examples with different switching combinations using NCN1188.

In the first example shown in Figure 26, the device is directly supplied from a single Li–Ion battery, typically

from 3.0 V to 4.2 V. The NCN1188 switch connects a 5-pin micro-USB connector to a Communication Processor, an MHL Application Processor, and the Audio Management IC headphone amplifier. Each function is active pending on power management IC accessory detection to control IN1 and IN2. This decision is usually made on the D-, D+, and ID pins to detect and differentiate accessory types such as USB cable, USB to HDMI MHL cable and micro-USB stereo headset.

For solutions related to portable devices accessory detection, contact your ON Semiconductor Field Applications Engineer.

The USB 3.0 Micro–B receptacle may be considered a combination of the USB 2.0 Micro–B interface and USB 3.0 SuperSpeed contacts and maintains backward compatibility with USB 2.0 Micro–B plugs. As a consequence, the NCN1188's USB 2.0 capability is fully compatible to the USB 3.0 Micro–B receptacle, as well as USB 2.0 accessories.

Figure 26. Schematic Example for USB 2.0, MHL, and Audio Combination; NCN1188 being supplied from battery

Figure 27. Schematic Example for USB 2.0, MHL, and UART Combination; NCN1188 Being Supplied by Protected VBUS 5 V

In this second design proposal, as NCN1188 must be active only when VBUS accessories are connected (USB cable, UART cable and MHL cable), the device is supplied from a protected VBUS 5 V. This design arrangement limits the system's overall quiescent current and saves battery life. Figure 27 also pictures NCN1188 around a USB 3.0 Micro–B topology: USB 2.0, UART and MHL Video pairs remain multiplexed with D– and D+ while the two USB 3.0 differential pairs are directly connected to the main communication processor.

The flexibility of the NCN1188 offers many extra application and design combinations.

### PCB DESIGN PROCEDURE

Implementing a high speed device requires careful design of signal traces to preserve signal integrity. The following electrical layout guidelines are basic rules to follow when designing boards capable of high speed transmission.

- The bypass capacitor must be placed as close as possible to the V<sub>CC</sub> input pin for noise immunity.

- The PCB should be designed to comply with the characteristic impedance requirements of MHL and USB.

- Make the signal traces as short as possible to reduce losses through the PCB. Furthermore, all corresponding D+ / D- line segment pairs should be the same length.

- The use of turns or bends to route these signals should be avoided when possible. Use 45° bends instead of 90° bends where bends are needed. The use of vias to route these signals should be avoided when possible.

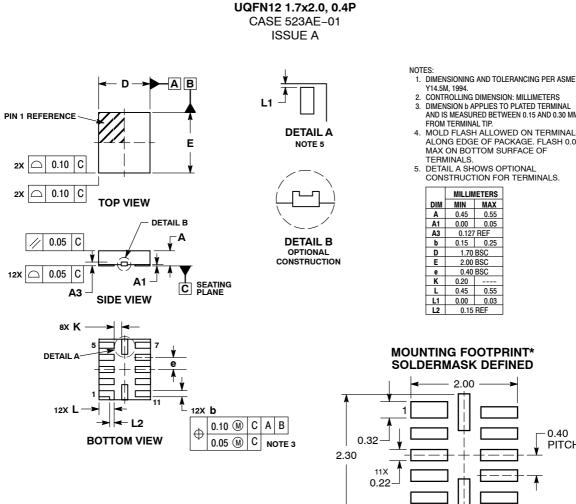

#### PACKAGE DIMENSIONS

- CONTROLLING DIMENSION: MILLIMETERS DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM

- AND IS MEASURED BETWEEN 0.15 AND 0.50 MM FROM TERMINAL TIP. MOLD FLASH ALLOWED ON TERMINALS ALONG EDGE OF PACKAGE. FLASH 0.03 MAX ON BOTTOM SURFACE OF

- DETAIL A SHOWS OPTIONAL CONSTRUCTION FOR TERMINALS.

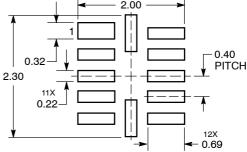

# SOLDERMASK DEFINED

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 🕕 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without the patient of the application or use of the application o limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative