# Single Synchronous Step-Down Controller

The NCP5217A is a synchronous step-down controller for high performance systems battery-power systems. The NCP5217A includes a high efficiency PWM controller. A pin is provided to enable or disable forced PWM mode of operation. An internal power good voltage monitor tracks the SMPS output. NCP5217A also features soft-start sequence, UVLO for  $\rm V_{CC}$  and switcher, overvoltage protection, overcurrent protection, undervoltage protection and thermal shutdown. The IC is packaged in QFN14.

#### **Features**

- 0.8% accuracy 0.8 V Reference

- 4.5 V to 27 V Battery/Adaptor Voltage Range

- Adjustable Output Voltage Range: 0.8 V to 3.3 V

- Selectable Power Saving Mode / Force PWM Mode

- Lossless Inductor Current Sensing

- Programmable Transient-Response-Enhancement (TRE) Control

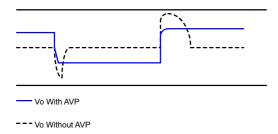

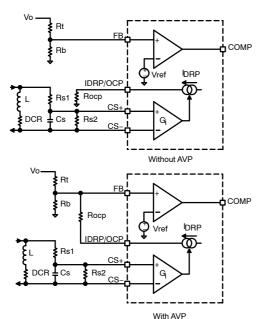

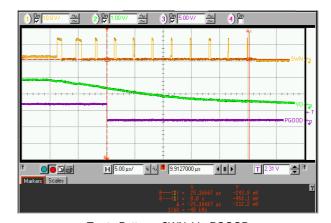

- Programmable Adaptive Voltage Positioning (AVP)

- Input Supply Feedforward Control

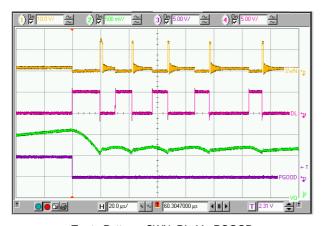

- Internal Soft-Start

- Integrated Output Discharge (Soft-Stop)

- Build-in Adaptive Gate Drivers

- PGOOD Indication

- Overvoltage, Undervoltage and Overcurrent Protections

- Thermal Shutdown

- QFN14 Package

- These Devices are Pb-Free and are RoHS Compliant

# **Typical Applications**

- Notebook Application

- System Power

# ON Semiconductor®

http://onsemi.com

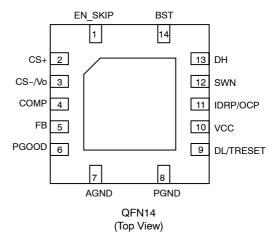

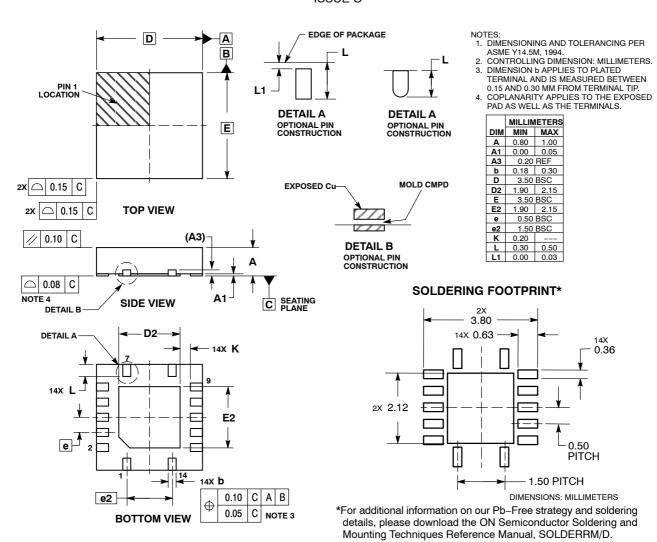

#### QFN14 CASE 485AL

MARKING DIAGRAM

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |  |

|---------------|--------------------|-----------------------|--|

| NCP5217AMNTXG | QFN14<br>(Pb-Free) | 3000 /<br>Tape & Reel |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

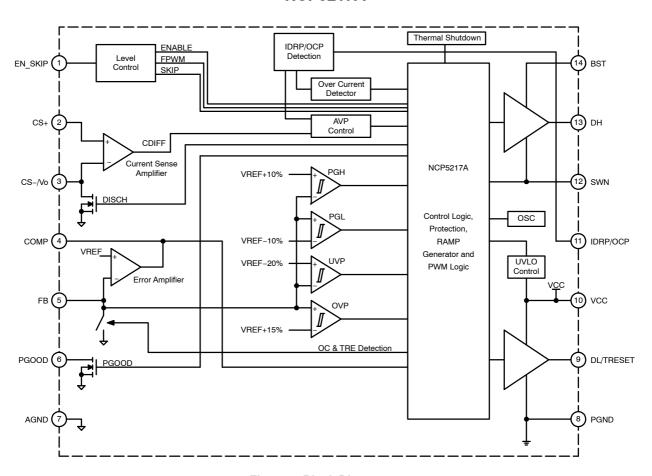

Figure 1. Block Diagram

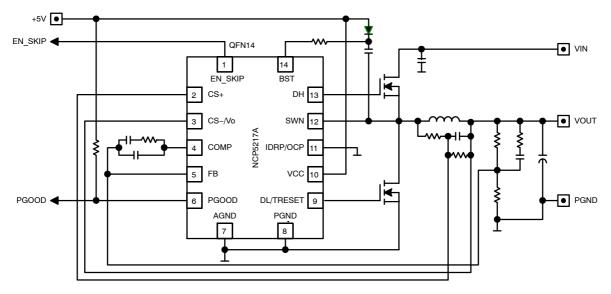

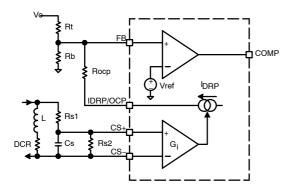

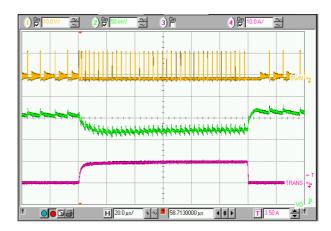

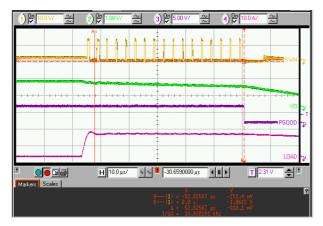

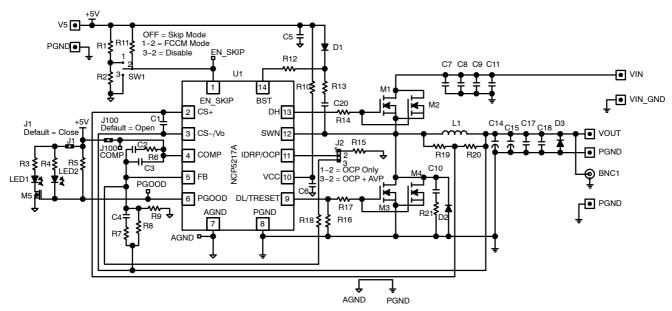

Figure 2. Typical Application Circuit

# **PIN FUNCTION DESCRIPTION**

| Pin No. | Symbol    | Description                                                                                                                                       |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN_SKIP   | This pin serves as two functions. Enable: Logic control for enabling the switcher. SKIP: Power saving mode (Skip and Force PWM) programmable pin. |

| 2       | CS+       | Inductor current differential sense non-inverting input.                                                                                          |

| 3       | CS-/Vo    | Inductor current differential sense inverting input.                                                                                              |

| 4       | COMP      | Output of the error amplifier.                                                                                                                    |

| 5       | FB        | Output voltage feed back.                                                                                                                         |

| 6       | PGOOD     | Power good indicator of the output voltage. High impendence (open drain) if power good (in regulation). Low impendence if power not good.         |

| 7       | AGND      | Analog ground.                                                                                                                                    |

| 8       | PGND      | Ground reference and high-current return path for the bottom gate driver.                                                                         |

| 9       | DL/TRESET | Gate driver output of bottom N-channel MOSFET. It also has the function for TRESET.                                                               |

| 10      | VCC       | Supply for analog circuit and bottom gate driver.                                                                                                 |

| 11      | IDRP/OCP  | Over current protection and Droop Voltage programmable pin.                                                                                       |

| 12      | SWN       | Switch node between the top MOSFET and bottom MOSFET.                                                                                             |

| 13      | DH        | Gate driver output of the top N-channel MOSFET.                                                                                                   |

| 14      | BST       | Top gate driver input supply, a bootstrap capacitor connection between SWN and this pin.                                                          |

# **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                                                                                          | Symbol                                                                                                                                         | Value                   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|

| VCC Power Supply Voltage to AGND                                                                                                                                | VCC                                                                                                                                            | -0.3, 6.0               | V    |

| High-side Gate Drive Supply: BST to SWN High-side Gate Drive Voltage: DH to SWN Low-side Gate Drive Supply: VCC to PGND Low-side Gate Drive Voltage: DL to PGND | V <sub>BST</sub> -V <sub>SWN</sub> ,<br>V <sub>DH</sub> -V <sub>SWN</sub> ,<br>VCC-V <sub>PGND</sub> ,<br>V <sub>DL</sub> -V <sub>PGND</sub> , | -0.3, 6.0               | V    |

| Input / Output Pins to AGND                                                                                                                                     | V <sub>IO</sub>                                                                                                                                | -0.3, 6.0               | V    |

| Switch Node SWN                                                                                                                                                 | V <sub>SWN</sub>                                                                                                                               | -5 V (< 100 ns)<br>30 V | V    |

| High-Side Gate Drive/Low-Side Gate Drive Outputs                                                                                                                | DH, DL                                                                                                                                         | -3(DC)                  | V    |

| PGND                                                                                                                                                            | $V_{PGND}$                                                                                                                                     | -0.3, 0.3               | V    |

| Thermal Characteristics Thermal Resistance Junction-to-Ambient (QFN14 Package)                                                                                  | $R_{\thetaJA}$ QFN14                                                                                                                           | 48                      | °C/W |

| Operating Junction Temperature Range (Note 1)                                                                                                                   | T <sub>J</sub>                                                                                                                                 | -40 to + 150            | °C   |

| Operating Ambient Temperature Range                                                                                                                             | T <sub>A</sub>                                                                                                                                 | – 40 to + 85            | °C   |

| Storage Temperature Range                                                                                                                                       | T <sub>stg</sub>                                                                                                                               | – 55 to +150            | °C   |

| Moisture Sensitivity Level                                                                                                                                      | MSL                                                                                                                                            | 1                       | _    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

1. Internally limited by thermal shutdown, 150°C min.

**ELECTRICAL CHARACTERISTICS** (V<sub>IN</sub> = 12 V, V<sub>CC</sub> = 5 V, T<sub>A</sub> = -40°C to 85°C, unless other noted)

| Voc Operating Voltage         Voc           SUPPLY CURRENT           Voc Quiescent Supply Current in FPWM operation         IVCC_FPWM         EN_SKIP = 2.0 V, VFB forced above regulation point. DH, DL are open           Voc Quiescent Supply Current in Power Saving Operation         IVCC_PS         EN_SKIP = 5 V, VFB forced above regulation point. DH, DL are open           Voc Shutdown Current         IVCC_SD         EN_SKIP = L, Vcc = 5 V, true shutdown           BST Quiescent Supply Current in FPWM operation         IBST_FPWM         EN_SKIP = 1.5 V, VFB forced above regulation point. DH and DL are open, No boost trap diode           BST Quiescent Supply Current in power-saving operation         IBST_PS         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_PS         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_PS         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_PS         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Quiescent Supply Current in FPWM operation         IBST_Shut Ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min      | Тур               | Max    | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|--------|------|

| Voc Operating Voltage         Voc           SUPPLY CURRENT           Voc Quiescent Supply Current in FPWM operation         IVCC_FPWM         EN_SKIP = 2.0 V. VFB forced above regulation point. DH, DL are open regulation point. DH and DL are open, No boost trap diode           BST Quiescent Supply Current in FPWM operation         IBST_FPWM         EN_SKIP = 1.5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Quiescent Supply Current in FPWM operation         IBST_FPWM         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Suldescent Supply Current in power-saving operation         IBST_PS         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SPS         EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Curre                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 1                 | 1      | 1    |

| SUPPLY CURRENT  Voc Quiescent Supply Current in FPWM operation  Voc Shutdown Current  IVCC_PS  EN_SKIP = 5 V, VFB forced above regulation point. DH, DL are open  Voc Shutdown Current  IVCC_SD  EN_SKIP = L, Vcc = 5 V, true shutdown  BST Quiescent Supply Current in FPWM operation  BST_PS  EN_SKIP = 1.5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  IBST_PS  EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  IBST_SD  EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  IBST_SD  EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  IBST_PS  EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  IBST_PS  EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  IBST_PS  EN_SKIP = 1.5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  EN_SKIP = 1.5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode  EN_SKIP = 1.5 V, VFB forced above regulation point, DH and DL are open, No boost trap flower spulled above regulation point, DH and DL are open, No boost trap diode  EN_SKIP = 1.5 V, VFB flower glob above regulation point, DH and DL are open, No boost trap diode  EN_SKIP = 1.5 V, VFB flower glob above regulation point, DH and DL are open, No boost trap flower glob above regulation point, DH and DL are open, No boost trap flower glob above regulation point, DH and DL are spen, No boost trap flower glob above regulation point, DH and DL are spen,                    | 4.5      | _                 | 27     | V    |

| V <sub>CC</sub> Quiescent Supply Current in FPWM operation         IVCC_FPWM         EN_SKIP = 2.0 V. V <sub>FB</sub> forced above regulation point. DH, DL are open           V <sub>CC</sub> Quiescent Supply Current in Power Saving Operation         IVCC_PS         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point. DH, DL are open           V <sub>CC</sub> Shutdown Current         IVCC_SD         EN_SKIP = 1, V <sub>CC</sub> = 5 V, true shutdown           BST Quiescent Supply Current in FPWM operation         IBST_FPWM         EN_SKIP = 1.5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode           BST Quiescent Supply Current in power-saving operation         IBST_PS         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode           BST Shutdown Current         IBST_SD         EN_SKIP = 6 V, V <sub>F</sub>                                                                                                                                                                                                                                                                                                                                                                         | 4.5      | 5.0               | 5.5    | V    |

| in FPVM operation regulation point. DH, DL are open  V <sub>CC</sub> Quiescent Supply Current in Power Saving Operation PV <sub>CC</sub> Shutdown Current IVCC_SD EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH, DL are open PV <sub>CC</sub> Shutdown Current IVCC_SD EN_SKIP = L, V <sub>CC</sub> = 5 V, true shutdown  BST Quiescent Supply Current INST_FPVM EN_SKIP = 1.5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode  BST Quiescent Supply Current in PVM operation PVM Department INST_PS EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current INST_PS EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open No boost trap diode  BST Shutdown Current INST_PS EN_SKIP = 0 V EN_SKIP = 0 V  VOLTAGE-MONITOR  BST_SD EN_SKIP = 0 V  VOLTAGE-MONITOR  BIST_SD EN_SKIP = 0 V  VCC UVLO Hysteresis VCCHYS  VCC UVLO Hysteresis VCCHYS  VCCHYS Power Good High Threshold VPGH PGOOD in from higher Vo (PGOOD goes high)  Power Good High Hysteresis VPGH_HYS PGOOD in from lower Vo (PGOOD goes low)  Power Good Low Threshold VPGL PGOOD goes low)  Power Good Low Hysteresis VPGL_HYS PGOOD low hysteresis (PGOOD goes low)  Power Good Low Delay Td_PGH  Power Good Low Delay Td_PGL  Output Overvoltage Rising Threshold VPThreshold Delay  Overvoltage Fault Propagation DVPth With respect to Error Comparator Threshold of 0.8 V  Overvoltage Fault Propagation UVPTblk  BREFERENCE OUTPUT  Internal Reference Voltage VREF D. SCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ·        |                   |        |      |

| in Power Saving Operation  V <sub>CC</sub> Shutdown Current  IVCC_SD  EN_SKIP = L, V <sub>CC</sub> = 5 V, true shutdown  BST Quiescent Supply Current in FPWM operation  BST Quiescent Supply Current in FPWM operation  BST Quiescent Supply Current in PWM operation  BST Shutdown Current  BST_SD  EN_SKIP = 5 V, V <sub>FB</sub> forced above regulation point, DH and DL are open, No boost trap diode  BST Shutdown Current  BST_SD  EN_SKIP = 0 V  VOLTAGE-MONITOR  Rising V <sub>CC</sub> Threshold  VCCh  VCCHYS  VCCHYS  Power Good High Threshold  VPGH  PGOOD in from higher Vo (PGOOD goes high)  Power Good High Hysteresis  VPGH_HYS  PGOOD high hysteresis  VPGL_HYS  PGOOD high hysteresis  POWER Good Low Threshold  VPGL  PGOOD goes low)  Power Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis  POWER Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis  POWER Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  OVPth+  With respect to Error Comparator Threshold of 0.8 V  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 1.5               | 2.5    | mA   |

| BST Quiescent Supply Current in FPWM peration   IBST_FPWM   EN_SKIP = 1.5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode   IBST_PS   EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open, No boost trap diode   IBST_PS   EN_SKIP = 5 V, VFB forced above regulation point, DH and DL are open No boost trap diode   IBST_Shutdown Current   IBST_SD   EN_SKIP = 0 V   IBST_SKIP = 0 V   I                    |          | 1.5               | 2.5    | mA   |

| regulation point, DH and DL are open, No boost trap diode  BST Quiescent Supply Current in power-saving operation  BST Shutdown Current  BST_SD  EN_SKIP = 0 V  dV/dt on V <sub>CC</sub> dVCC/dt  (Note 2)  VOLTAGE-MONITOR  Rising V <sub>CC</sub> Threshold  VCC HYS  Power Good High Threshold  VPGH  Power Good Low Threshold  VPGL  Power Good Low Hysteresis  VPGL_HYS  Power Good High Delay  Power Good High Delay  Power Good Low Delay  Td_PGL  Output Overvoltage Rising  Threshold  OVPTblk  Dutput Undervoltage Protection  BST_SNLP = 0 V  EN_SKIP = 0 V  (Note 2)  EN_SKIP = 0 V  (Note 2)  FN_SKIP = 0 V  (Note 2)  FN_SKIP = 0 V  EN_SKIP = 0 V |          |                   | 1      | uA   |

| in power-saving operation    regulation point, DH and DL are open No boost trap diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                   | 0.3    | mA   |

| dV/dt on V <sub>CC</sub> VOLTAGE-MONITOR  Rising V <sub>CC</sub> Threshold  VCC UVLO Hysteresis  VCCHYS  Power Good High Threshold  VPGH  PGOOD in from higher Vo (PGOOD goes high)  Power Good Low Threshold  VPGL  Power Good Low Hysteresis  VPGL  PGOOD low hysteresis (PGOOD goes high)  Power Good Low Hysteresis  VPGL  PGOOD low hysteresis (PGOOD goes low)  Power Good Low Hysteresis  VPGL  PGOOD low hysteresis (PGOOD goes low)  Power Good Low Delay  Td  PGH  Power Good Low Delay  Td  PGH  Power Good Low Delay  Td  PGH  VPGL  With respect to Error Comparator Threshold of 0.8 V  Overvoltage Fault Propagation  Delay  Output Undervoltage Trip  Threshold  Output Undervoltage Protection  Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                   | 0.3    | mA   |

| VOLTAGE-MONITOR         Rising V <sub>CC</sub> Threshold       VCCHYS       4         V <sub>CC</sub> UVLO Hysteresis       VCCHYS       2         Power Good High Threshold       VPGH       PGOOD in from higher Vo (PGOOD goes high)       1         Power Good High Hysteresis       VPGH_HYS       PGOOD high hysteresis (PGOOD goes low)       2         Power Good Low Threshold       VPGL       PGOOD in from lower Vo (PGOOD goes high)       3         Power Good Low Hysteresis       VPGL_HYS       PGOOD low hysteresis (PGOOD goes low)       3         Power Good High Delay       Td_PGH       4       4         Power Good Low Delay       Td_PGL       4       4       4         Power Good Low Delay       Td_PGL       5       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4       4 <t< td=""><td></td><td></td><td>1</td><td>μΑ</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                   | 1      | μΑ   |

| Rising V <sub>CC</sub> Threshold VCCth+ Wake Up 4 V <sub>CC</sub> UVLO Hysteresis VCCHYS 2 Power Good High Threshold VPGH PGOOD in from higher Vo (PGOOD goes high) 1 Power Good High Hysteresis VPGH_HYS PGOOD high hysteresis (PGOOD goes low) 2 Power Good Low Threshold VPGL PGOOD goes high) 7 Power Good Low Hysteresis VPGL_HYS PGOOD in from lower Vo (PGOOD goes high) 8 Power Good Low Hysteresis VPGL_HYS PGOOD low hysteresis (PGOOD goes low) 9 Power Good High Delay Td_PGH Power Good Low Delay Td_PGL VITH With respect to Error Comparator Threshold of 0.8 V 1 Overvoltage Fault Propagation Delay DVPTblk PB forced 2% above trip threshold Delay Output Undervoltage Trip Threshold UVPTblk With respect to Error Comparator Threshold Output Undervoltage Protection Blanking Time VVPTblk With respect to Error Comparator Threshold Output Undervoltage Protection UVPTblk Blanking Time 0.5  REFERENCE OUTPUT 1 Internal Reference Voltage VREF 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -10      |                   | 10     | V/μs |

| Power Good High Threshold  VPGH  PGOOD in from higher Vo (PGOOD goes high)  Power Good High Hysteresis  VPGH_HYS  PGOOD high hysteresis (PGOOD goes low)  Power Good Low Threshold  VPGL  PGOOD goes low)  Power Good Low Hysteresis  VPGL_HYS  PGOOD in from lower Vo (PGOOD goes low)  Power Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis (PGOOD goes low)  Power Good High Delay  Td_PGH  Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  OVPTh+  With respect to Error Comparator Threshold of 0.8 V  Overvoltage Fault Propagation Delay  Output Undervoltage Trip UVPth With respect to Error Comparator Threshold  Output Undervoltage Trip Threshold  UVPTblk  With respect to Error Comparator Threshold of 0.8 V  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                   |        |      |

| Power Good High Threshold  VPGH  PGOOD in from higher Vo (PGOOD goes high)  Power Good High Hysteresis  VPGH_HYS  PGOOD high hysteresis (PGOOD goes low)  Power Good Low Threshold  VPGL  PGOOD in from lower Vo (PGOOD goes low)  Power Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis (PGOOD goes high)  Power Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis (PGOOD goes low)  Power Good Low Delay  Td_PGH  Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  OVPTh+  With respect to Error Comparator Threshold of 0.8 V  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  OVPTblk  With respect to Error Comparator Threshold of 0.8 V  Output Undervoltage Trip Threshold  UVPTblk  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.05     | 4.25              | 4.48   | V    |

| Power Good High Hysteresis  VPGH_HYS  PGOOD high hysteresis (PGOOD goes low)  Power Good Low Threshold  VPGL  PGOOD in from lower Vo (PGOOD goes high)  Power Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis (PGOOD goes low)  Power Good High Delay  Td_PGH  Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VPGL  PGOOD in from lower Vo (PGOOD goes low)  PGOOD low hysteresis (PGOOD goes high)  PGOOD low hysteresis (PGOOD goes low)  PGOOD goes low)  POWER SOOD BOOD GOES LOW  PGOOD goes low)  POWER SOOD BOOD GOES LOW  PGOOD goes low)  POWER SOOD BOOD GOES LOW  PGOOD goes low)  PGOOD goes low)  POWER SOOD GOES LOW  PGOOD goes low)  PGOOD goes low)  PGOOD goes low)  POWER SOOD GOES LOW  PGOOD goes low)  POWER SOOD GOES LOW  PGOOD goes low)  PGOOD goes low  PGOOD goes low)  PGOOD goes low  POWER SOOD goes low  PGOOD goes low  POWER SOOD goes low  PGOOD goes low  POWER SOOD goes low  POWER SOOD goes low  PGOOD goes low  POWER SOOD goes low  POWER SOOD goes low  POWER SOOD goes low  PGOOD goes low  POWER SOOD goes low  POWER SOOD goes low  PGOOD goes low  PGOOD goes low  POWER SOOD                     | 200      | 275               | 400    | mV   |

| Power Good Low Threshold  Power Good Low Threshold  Power Good Low Hysteresis  Power Good Low Hysteresis  Power Good Low Hysteresis  Power Good Low Hysteresis  Power Good High Delay  Power Good Low Delay  Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  Overvoltage Fault Propagation Delay  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  UVPth With respect to Error Comparator Threshold  FB forced 2% above trip threshold  Output Undervoltage Trip Threshold  UVPTblk  With respect to Error Comparator Threshold of 0.8 V   Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  O.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105      | 110               | 115    | %    |

| Power Good Low Hysteresis  VPGL_HYS  PGOOD low hysteresis (PGOOD goes low)  Power Good High Delay  Td_PGH  Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VPGL_HYS  PGOOD low hysteresis (PGOOD goes low)  PGOOD goes high)  PGOOD goes high  PGOOD goes high)  PGOOD goes high)  PGOOD goes high  PGOOD goes hi                    |          | 5                 |        | %    |

| Power Good High Delay  Td_PGH  Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  (PGOOD goes low)  (Independence location goes location go                    | 80       | 85                | 90     | %    |

| Power Good Low Delay  Td_PGL  Output Overvoltage Rising Threshold  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  Overvoltage Rising OVPth+ With respect to Error Comparator Threshold  OVPTblk With respect to Error Comparator Threshold of 0.8 V  Output Undervoltage Protection Blanking Time  VREF  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | -5                |        | %    |

| Output Overvoltage Rising Threshold  OVPth+ With respect to Error Comparator Threshold of 0.8 V  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Trip Threshold  UVPth With respect to Error Comparator Threshold of 0.8 V  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage VREF  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 150               |        | us   |

| Threshold Threshold of 0.8 V  Overvoltage Fault Propagation Delay  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  OVPTblk  FB forced 2% above trip threshold  With respect to Error Comparator Threshold of 0.8 V  UVPTblk  UVPTblk  REFERENCE OUTPUT  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 1.5               |        | us   |

| Delay  Output Undervoltage Trip Threshold  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage  VREF  OSCILLATOR  With respect to Error Comparator Threshold of 0.8 V  UVPTblk  UVPTblk  VREF  O.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110      | 115               | 120    | %    |

| Threshold Threshold of 0.8 V  Output Undervoltage Protection Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage VREF 0.3  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 1.5               |        | us   |

| Blanking Time  REFERENCE OUTPUT  Internal Reference Voltage VREF 0.3  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75       | 80                | 85     | %    |

| Internal Reference Voltage VREF 0.3  OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -        | 8/f <sub>SW</sub> | _      | s    |

| OSCILLATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                   |        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.7936   | 0.8               | 0.8064 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                   |        |      |

| Operation Frequency FSW 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 270      | 300               | 330    | kHz  |

| OVERCURRENT THRESHOLD DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u> </u> |                   |        |      |

| Total Detection Time T <sub>DETECT</sub> A short period before SS 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.26     | 1.92              | 2.21   | ms   |

| OCSET Detection Time T_OCDET (Note 2) 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.09     |                   | 1.47   | ms   |

<sup>2.</sup> Guaranteed by design, not tested in production.

# **ELECTRICAL CHARACTERISTICS** (V<sub>IN</sub> = 12 V, V<sub>CC</sub> = 5 V, T<sub>A</sub> = -40°C to 85°C, unless other noted)

| Characteristics                                   | Symbol                                            | Test Con                                                            | Min                                                  | Тур   | Max        | Unit  |                |

|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------|-------|------------|-------|----------------|

| INTERNAL SOFT-START                               |                                                   |                                                                     |                                                      | 1     | •          | 1     |                |

| Soft-Start Time                                   | T <sub>SS</sub>                                   |                                                                     |                                                      | 0.9   | 1.1        | 1.3   | ms             |

| VOLTAGE ERROR AMPLIFIER                           |                                                   |                                                                     |                                                      | -     |            | -     |                |

| DC Gain                                           | GAIN_VEA                                          | (Note                                                               | e 2)                                                 |       | 88         |       | dB             |

| Unity Gain Bandwidth                              | BW_VEA                                            | (Note                                                               | e 2)                                                 |       | 15         |       | MHz            |

| Slew Rate                                         | SR_VEA                                            | COMP PIN TO GND                                                     | = 100 pF (Note 2)                                    |       | 2.5        |       | V/μs           |

| FB Bias Current                                   | lbias_FB                                          |                                                                     |                                                      |       |            | 0.1   | μΑ             |

| Output Voltage Swing                              | Vmax_EA                                           | Isource_E                                                           | A = 2 mA                                             | 3.3   | 3.5        |       | V              |

|                                                   | Vmin_EA                                           | lsink_EA                                                            | = 2 mA                                               |       | 0.15       | 0.3   |                |

| DIFFERENTIAL CURRENT SENS                         | SE AMPLIFIER                                      | -                                                                   |                                                      |       |            |       |                |

| CS+ and CS- Common-mode<br>Input Signal Range     | VCSCOM_MAX                                        | Refer to                                                            | AGND                                                 |       |            | 3.5   | ٧              |

| Input Bias Current                                | CS_IIB                                            |                                                                     |                                                      | -100  |            | 100   | nA             |

| Input Signal Range                                | CS_range                                          |                                                                     |                                                      | -70   |            | 70    | mV             |

| Offset Current at IDRP                            | IDRP_offset                                       | (CS+) - (C                                                          | S-) = 0 V                                            | -1.0  |            | 1.0   | μΑ             |

| [(CS+) - (CS-)] to IDRP Gain                      | IDRP_GAIN                                         | (CS+) - (CS-) =                                                     | T <sub>A</sub> = 25°C                                | 0.475 | 0.525      | 0.575 | μ <b>A</b> /mV |

|                                                   | (IDRP/((CS+) -<br>(CS-)))                         | 10 mV, V(IDRP) =<br>0.8 V                                           | T <sub>A</sub> =-40°C to 85°C                        | 0.425 |            | 0.625 | 1              |

| Current-Sense Bandwidth                           | BW_CS                                             | At -3dB to DC                                                       | At -3dB to DC Gain (Note 2)                          |       | 20         |       | MHz            |

| Maximum IDRP Output Voltage                       | IDRP_Max                                          | (CS+) - (CS-) = 70 n<br>95% of the value wh                         | 2.5                                                  |       |            | ٧     |                |

| Minimum IDRP Output Voltage                       | IDRP_Min                                          |                                                                     |                                                      |       | 0          |       | V              |

| IDRP Output current                               | I_IDRP                                            |                                                                     |                                                      | -1.0  |            | 35    | μΑ             |

| OVERCURRENT PROTECTION                            | SETTING                                           |                                                                     |                                                      |       |            |       |                |

| Overcurrent Threshold (OCTH)<br>Detection Current | I_OCSET                                           | Sourced from OCP<br>Rocp = 16.7 kΩ is cor<br>AGND                   | nected from OCP to                                   | 21.6  | 24         | 26.4  | μΑ             |

| Ratio of OC Threshold over<br>OCSET Voltage       | K_OCSET                                           | V((CS+) - (CS-<br>(Note                                             |                                                      |       | 0.1        |       | -              |

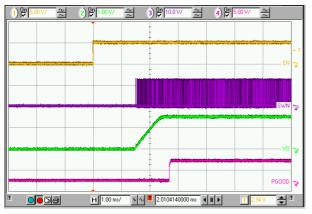

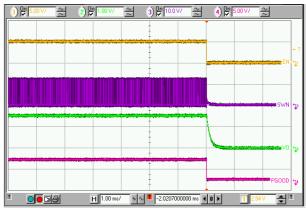

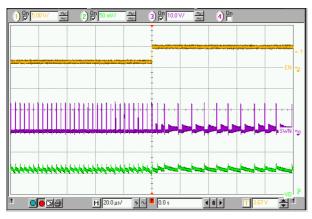

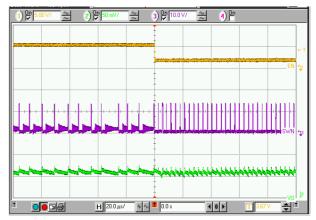

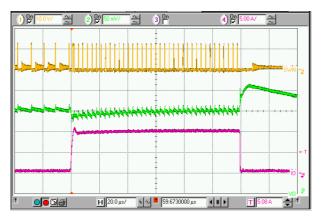

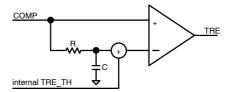

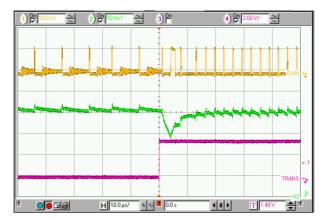

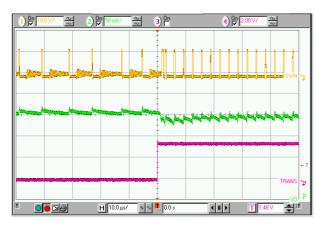

| OCSET Voltage for Default Fixed OC Threshold      | VOCSET_DFT                                        | $Rocp \leq 2 \ k\Omega \ is \ conr \ AGND$                          |                                                      |       |            | 100   | mV             |