# **5.0 V Micropower 150 mA** LDO Linear Regulator with DELAY, Adjustable RESET, and Sense Output

The NCV4279 is a 5.0 V precision micropower voltage regulator with an output current capability of 150 mA.

The output voltage is accurate within  $\pm 2.0\%$  with a maximum dropout voltage of 0.5 V at 100 mA. Low quiescent current is a feature drawing only 150  $\mu$ A with a 1.0 mA load. This part is ideal for any and all battery operated microprocessor equipment.

Microprocessor control logic includes an active reset output RO with delay and a SI/SO monitor which can be used to provide an early warning signal to the microprocessor of a potential impending reset signal. The use of the SI/SO monitor allows the microprocessor to finish any signal processing before the reset shuts the microprocessor down.

The active Reset circuit operates correctly at an output voltage as low as 1.0 V. The Reset function is activated during the power up sequence or during normal operation if the output voltage drops outside the regulation limits.

The reset threshold voltage can be decreased by the connection of an external resistor divider to the  $R_{ADJ}$  lead. The regulator is protected against reverse battery, short circuit, and thermal overload conditions. The device can withstand load dump transients making it suitable for use in automotive environments. The device has also been optimized for EMC conditions.

If the application requires pullup resistors at the logic outputs Reset and Sense Out, the NCV4269 with integrated resistors can be used.

#### Features

- 5.0 V ± 2.0% Output

- Low 150 µA Quiescent Current

- Active Reset Output Low Down to  $V_0 = 1.0 V$

- Adjustable Reset Threshold

- 150 mA Output Current Capability

- Fault Protection

- +60 V Peak Transient Voltage

- ♦ -40 V Reverse Voltage

- Short Circuit

- Thermal Overload

- Early Warning through SI/SO Leads

- Internally Fused Leads in SO-14 Package

- Very Low Dropout Voltage

- Electrical Parameters Guaranteed Over Entire Temperature Range

- These are Pb–Free Devices

- NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

| 8           | SO-8<br>D1 SUFFIX<br>CASE 751                 | MARKING<br>DIAGRAMS<br>8 H H H<br>4279<br>ALYW<br>1 H H H H |

|-------------|-----------------------------------------------|-------------------------------------------------------------|

| 14 5588 558 | SO-14<br>D2 SUFFIX<br>CASE 751A               | 14 A A A A A A A A<br>NCV4279<br>O AWLYWWG<br>14 4 4 4 4 4  |

| YY,         | ., L = Wafer L<br>, Y = Year<br>V, W = Work W |                                                             |

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

© Semiconductor Components Industries, LLC, 2011 February, 2011 – Rev. 6

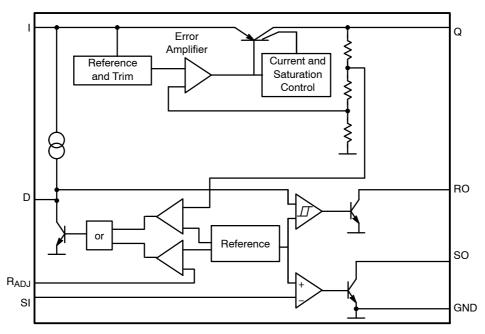

Figure 1. Block Diagram

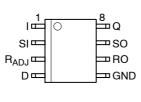

#### **PIN CONNECTIONS**

SO-8

SO-14

## PACKAGE PIN DESCRIPTION

| Package Pin Number    |                           |                  |                                                                            |  |

|-----------------------|---------------------------|------------------|----------------------------------------------------------------------------|--|

| SO-8 SO-14 Pin Symbol |                           | Pin Symbol       | Function                                                                   |  |

| 3                     | 1                         | R <sub>ADJ</sub> | Reset Threshold Adjust; if not used to connect to GND.                     |  |

| 4                     | 2                         | D                | Reset Delay; To Set Time Delay, Connect to GND with a Capacitor            |  |

| 5                     | 3, 4, 5, 6,<br>10, 11, 12 | GND              | Ground                                                                     |  |

| 6                     | 7                         | RO               | Reset Output; This is an Open-Collector Output. Leave Open if Not Used.    |  |

| 7                     | 8                         | SO               | Sense Output; This is an Open-Collector Output. If not used, keep open.    |  |

| 8                     | 9                         | Q                | 5 V Output; Connect to GND with a 10 $\mu F$ Capacitor, ESR < 10 $\Omega.$ |  |

| 1                     | 13                        | I                | Input; Connect to GND Directly at the IC with a Ceramic Capacitor.         |  |

| 2                     | 14                        | SI               | Sense Input; If not used, Connect to Q.                                    |  |

#### **MAXIMUM RATINGS** ( $T_J = -40^{\circ}C$ to $150^{\circ}C$ )

| Parameter                                                             | Symbol                                 | Min                        | Max                      | Unit    |

|-----------------------------------------------------------------------|----------------------------------------|----------------------------|--------------------------|---------|

| Input to Regulator                                                    | V <sub>I</sub><br>II                   | -40<br>Internally Limited  | 45<br>Internally Limited | V       |

| Input Peak Transient Voltage                                          | VI                                     | -                          | 60                       | V       |

| Sense Input                                                           | V <sub>SI</sub><br>I <sub>SI</sub>     | -40<br>-1                  | 45<br>1                  | V<br>mA |

| Reset Threshold Adjust                                                | V <sub>RADJ</sub><br>I <sub>RADJ</sub> | -0.3<br>-10                | 7<br>10                  | V<br>mA |

| Reset Delay                                                           | V <sub>D</sub><br>I <sub>D</sub>       | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Ground                                                                | ۱ <sub>q</sub>                         | 50                         | -                        | mA      |

| Reset Output                                                          | V <sub>RO</sub><br>I <sub>RO</sub>     | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Sense Output                                                          | V <sub>SO</sub><br>I <sub>SO</sub>     | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Regulated Output                                                      | V <sub>Q</sub><br>I <sub>Q</sub>       | -0.5<br>-10                | 7.0<br>-                 | V<br>mA |

| Junction Temperature<br>Storage Temperature                           | T <sub>J</sub><br>T <sub>STG</sub>     | _<br>_50                   | 150<br>150               | °C<br>℃ |

| Input Voltage Operating Range<br>Junction Temperature Operating Range | V <sub>I</sub><br>T <sub>J</sub>       | _<br>_40                   | 45<br>150                | °C<br>℃ |

#### LEAD TEMPERATURE SOLDERING AND MSL

| Parameter                                                 |     | Value | Unit |

|-----------------------------------------------------------|-----|-------|------|

| MSL, 8-Lead, 14-Lead, LS Temperature 260°C Peak (Notes 3) | MSL | 1     | -    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device series incorporates ESD protection and exceeds the following ratings: Human Body Model (HBM) ≤ 2.0 kV per JEDEC standard: JESD22–A114.

Machine Model (MM)  $\leq$  200 V per JEDEC standard: JESD22–A115.

Latchup Current Maximum Rating: ≤ 150 mA per JEDEC standard: JESD78.

Lead free: 60–150 Sec above 217°C, 40 Sec Max at Peak, 265°C Peak.

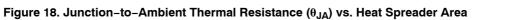

#### THERMAL CHARACTERISTICS

| Characteristic                                                          | Test Conditions (Typical Values) | Unit |

|-------------------------------------------------------------------------|----------------------------------|------|

| SO-8 Package (Note 4)                                                   |                                  |      |

| Junction–to–Pin 4 ( $\Psi$ – JL4, $\Psi$ <sub>L4</sub> )                | 53.8                             | °C/W |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}, \theta_{JA}$ ) | 170.9                            | °C/W |

| SO-14 Package (Note 4)                                                  |                                  |      |

| Junction–to–Pin 4 ( $\Psi$ – JL4, $\Psi$ <sub>L4</sub> )                | 18.4                             | °C/W |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}, \theta_{JA}$ ) | 111.6                            | °C/W |

4. 2 oz copper, 50 mm<sup>2</sup> copper area, 1.5 mm thick FR4

## **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = -40°C $\leq$ T<sub>J</sub> $\leq$ 125°C, V<sub>I</sub> = 13.5 V unless otherwise specified)

| Characteristic                         | Symbol               | Test Conditions                                                                        | Min  | Тур  | Max  | Unit |  |

|----------------------------------------|----------------------|----------------------------------------------------------------------------------------|------|------|------|------|--|

| REGULATOR                              |                      |                                                                                        |      |      |      |      |  |

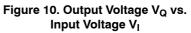

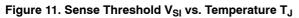

| Output Voltage                         | V <sub>Q</sub>       | $1 \text{ mA} \le I_Q \le 100 \text{ mA}; 6 \text{ V} \le \text{V}_I \le 16 \text{ V}$ | 4.90 | 5.00 | 5.10 | V    |  |

| Current Limit                          | Ι <sub>Q</sub>       | -                                                                                      | 150  | 200  | 500  | mA   |  |

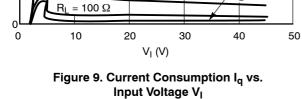

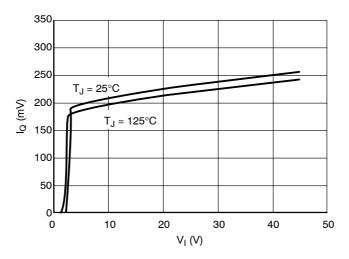

| Current Consumption; $I_q = I_I - I_Q$ | Ι <sub>q</sub>       | l <sub>Q</sub> = 1 mA, RO, SO High                                                     | -    | 190  | 250  | μΑ   |  |

| Current Consumption; $I_q = I_I - I_Q$ | Ι <sub>q</sub>       | I <sub>Q</sub> = 10 mA, RO, SO High                                                    | -    | 250  | 450  | μΑ   |  |

| Current Consumption; $I_q = I_I - I_Q$ | Ι <sub>q</sub>       | I <sub>Q</sub> = 50 mA, RO, SO High                                                    | -    | 2.0  | 3.0  | mA   |  |

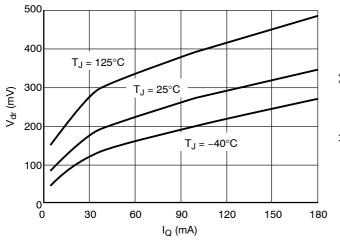

| Dropout Voltage                        | V <sub>dr</sub>      | l <sub>Q</sub> = 100 mA (Note 5)                                                       | -    | 0.25 | 0.5  | V    |  |

| Load Regulation                        | $\Delta V_Q$         | I <sub>Q</sub> = 5 mA to 100 mA                                                        | -    | 10   | 20   | mV   |  |

| Line Regulation                        | $\Delta V_Q$         | $V_{I} = 6 V \text{ to } 26 V; I_{Q} = 1 \text{ mA}$                                   | -    | 10   | 30   | mV   |  |

| RESET GENERATOR                        |                      |                                                                                        |      |      |      |      |  |

| Reset Switching Threshold              | V <sub>RT</sub>      | -                                                                                      | 4.50 | 4.65 | 4.80 | V    |  |

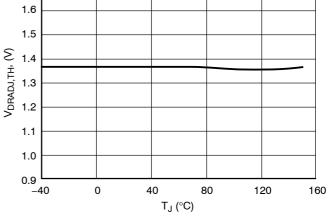

| Reset Adjust Switching Threshold       | V <sub>RADJ,TH</sub> | V <sub>Q</sub> > 3.5 V                                                                 | 1.26 | 1.35 | 1.44 | V    |  |

| Reset Output Saturation Voltage        | V <sub>RO,SAT</sub>  | $V_Q < V_{RT}$ , $R_{RO}$ = 20 k $\Omega$                                              | -    | 0.1  | 0.4  | V    |  |

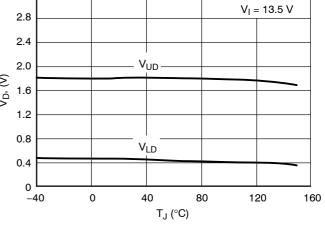

| Upper Delay Switching Threshold        | V <sub>UD</sub>      | -                                                                                      | 1.4  | 1.8  | 2.2  | V    |  |

| Lower Delay Switching Threshold        | V <sub>LD</sub>      | -                                                                                      | 0.3  | 0.45 | 0.60 | V    |  |

| Saturation Voltage on Delay Capacitor  | V <sub>D,SAT</sub>   | V <sub>Q</sub> < V <sub>RT</sub>                                                       | -    | -    | 0.1  | V    |  |

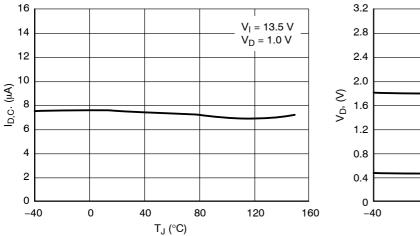

| Charge Current                         | I <sub>D,C</sub>     | V <sub>D</sub> = 1 V                                                                   | 3.0  | 6.5  | 9.5  | μΑ   |  |

| Delay Time L $\rightarrow$ H           | t <sub>d</sub>       | C <sub>D</sub> = 100 nF                                                                | 17   | 28   | -    | ms   |  |

| Delay Time $H \rightarrow L$           | t <sub>RR</sub>      | C <sub>D</sub> = 100 nF                                                                | -    | 1.0  | -    | μs   |  |

| INPUT VOLTAGE SENSE                    |                      |                                                                                        |      |      |      |      |  |

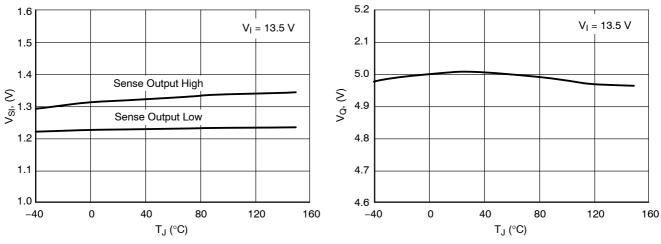

| Sense Threshold High                   | V <sub>SI,High</sub> | -                                                                                      | 1.24 | 1.31 | 1.38 | V    |  |

| Sense Threshold Low                    | V <sub>SI,Low</sub>  | _                                                                                      | 1.16 | 1.20 | 1.28 | V    |  |

| Sense Output Saturation Voltage        | V <sub>SO,Low</sub>  | $V_{SI}$ < 1.20 V; $V_Q$ > 3 V; $R_{SO}$ = 20 k $\Omega$                               | -    | 0.1  | 0.4  | V    |  |

| Concert Coursest                       |                      |                                                                                        | 10   | 0.1  | 10   |      |  |

Sense Input Current

ISI

-1.0

0.1

1.0

$\mu A$

5. Dropout voltage = V<sub>I</sub> - V<sub>Q</sub> measured when the output voltage has dropped 100 mV from the nominal value obtained at 13.5 V input.

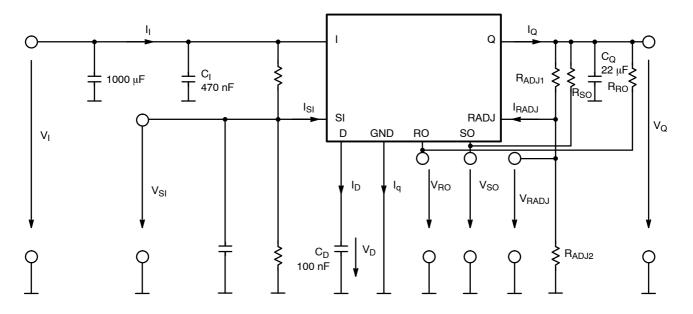

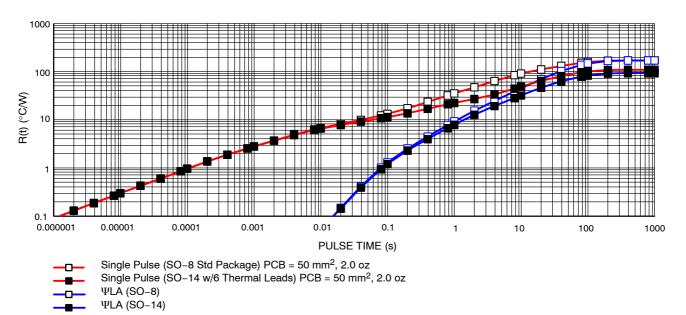

Figure 2. Measuring Circuit

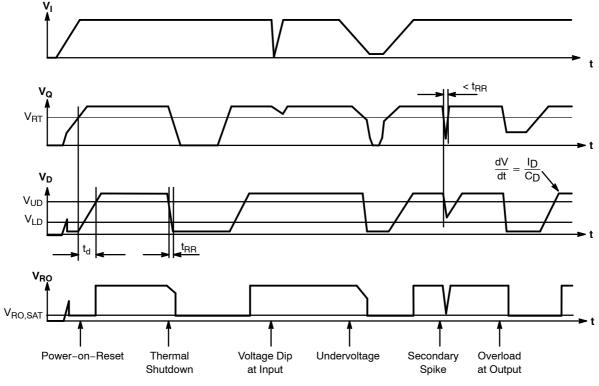

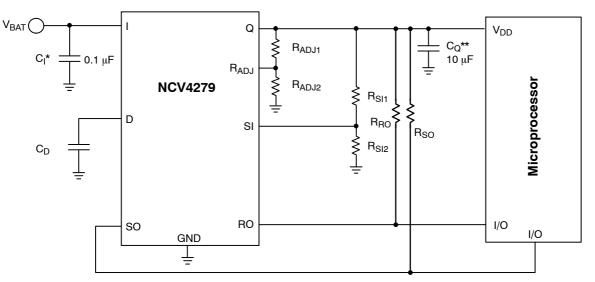

Figure 3. Reset Timing Diagram

1.7

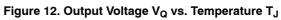

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 6. Switching Voltage  $V_{UD}$  and  $V_{LD}$  vs. Temperature  $T_{\rm J}$

Figure 7. Drop Voltage  $V_{dr}$  vs. Output Current  $I_Q$

35

30

25

20

15

10

5

I<sub>q</sub> (mA)

$R_L = 33 \Omega$

$R_I = 50 \Omega$

Figure 8. Reset Adjust Switching Threshold  $$V_{RADJ,TH}$$  vs. Temperature  $T_J$

$R_L = 200 \Omega$

## **TYPICAL PERFORMANCE CHARACTERISTICS**

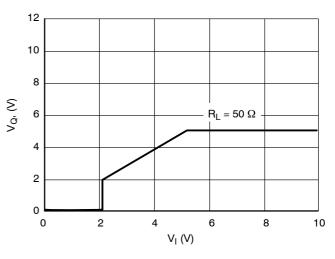

Figure 13. Output Current  ${\rm I}_{\rm Q}$  vs. Input Voltage  ${\rm V}_{\rm I}$

## **TYPICAL PERFORMANCE CHARACTERISTICS**

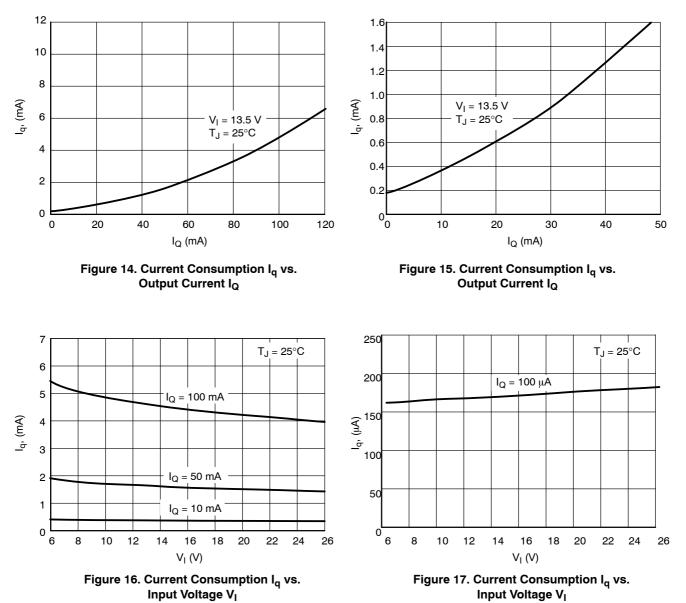

## **TYPICAL THERMAL CHARACTERISTICS**

SO-14 w/6 Thermal Leads NCV4279, 2.0 oz

Figure 19. R(t) vs. Pulse Time

### APPLICATION DESCRIPTION

#### **OUTPUT REGULATOR**

The output is controlled by a precision trimmed reference. The PNP output has drive quiescent current control for regulation while the input voltage is low, preventing over saturation. Current limit and voltage monitors complement the regulator design to give safe operating signals to the processor and control circuits.

### **RESET OUTPUT (RO)**

A reset signal, Reset Output, RO, (low voltage) is generated as the IC powers up. After the output voltage  $V_Q$ increases above the reset threshold voltage  $V_{RT}$ , the delay timer D is started. When the voltage on the delay timer  $V_D$ passes  $V_{UD}$ , the reset signal RO goes high. A discharge of the delay timer  $V_D$  is started when  $V_Q$  drops and stays below the reset threshold voltage  $V_{RT}$ . When the voltage of the delay timer  $V_D$  drops below the lower threshold voltage  $V_{LD}$ the reset output voltage  $V_{RO}$  is brought low to reset the processor.

The reset output RO is an open collector NPN transistor, controlled by a low voltage detection circuit. The circuit is functionally independent of the rest of the IC, thereby guaranteeing that RO is valid for  $V_{O}$  as low as 1.0 V.

## **RESET ADJUST (R<sub>ADJ</sub>)**

The reset threshold  $V_{RT}$  can be decreased from a typical value of 4.65 V to as low as 3.5 V by using an external voltage divider connected from the Q lead to the pin RADJ, as shown in Figure 20. The resistor divider keeps the voltage above the  $V_{RADJ,TH}$  (typical 1.35 V) for the desired input voltages, and overrides the internal threshold detector. Adjust the voltage divider according to the following relationship:

$V_{RT} = V_{RADJ,TH} \cdot (R_{ADJ1} + R_{ADJ2}) / R_{ADJ2} \qquad (eq. 1)$

If the reset adjust option is not needed, the  $R_{ADJ}$  pin should be connected to GND causing the reset threshold to go to its default value (typically 4.65 V).

### RESET DELAY (D)

The reset delay circuit provides a delay (programmable by capacitor  $C_D$ ) on the reset output lead RO. The delay lead D provides charge current  $I_{D,C}$  (typically 6.5  $\mu$ A) to the external delay capacitor  $C_D$  during the following times:

- 1. During Powerup (once the regulation threshold has been exceeded).

- 2. After a reset event has occurred and the device is back in regulation. The delay capacitor is set to discharge when the regulation ( $V_{RT}$ , reset threshold voltage) has been violated. When the delay capacitor discharges to  $V_{LD}$ , the reset signal RO pulls low.

## SETTING THE DELAY TIME

The delay time is set by the delay capacitor  $C_D$  and the charge current  $I_D$ . The time is measured by the delay capacitor voltage charging from the low level of  $V_{DSAT}$  to the higher level  $V_{UD}$ . The time delay follows the equation:

$$t_d = [C_D (V_{UD} - V_{D, SAT})]/I_D$$

(eq. 2)

Example:

Using  $C_D = 100 \text{ nF.}$

Use the typical value for  $V_{D,SAT} = 0.1$  V.

Use the typical value for  $V_{UD} = 1.8$  V.

Use the typical value for Delay Charge Current  $I_D = 6.5 \mu A$ .

$t_d = [100 \text{ nF}(1.8 - 0.1 \text{ V})]/6.5 \,\mu\text{A} = 26.2 \text{ ms}$  (eq. 3)

\*C<sub>I</sub> required if regulator is located far from the power supply filter.

\*\* C<sub>Q</sub> required for Stability. Cap must operate at minimum temperature expected.

Figure 20. Application Diagram

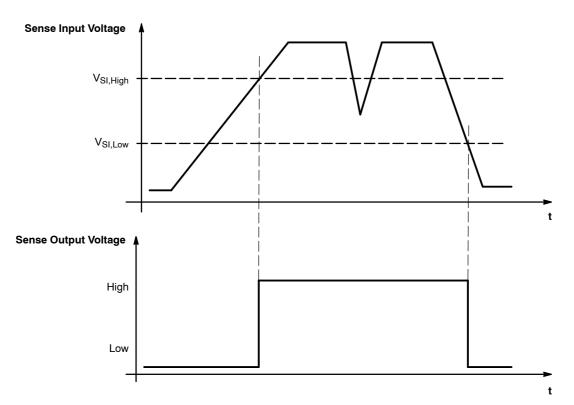

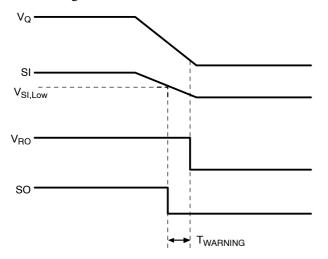

# SENSE INPUT (SI) / SENSE OUTPUT (SO) VOLTAGE MONITOR

An on-chip comparator is available to provide early warning to the microprocessor of a possible reset signal. The output is from an open collector driver. The reset signal typically turns the microprocessor off instantaneously. This can cause unpredictable results with the microprocessor. The signal received from the SO pin will allow the microprocessor time to complete its present task before shutting down. This function is performed by a comparator referenced to the band gap voltage. The actual trip point can be programmed externally using a resistor divider to the input monitor SI (Figure 20). The values for  $R_{SI1}$  and  $R_{SI2}$  are selected for a typical threshold of 1.20 V on the SI Pin.

#### SIGNAL OUTPUT

Figure 21 shows the SO Monitor timing waveforms as a result of the circuit depicted in Figure 20. As the output voltage ( $V_Q$ ) falls, the monitor threshold ( $V_{SILOW}$ ), is crossed. This causes the voltage on the SO output to go low sending a warning signal to the microprocessor that a reset signal may occur in a short period of time.  $T_{WARNING}$  is the time the microprocessor has to complete the function it is currently working on and get ready for the reset shutdown signal.

Figure 21. SO Warning Waveform Time Diagram

#### STABILITY CONSIDERATIONS

The input capacitor  $C_I$  in Figure 20 is necessary for compensating input line reactance. Possible oscillations caused by input inductance and input capacitance can be damped by using a resistor of approximately 1.0  $\Omega$  in series with  $C_L$

The output or compensation capacitor helps determine three main characteristics of a linear regulator: startup delay, load transient response and loop stability.

The capacitor value and type should be based on cost, availability, size and temperature constraints. A tantalum or aluminum electrolytic capacitor is best, since a film or ceramic capacitor with almost zero ESR can cause instability. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures ( $-25^{\circ}$ C to  $-40^{\circ}$ C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturer's data sheet usually provides this information.

The value for the output capacitor  $C_Q$  shown in Figure 20 should work for most applications; however, it is not necessarily the optimized solution. Stability is guaranteed at values  $C_Q = 10 \,\mu\text{F}$  and an ESR =  $10 \,\Omega$  within the operating temperature range. Actual limits are shown in a graph in the typical data section.

# CALCULATING POWER DISSIPATION IN A SINGLE OUTPUT LINEAR REGULATOR

The maximum power dissipation for a single output regulator (Figure 20) is:

$$PD(max) = [VI(max) - VQ(min)]IQ(max) + VI(max)Iq (eq. 4)$$

where:

V<sub>I(max)</sub> is the maximum input voltage,

V<sub>Q(min)</sub> is the minimum output voltage,

$I_{Q(max)}$  is the maximum output current for the application, and  $I_q$  is the quiescent current the regulator consumes at  $I_{Q(max)}$ .

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{0JA}$  can be calculated:

$$R_{\theta JA} = (150^{\circ}C - T_A) / P_D \qquad (eq. 5)$$

The value of  $R_{\theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C. In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required. The current flow and voltages are shown in the Measurement Circuit Diagram.

#### HEATSINKS

A heatsink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\theta JA}$ :

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CS} + R_{\theta SA} \qquad (eq. 6)$$

where:

$R_{\theta JC}$  = the junction-to-case thermal resistance,

$R_{\theta CS}$  = the case-to-heat sink thermal resistance, and  $R_{\theta SA}$  = the heat sink-to-ambient thermal resistance.

$R_{\theta JC}$  appears in the package section of the data sheet. Like  $R_{\theta IA}$ , it too is a function of package type.  $R_{\theta CS}$  and  $R_{\theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in data sheets of heatsink manufacturers. Thermal, mounting, and heatsinking considerations are discussed the in ON Semiconductor application note AN1040/D, available on the ON Semiconductor website.

#### **ORDERING INFORMATION**

| Device       | Output Voltage | Package            | Shipping <sup>†</sup> |

|--------------|----------------|--------------------|-----------------------|

| NCV4279D1G   |                | SO-8<br>(Pb-Free)  | 98 Units/Rail         |

| NCV4279D1R2G |                | SO-8<br>(Pb-Free)  | 2500 Tape & Reel      |

| NCV4279D2G   | 5.0 V          | SO-14<br>(Pb-Free) | 55 Units/Rail         |

| NCV4279D2R2G |                | SO-14<br>(Pb-Free) | 2500 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

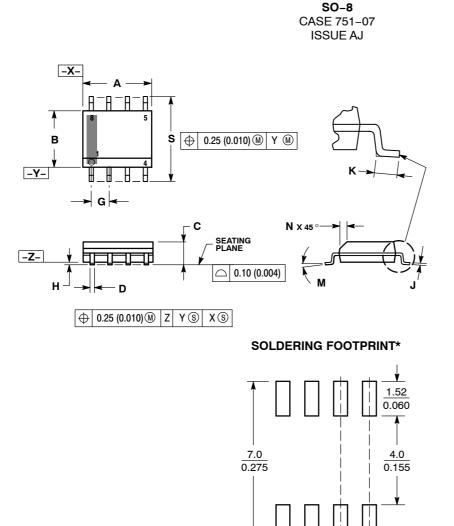

#### PACKAGE DIMENSIONS

0.6

0.024

- NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIN   | IETERS | INC       | HES   |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 4.80     | 5.00   | 0.189     | 0.197 |

| в   | 3.80     | 4.00   | 0.150     | 0.157 |

| С   | 1.35     | 1.75   | 0.053     | 0.069 |

| D   | 0.33     | 0.51   | 0.013     | 0.020 |

| G   | 1.27 BSC |        | 0.050 BSC |       |

| н   | 0.10     | 0.25   | 0.004     | 0.010 |

| J   | 0.19     | 0.25   | 0.007     | 0.010 |

| к   | 0.40     | 1.27   | 0.016     | 0.050 |

| м   | 0 °      | 8 °    | 0 °       | 8 °   |

| Ν   | 0.25     | 0.50   | 0.010     | 0.020 |

| S   | 5.80     | 6.20   | 0.228     | 0.244 |

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

1.270

0.050

SCALE 6:1

$\left(\frac{mm}{inches}\right)$

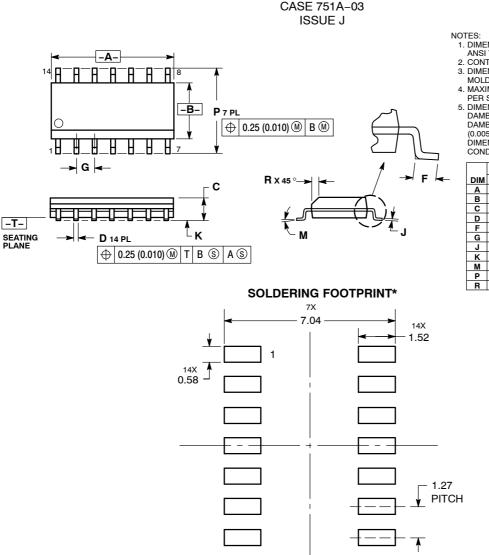

#### PACKAGE DIMENSIONS

SOIC-14

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN   | IETERS | INCHES    |       |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 8.55     | 8.75   | 0.337     | 0.344 |

| в   | 3.80     | 4.00   | 0.150     | 0.157 |

| С   | 1.35     | 1.75   | 0.054     | 0.068 |

| D   | 0.35     | 0.49   | 0.014     | 0.019 |

| F   | 0.40     | 1.25   | 0.016     | 0.049 |

| G   | 1.27 BSC |        | 0.050 BSC |       |

| J   | 0.19     | 0.25   | 0.008     | 0.009 |

| к   | 0.10     | 0.25   | 0.004     | 0.009 |

| м   | 0 °      | 7 °    | 0 °       | 7 °   |

| Р   | 5.80     | 6.20   | 0.228     | 0.244 |

| R   | 0.25     | 0.50   | 0.010     | 0.019 |

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability, arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use payers and reasonable attorney fees and is not for seale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative