# FLEXMOS<sup>™</sup> Hex Low-Side MOSFET Pre-Driver

The NCV7517B programmable six channel low-side MOSFET pre-driver is one of a family of FLEXMOS<sup>TM</sup> automotive grade products for driving logic-level MOSFETs. The product is controllable by a combination of serial SPI and parallel inputs. It features programmable fault management modes and allows power-limiting PWM operation with programmable refresh time. The device offers 3.3 V/5.0 V compatible inputs and the serial output driver can be powered from either 3.3 V or 5.0 V. Power-on reset provides controlled powerup and two enable inputs allow all outputs to be simultaneously disabled.

Each channel independently monitors its external MOSFET's drain voltage for fault conditions. Shorted load fault detection thresholds are fully programmable using an externally programmed reference voltage and a combination of four discrete internal ratio values. The ratio values are SPI selectable and allow different detection thresholds for each group of three output channels.

Fault information for each channel is 2-bit encoded by fault type and is available through SPI communication. Fault recovery operation for each channel is programmable and may be selected for latch-off or automatic retry.

The FLEXMOS family of products offers application scalability through choice of external MOSFETs.

## Features

- 16-Bit SPI with Frame Error Detection

- 3.3 V/5.0 V Compatible Parallel and Serial Control Inputs

- 3.3 V/5.0 V Compatible Serial Output Driver

- Two Enable Inputs

- Open–Drain Fault and Status Flags

- Programmable

- Shorted Load Fault Detection Thresholds

- Fault Recovery Mode

- Fault Retry Timer

- Flag Masking

- Load Diagnostics with Latched Unique Fault Type Data

- Shorted Load

- Open Load

- Short to GND

- NCV Prefix for Automotive and Other Applications Requiring Site and Change Controls

- These are Pb–Free Devices\*

## **Benefits**

• Scalable to Load by Choice of External MOSFET

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **ON Semiconductor®**

http://onsemi.com

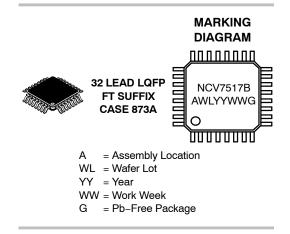

## **ORDERING INFORMATION**

| Device        | Package           | Shipping†        |

|---------------|-------------------|------------------|

| NCV7517BFTG   | LQFP<br>(Pb-Free) | 250 Units/Tray   |

| NCV7517BFTR2G | LQFP<br>(Pb-Free) | 2000 Tape & Reel |

<sup>+</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

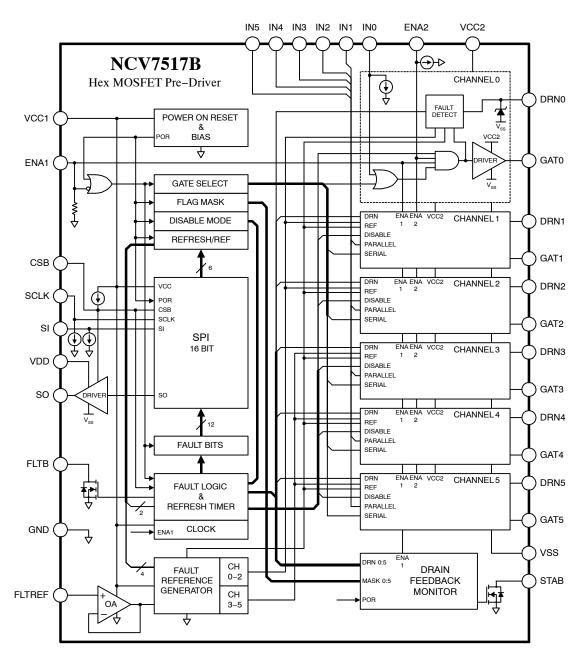

Figure 1. Block Diagram

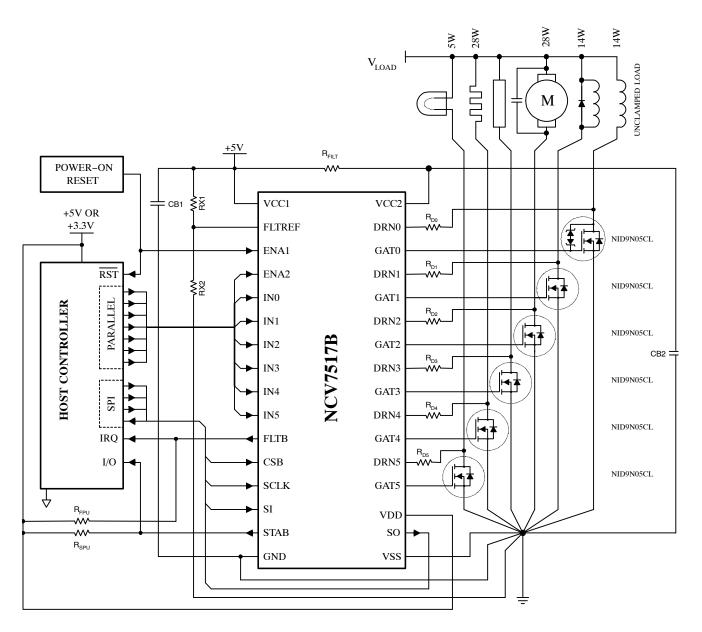

Figure 2. Application Diagram

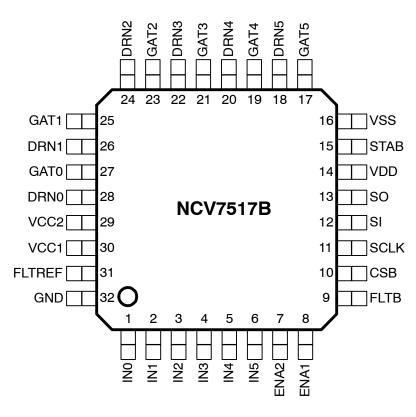

## PIN FUNCTION DESCRIPTION

| Symbol      | Description                                                |

|-------------|------------------------------------------------------------|

| FLTREF      | Analog Fault Detect Threshold: 5.0 V Compliant             |

| DRN0 – DRN5 | Analog Drain Feedback: Internally Clamped                  |

| GAT0 – GAT5 | Analog Gate Drive: 5.0 V Compliant                         |

| ENA1, ENA2  | Digital Master Enable Inputs: 3.3 V/5.0 V (TTL) Compatible |

| IN0 – IN5   | Digital Parallel Input: 3.3 V/5.0 V (TTL) Compatible       |

| CSB         | Digital Chip Select Input: 3.3 V/5.0 V (TTL) Compatible    |

| SCLK        | Digital Shift Clock Input: 3.3 V/5.0 V (TTL) Compatible    |

| SI          | Digital Serial Data Input: 3.3 V/5.0 V (TTL) Compatible    |

| SO          | Digital Serial Data Output: 3.3 V/5.0 V Compliant          |

| STAB        | Digital Open-Drain Output: 3.3 V/5.0 V Compliant           |

| FLTB        | Digital Open-Drain Output: 3.3 V/5.0 V Compliant           |

| VCC1        | Power Supply – Low Power Path                              |

| GND         | Power Return – Low Power Path – Device Substrate           |

| VCC2        | Power Supply – Gate Drivers                                |

| VDD         | Power Supply – Serial Output Driver                        |

| VSS         | Power Return – VCC2, VDD, Drain Clamps                     |

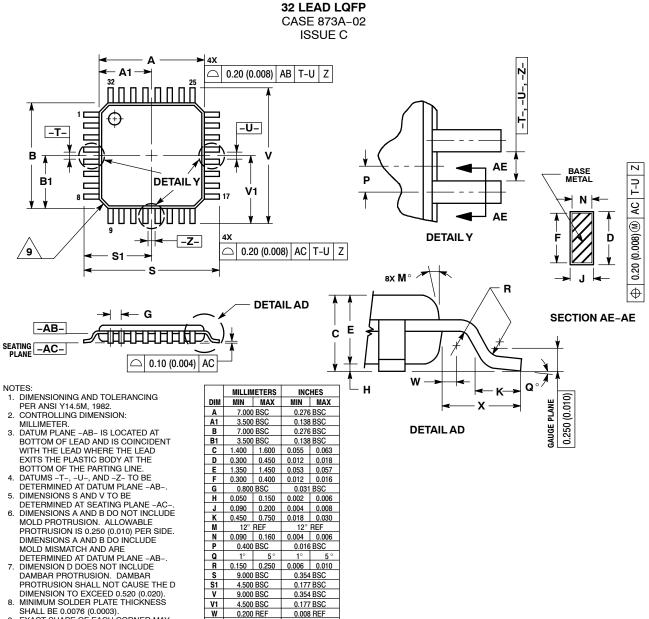

Figure 3. 32 Pin LQFP Pinout (Top View)

## MAXIMUM RATINGS (Voltages are with respect to device substrate.)

| Rating                                                                              | Value       | Unit |

|-------------------------------------------------------------------------------------|-------------|------|

| DC Supply (V <sub>CC1</sub> , V <sub>CC2</sub> , V <sub>DD</sub> )                  | -0.3 to 6.5 | V    |

| Difference Between $V_{CC1}$ and $V_{CC2}$                                          | ±0.3        | V    |

| Difference Between GND (Substrate) and $V_{SS}$                                     | ±0.3        | V    |

| Output Voltage (Any Output)                                                         | -0.3 to 6.5 | V    |

| Drain Feedback Clamp Voltage (Note 1)                                               | -0.3 to 47  | V    |

| Drain Feedback Clamp Current (Note 1)                                               | 10          | mA   |

| Input Voltage (Any Input)                                                           | -0.3 to 6.5 | V    |

| Junction Temperature, T <sub>J</sub>                                                | -40 to 150  | °C   |

| Storage Temperature, T <sub>STG</sub>                                               | -65 to 150  | °C   |

| Peak Reflow Soldering Temperature: Lead–Free<br>60 to 150 seconds at 217°C (Note 2) | 260 peak    | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## ATTRIBUTES

| Characteristic                                                                                          | Value                  |

|---------------------------------------------------------------------------------------------------------|------------------------|

| ESD Capability<br>Human Body Model<br>Machine Model                                                     |                        |

| Moisture Sensitivity (Note 2)                                                                           | MSL3                   |

| Package Thermal Resistance (Note 3) Junction–to–Ambient, $R_{\theta JA}$ Junction–to–Pin, $R_{\Psi JL}$ | 86.0 °C/W<br>58.5 °C/W |

1. An external series resistor must be connected between the MOSFET drain and the feedback input in the application. Total clamp power dissipation is limited by the maximum junction temperature, the application environment temperature, and the package thermal resistances.

2. For additional information, see or download ON Semiconductor's Soldering and Mounting Techniques Reference Manual, SOLDERRM/D, and Application Note AND8003/D.

Values represent still air steady-state thermal performance on a 4 layer (42 x 42 x 1.5 mm) PCB with 1 oz. copper on an FR4 substrate, using a minimum width signal trace pattern (384 mm<sup>2</sup> trace area).

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol               | Parameter                                 | Min                    | Max                    | Unit |

|----------------------|-------------------------------------------|------------------------|------------------------|------|

| V <sub>CC1</sub>     | Main Power Supply Voltage                 | 4.75                   | 5.25                   | V    |

| V <sub>CC2</sub>     | Gate Drivers Power Supply Voltage         | V <sub>CC1</sub> – 0.3 | V <sub>CC1</sub> + 0.3 | V    |

| V <sub>DD</sub>      | Serial Output Driver Power Supply Voltage | 3.0                    | V <sub>CC1</sub>       | V    |

| V <sub>IN</sub> High | Logic High Input Voltage                  | 2.0                    | V <sub>CC1</sub>       | V    |

| V <sub>IN</sub> Low  | Logic Low Input Voltage                   | 0                      | 0.8                    | V    |

| T <sub>A</sub>       | Ambient Still-Air Operating Temperature   | -40                    | 125                    | °C   |

| Characteristic                                                                | Symbol          | Conditions                                                                    | Min                       | Тур                       | Max                       | Unit                    |

|-------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------------------------|

| V <sub>CC1</sub> Supply                                                       |                 |                                                                               |                           |                           |                           |                         |

| Operating Current –<br>V <sub>CC1</sub> = 5.25 V, V <sub>FLTREF</sub> = 1.0 V |                 |                                                                               |                           | 2.80<br>3.10              | 5.0<br>5.0                | mA                      |

|                                                                               |                 | $ENA_1 = ENA_2 = V_{CC1},$<br>$GAT_X$ drivers on                              | _                         | 2.80                      | 5.0                       |                         |

| Power-On Reset Threshold                                                      |                 | V <sub>CC1</sub> Rising                                                       | 3.65                      | 4.20                      | 4.60                      | V                       |

| Power–On Reset Hysteresis                                                     |                 | -                                                                             | 0.150                     | 0.385                     | -                         | V                       |

| Digital I/O                                                                   |                 |                                                                               |                           |                           |                           |                         |

| V <sub>IN</sub> High                                                          |                 | ENA <sub>X</sub> , IN <sub>X</sub> , SI, SCLK, CSB                            | 2.0                       | -                         | -                         | V                       |

| V <sub>IN</sub> Low                                                           |                 | ENA <sub>X</sub> , IN <sub>X</sub> , SI, SCLK, CSB                            | —                         | -                         | 0.8                       | V                       |

| V <sub>IN</sub> Hysteresis                                                    |                 | ENA <sub>X</sub> , IN <sub>X</sub> , SI, SCLK, CSB                            | 100                       | 330                       | 500                       | mV                      |

| Input Pullup Current                                                          |                 | CSB V <sub>IN</sub> = 0 V                                                     | -25                       | -10                       | -                         | μA                      |

| Input Pulldown Current                                                        |                 | ENA2, IN <sub>X</sub> , SI, SCLK, $V_{IN} = V_{CC1}$                          | _                         | 10                        | 25                        | μΑ                      |

| Input Pulldown Resistance                                                     |                 | ENA1                                                                          | 100                       | 150                       | 200                       | kΩ                      |

| SO Low Voltage                                                                |                 | V <sub>DD</sub> = 3.3 V, I <sub>SINK</sub> = 5.0 mA                           | -                         | 0.11                      | 0.25                      | V                       |

| SO High Voltage                                                               |                 | V <sub>DD</sub> = 3.3 V, I <sub>SOURCE</sub> = 5.0 mA                         | V <sub>DD</sub> –<br>0.25 | V <sub>DD</sub> -<br>0.11 | -                         | V                       |

| SO Output Resistance                                                          |                 | Output High or Low                                                            | -                         | 22                        | -                         | Ω                       |

| SO Tri-State Leakage Current                                                  |                 | CSB = 3.3 V                                                                   | -10                       | -                         | 10                        | μA                      |

| STAB Low Voltage                                                              |                 | STAB Active, I <sub>STAB</sub> = 1.25 mA                                      | -                         | 0.1                       | 0.25                      | V                       |

| STAB Leakage Current                                                          |                 | $V_{STAB} = V_{CC1}$                                                          | _                         | -                         | 10                        | μA                      |

| FLTB Low Voltage                                                              |                 | FLTB Active, I <sub>FLTB</sub> = 1.25 mA                                      | —                         | 0.1                       | 0.25                      | V                       |

| FLTB Leakage Current                                                          |                 | $V_{FLTB} = V_{CC1}$                                                          | _                         | -                         | 10                        | μA                      |

| Fault Detection – GAT <sub>X</sub> ON                                         |                 |                                                                               |                           |                           |                           |                         |

| FLTREF Input Current                                                          |                 | V <sub>FLTREF</sub> = 0 V                                                     | -1.0                      | -                         | -                         | μA                      |

| FLTREF Input Linear Range                                                     |                 | (Note 5)                                                                      | 0                         | -                         | V <sub>CC1</sub> -<br>2.0 | V                       |

| FLTREF Op-amp V <sub>CC1</sub> PSRR                                           |                 | (Note 5)                                                                      | 30                        | -                         | -                         | dB                      |

| DRN <sub>X</sub> Clamp Voltage                                                | V <sub>CL</sub> | I <sub>DRNX</sub> = 10 μA<br>I <sub>DRNX</sub> = I <sub>CL(MAX)</sub> = 10 mA | 27                        | 34<br>42                  | 47                        | V                       |

| DRN <sub>X</sub> Shorted Load Threshold                                       |                 | Register 2: $R_1 = 0$ , $R_0 = 0$ or<br>$R_4 = 0$ , $R_3 = 0$                 | 20                        | 25                        | 30                        | %<br>V <sub>FLTRE</sub> |

| GAT <sub>X</sub> Output High<br>V <sub>FLTREF</sub> = 1.0 V                   |                 | Register 2: $R_1 = 0$ , $R_0 = 1$ or<br>$R_4 = 0$ , $R_3 = 1$                 | 45                        | 50                        | 55                        | %<br>V <sub>FLTRE</sub> |

|                                                                               |                 | Register 2: $R_1 = 1$ , $R_0 = 0$ or<br>$R_4 = 1$ , $R_3 = 0$                 | 70                        | 75                        | 80                        | %<br>V <sub>FLTRE</sub> |

|                                                                               |                 | Register 2: $R_1 = 1$ , $R_0 = 1$ or $R_4 = 1$ , $R_3 = 1$                    | 95                        | 100                       | 105                       | %<br>V <sub>FLTRE</sub> |

| DRN <sub>X</sub> Input Leakage Current                                        |                 |                                                                               | -1.0                      | -                         | 1.0                       | μΑ                      |

Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100% parametrically tested in production.

Guaranteed by design.

**ELECTRICAL CHARACTERISTICS (continued)** (4.75 V  $\leq$  V<sub>CCX</sub>  $\leq$  5.25 V, V<sub>DD</sub> = V<sub>CCX</sub>, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, unless otherwise specified.) (Note 6)

| Characteristic                                  | Symbol                                    | Conditions                                                                      | Min    | Тур | Max   | Unit              |

|-------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------|--------|-----|-------|-------------------|

| Fault Detection – GAT <sub>X</sub> OFF          |                                           |                                                                                 |        |     |       |                   |

| DRN <sub>X</sub> Diagnostic Current             | I <sub>SG</sub>                           | Short to GND Detection,<br>$V_{DRNX} = 0.30 V_{CC1}$                            | -27    | -20 | -10   | μΑ                |

|                                                 | I <sub>OL</sub>                           | Open Load Detection,<br>$V_{DRNX} = 0.75 V_{CC1}$                               | 30     | 60  | 80    | μΑ                |

| DRN <sub>X</sub> Fault Threshold Voltage        | V <sub>SG</sub>                           | V <sub>SG</sub> Short to GND Detection                                          |        | 30  | 33    | %V <sub>CC1</sub> |

|                                                 | V <sub>OL</sub>                           | Open Load Detection                                                             | 72     | 75  | 78    | %V <sub>CC1</sub> |

| DRN <sub>X</sub> Off State Bias Voltage         | V <sub>CTR</sub>                          | -                                                                               | -      | 50  | -     | %V <sub>CC1</sub> |

| Gate Driver Outputs                             |                                           |                                                                                 |        |     |       |                   |

| GAT <sub>X</sub> Output Resistance              |                                           | Output High or Low                                                              | 200    | 350 | 500   | Ω                 |

| GAT <sub>X</sub> High Output Current            |                                           | V <sub>GATX</sub> = 0 V                                                         | -26.25 | _   | -9.5  | mA                |

| GAT <sub>X</sub> Low Output Current             |                                           | V <sub>GATX</sub> = V <sub>CC2</sub>                                            | 9.5    | _   | 26.25 | mA                |

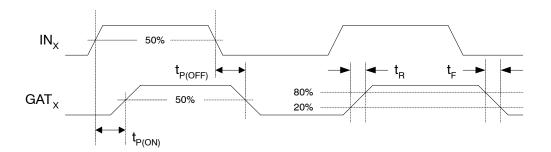

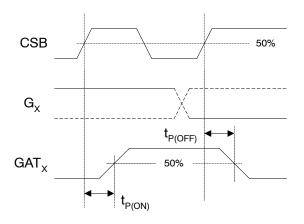

| Turn–On Propagation Delay                       | t <sub>P(ON)</sub>                        | IN <sub>X</sub> to GAT <sub>X</sub> (Figure 4)                                  |        |     | 1.0   | μs                |

|                                                 |                                           | CSB to GAT <sub>X</sub> (Figure 5)                                              | —      | -   |       |                   |

| Turn–Off Propagation Delay                      | t <sub>P(OFF)</sub>                       | IN <sub>X</sub> to GAT <sub>X</sub> (Figure 4)                                  |        |     | 1.0   | μs                |

|                                                 |                                           | CSB to GAT <sub>X</sub> (Figure 5)                                              | —      | -   |       |                   |

| Output Rise Time                                | t <sub>R</sub>                            | 20% to 80% of V <sub>CC2</sub> ,                                                | _      | -   | 277   | ns                |

|                                                 |                                           | C <sub>LOAD</sub> = 400 pF                                                      |        |     |       |                   |

|                                                 |                                           | (Figure 4, Note 5)                                                              |        |     |       |                   |

| Output Fall Time                                | t <sub>F</sub>                            | 80% to 20% of $V_{CC2},$                                                        | _      | -   | 277   | ns                |

|                                                 |                                           | C <sub>LOAD</sub> = 400 pF                                                      |        |     |       |                   |

|                                                 |                                           | (Figure 4, Note 5)                                                              |        |     |       |                   |

| Fault Timers                                    |                                           |                                                                                 |        |     |       |                   |

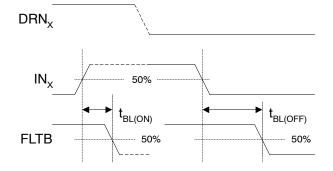

| Channel Fault Blanking Timer                    | t <sub>BL(ON)</sub>                       | V <sub>DRNX</sub> = 5.0 V; IN <sub>X</sub> rising to<br>FLTB falling (Figure 6) | 11     | 21  | 31    | μs                |

|                                                 | t <sub>BL(OFF)</sub>                      | V <sub>DRNX</sub> = 0 V; IN <sub>X</sub> falling to<br>FLTB falling (Figure 6)  | 90     | 120 | 150   | μs                |

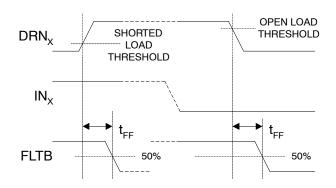

| Channel Fault Filter Timer                      | t <sub>FF</sub>                           | Figure 7                                                                        | 7.0    | 12  | 17    | μs                |

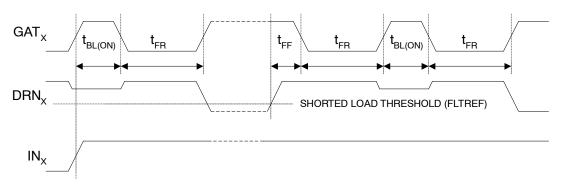

| Global Fault Refresh Timer                      | t <sub>FR</sub>                           | Register 2: Bit $R_2 = 0$ or $R_5 = 0$                                          | 7.5    | 10  | 12.5  | ms                |

| (Auto-retry Mode)                               |                                           | Register 2: Bit $R_2 = 1$ or $R_5 = 1$                                          | 30     | 40  | 50    | ms                |

| Timer Clock                                     |                                           | ENA1 = 1                                                                        | _      | 500 | _     | kHz               |

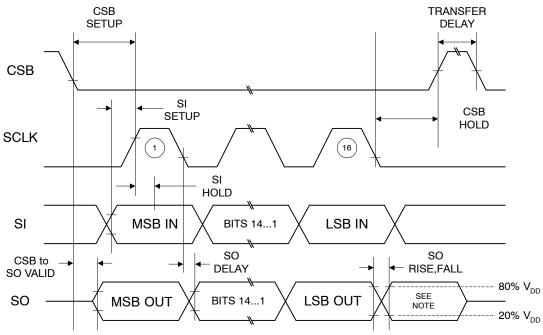

| Serial Peripheral Interface (Figure 9) $V_{cc}$ | <sub>x</sub> = 5.0 V, V <sub>DD</sub> = 3 | 8.3 V, F <sub>SCLK</sub> = 4.0 MHz, C <sub>LOAD</sub> = 20                      | 00 pF  |     |       |                   |

| SO Supply Voltage                               | V <sub>DD</sub>                           | 3.3 V Interface                                                                 | 3.0    | 3.3 | 3.6   | V                 |

|                                                 |                                           | 5.0 V Interface                                                                 | 4.5    | 5.0 | 5.5   | V                 |

| SCLK Clock Period                               |                                           | -                                                                               | _      | 250 | -     | ns                |

| Maximum Input Capacitance                       |                                           | SI, SCLK (Note 7)                                                               | _      | _   | 12    | pF                |

| SCLK High Time                                  |                                           | SCLK = 2.0 V to 2.0 V                                                           | 125    | -   | _     | ns                |

| SCLK Low Time                                   |                                           | SCLK = 0.8 V to 0.8 V                                                           | 125    | -   | -     | ns                |

| SI Setup Time                                   |                                           | SI = 0.8 V/2.0 V to<br>SCLK = 2.0 V (Note 7)                                    | 25     | _   | _     | ns                |

| SI Hold Time                                    |                                           | SCLK = 2.0 V to<br>SI = 0.8 V/2.0 V (Note 7)                                    | 25     | _   | _     | ns                |

Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100% parametrically tested in production.

Guaranteed by design.

**ELECTRICAL CHARACTERISTICS (continued)** (4.75 V  $\leq$  V<sub>CCX</sub>  $\leq$  5.25 V, V<sub>DD</sub> = V<sub>CCX</sub>, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, unless otherwise specified.) (Note 8)

| Characteristic                                                                                                                    | Symbol | Conditions                                                                           | Min | Тур | Max | Unit |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| Serial Peripheral Interface (continued) (Figure 9) $V_{ccx}$ = 5.0 V, $V_{DD}$ = 3.3 V, $F_{SCLK}$ = 4.0 MHz, $C_{LOAD}$ = 200 pF |        |                                                                                      |     |     |     |      |  |  |  |

| SO Rise Time                                                                                                                      |        | (20% V <sub>SO</sub> to 80% V <sub>DD</sub> )<br>C <sub>LOAD</sub> = 200 pF (Note 9) | -   | 25  | 50  | ns   |  |  |  |

| SO Fall Time                                                                                                                      |        | (80% V <sub>SO</sub> to 20% V <sub>DD</sub> )<br>C <sub>LOAD</sub> = 200 pF (Note 9) | _   | -   | 50  | ns   |  |  |  |

| CSB Setup Time                                                                                                                    |        | CSB = 0.8 V to SCLK = 2.0 V<br>(Note 9)                                              | 60  | _   | -   | ns   |  |  |  |

| CSB Hold Time                                                                                                                     |        | SCLK = 0.8 V to CSB = 2.0 V<br>(Note 9)                                              | 75  | -   | -   | ns   |  |  |  |

| CSB to SO Time                                                                                                                    |        | CSB = 0.8 V to SO Data Valid<br>(Note 9)                                             | -   | 65  | 125 | ns   |  |  |  |

| SO Delay Time                                                                                                                     |        | SCLK = 0.8 V to SO Data Valid<br>(Note 9)                                            | —   | 65  | 125 | ns   |  |  |  |

| Transfer Delay Time                                                                                                               |        | CSB Rising Edge to Next<br>Falling Edge (Note 9)                                     | 1.0 | -   | -   | μs   |  |  |  |

8. Designed to meet these characteristics over the stated voltage and temperature recommended operating ranges, though may not be 100% parametrically tested in production.9. Guaranteed by design.

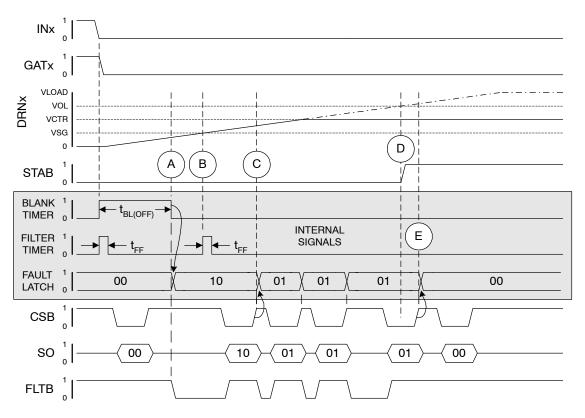

Figure 7. Filter Timing Diagram

Figure 8. Fault Refresh Timing Diagram

Note: Not defined but usually MSB of data just received.

Figure 9. SPI Timing Diagram

## DETAILED OPERATING DESCRIPTION

## General

The NCV7517B is a six channel general purpose low-side pre-driver for controlling and protecting N-type logic level MOSFETs. While specifically designed for driving MOSFETs with resistive, inductive or lamp loads in automotive applications, the device is also suitable for industrial and commercial applications. Programmable fault detection and protection modes allow the NCV7517B to accommodate a wide range of external MOSFETs and loads, providing the user with flexible application solutions. Separate power supply pins are provided for low and high current paths to improve analog accuracy and digital signal integrity. ON Semiconductor's SMARTDISCRETES<sup>TM</sup> clamp MOSFETs, such as the NID9N05CL, are recommended when driving unclamped inductive loads.

## **Power Up/Down Control**

The NCV7517B's powerup/down control prevents spurious output operation by monitoring the  $V_{CC1}$  power supply. An internal Power–On Reset (POR) circuit causes all GAT<sub>X</sub> outputs to be held low until sufficient voltage is available to allow proper control of the device. All internal registers are initialized to their default states, fault data is cleared, and the open–drain fault (FLTB) and status (STAB) flags are disabled.

When  $V_{CC1}$  exceeds the POR threshold, outputs and flags are enabled and the device is ready to accept input data. When  $V_{CC1}$  falls below the POR threshold during power down, flags are reset and disabled and all GAT<sub>X</sub> outputs are driven and held low until  $V_{CC1}$  falls below about 0.7 V.

## **SPI Communication**

The NCV7517B is a 16-bit SPI slave device. SPI communication between the host and the NCV7517B may either be parallel via individual CSB addressing or daisy-chained through other devices using a compatible SPI protocol.

The active–low CSB chip select input has a pullup current source. The SI and SCLK inputs have pulldown current sources. The recommended idle state for SCLK is low. The tri–state SO line driver can be supplied with either 3.3 or 5.0 V and is powered via the device's  $V_{DD}$  and  $V_{SS}$  pins.

The NCV7517B employs frame error detection that requires integer multiples of 16 SCLK cycles during each CSB high-low-high cycle (valid communication frame.) A frame error does not affect the flags. The CSB input controls SPI data transfer and initializes the selected device's frame error and fault reporting logic.

The host initiates communication when a selected device's CSB pin goes low. Output (fault) data is simultaneously sent MSB first from the SO pin while input (command) data is received MSB first at the SI pin under synchronous control of the master's SCLK signal while CSB is held low (Figure 10). Fault data changes on the falling edge of SCLK and is guaranteed valid before the next rising edge of SCLK. Command data received must be valid before the rising edge of SCLK.

When CSB goes low, frame error detection is initialized, latched fault data is transferred to the SPI, and the FLTB flag is disabled and reset if previously set. Data for faults detected while CSB is low are ignored but will be captured if still present after CSB goes high.

If a valid frame has been received when CSB goes high, the last multiple of 16 bits received is decoded into command data, and FLTB is re-enabled. Latched (previous) fault data is cleared and current fault data is captured. The FLTB flag will be set if a fault is detected.

If a frame error is detected when CSB goes high, new command data is ignored, and previous fault data remains latched and available for retrieval during the next valid frame. The FLTB flag will be set if a fault (not a frame error) is detected.

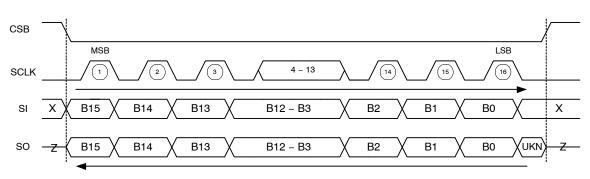

Note: X=Don't Care, Z=Tri-State, UKN=Unknown Data

#### Figure 10. SPI Communication Frame Format

## Serial Data and Register Structure

The 16-bit data sent by the NCV7517B is always the encoded 12-bit fault information, with the upper 4 bits forced to zero. The 16-bit data received is decoded into a 4-bit address and a 6-bit data word (see Figure 11). The upper four bits, beginning with the received MSB, are fully decoded to address one of four programmable registers and the lower six bits are decoded into data for the addressed register. Bit B15 must always be set to zero. The valid register addresses are shown in Table 1. Each register is next described in detail.

| B15     B14     B13     B12     B11     B10     B9     B8     B7     B6     B5     B4     B3     B2     B1     B0       0     0     0     0     CH5     CH4     CH3     CH2     CH1     CH0       CHANNEL FAULT OUTPUT DATA       REGISTER SELECT       MSB     COMMAND INPUT DATA       LSB       B15     B14     B13     B12     B11     B10     B9     B8     B7     B6     B5     B4     B3     B2     B1     CH0 | MSB                       |       |     |     |     |     |    |    |    |     |    |      |    |     |      | LSB |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|-----|-----|-----|-----|----|----|----|-----|----|------|----|-----|------|-----|

| CHANNEL FAULT OUTPUT DATA       REGISTER SELECT     COMMAND INPUT DATA       MSB     LSB       B15     B14     B13     B12     B11     B10     B9     B8     B7     B6     B5     B4     B3     B2     B1     B0                                                                                                                                                                                                      | B15                       | B14   | B13 | B12 | B11 | B10 | B9 | B8 | B7 | B6  | B5 | B4   | B3 | B2  | B1   | B0  |

| REGISTER SELECT     COMMAND INPUT DATA       MSB                                                                                                                                                                                                                                                                                                                                                                      | 0                         | 0     | 0   | 0   | Cł  | -15 | CI | 4  | CI | -13 | Cł | H2   | Cł | -11 | CI   | 10  |

| MSB LSB                                                                                                                                                                                                                                                                                                                                                                                                               | CHANNEL FAULT OUTPUT DATA |       |     |     |     |     |    |    |    |     |    |      |    |     |      |     |

| B15     B14     B13     B12     B11     B10     B9     B8     B7     B6     B5     B4     B3     B2     B1     B0                                                                                                                                                                                                                                                                                                     | REG                       | ISTER |     | ECT |     |     |    |    |    |     | (  | СОММ |    |     | DATA |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                       | ( <sub>MSB</sub>          |       |     | )   | I   |     |    |    |    |     | ſ  |      |    |     |      | LSB |

| 0 A2 A1 A0 X X X X X D5 D4 D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                                                                                | B15                       | B14   | B13 | B12 | B11 | B10 | B9 | B8 | B7 | B6  | B5 | B4   | B3 | B2  | B1   | B0  |

|                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                         | A2    | A1  | A0  | х   | х   | Х  | х  | Х  | х   | D5 | D4   | D3 | D2  | D1   | D0  |

Figure 11. SPI Data Format

|                 | 4-BIT AI        | DDRESS          |                 | 6–BIT INPUT DATA                                                                          |                     |        |        |  |  |  |

|-----------------|-----------------|-----------------|-----------------|-------------------------------------------------------------------------------------------|---------------------|--------|--------|--|--|--|

| B <sub>15</sub> | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  | D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |                     |        |        |  |  |  |

| 0               | 0               | 0               | 0               | Gate Select                                                                               |                     |        |        |  |  |  |

| 0               | 0               | 0               | 1               |                                                                                           |                     | Disabl | e Mode |  |  |  |

| 0               | 0               | 1               | 0               |                                                                                           | Refresh & Reference |        |        |  |  |  |

| 0               | 0               | 1               | 1               |                                                                                           |                     | Flag   | Mask   |  |  |  |

| 0               | 1               | Х               | Х               |                                                                                           |                     | N      | lull   |  |  |  |

|                 | •               | •               |                 | 16-BIT OL                                                                                 | JTPUT DATA          |        |        |  |  |  |

| B <sub>15</sub> | B <sub>14</sub> | B <sub>13</sub> | B <sub>12</sub> | B <sub>11</sub> B <sub>0</sub>                                                            |                     |        |        |  |  |  |

| 0               | 0               | 0               | 0               | D <sub>11</sub> 12-bit Fault Data D <sub>0</sub>                                          |                     |        |        |  |  |  |

## Table 1. Register Address Definitions

## Gate Select – Register 0

Each GAT<sub>X</sub> output is turned on/off by programming its respective  $G_X$  bit (see Table 2). Setting a bit to 1 causes the selected GAT<sub>X</sub> output to drive its external MOSFET's gate to V<sub>CC2</sub> (ON). Setting a bit to 0 causes the selected GAT<sub>X</sub> output to drive its external MOSFET's gate to V<sub>SS</sub> (OFF). Note that the actual state of the output depends on POR, ENA<sub>X</sub> and shorted load fault states as later defined by Equation 1. At powerup, each bit is set to 0 (all outputs OFF).

## Table 2. Gate Select Register

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub>                            | $D_2$          | D <sub>1</sub> | D <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|-------------------------------------------|----------------|----------------|----------------|

| 0              | 0              | 0              | G <sub>5</sub> | G <sub>4</sub> | G <sub>3</sub>                            | G <sub>2</sub> | G <sub>1</sub> | G <sub>0</sub> |

|                |                |                |                |                | aat <sub>x</sub> oi<br>At <sub>x</sub> oi |                |                |                |

## Disable Mode – Register 1

The disable mode for shorted load faults is controlled by each channel's respective  $M_X$  bit (see Table 3). Setting a bit

to 1 causes the selected  $GAT_X$  output to latch-off when a fault is detected. Setting a bit to 0 causes the selected  $GAT_X$  output to auto-retry when a fault is detected. At powerup, each bit is set to 0 (all outputs in auto-retry mode).

## Table 3. Disable Mode Register

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub>  | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|

| 0              | 0              | 1              | M <sub>5</sub> | M4             | M <sub>3</sub>  | M <sub>2</sub> | M <sub>1</sub> | M <sub>0</sub> |

|                |                |                |                |                | UTO-F<br>ATCH ( |                |                |                |

## **Refresh and Reference – Register 2**

Refresh time (auto-retry mode) and shorted load fault detection references are programmable in two groups of three channels. Refresh time and the fault reference for channels 5–3 is programmed by  $R_X$  bits 5–3. Refresh time and the fault reference for channels 2–0 is programmed by  $R_X$  bits 2–0 (see Table 4). At powerup, each bit is set to 0 (V<sub>FLT</sub> = 25% V<sub>FLTREF</sub>, t<sub>FR</sub> = 10 ms).

| A <sub>1</sub>          | A <sub>0</sub>                                                                                                                                                                                          | D <sub>5</sub>                                                                                                                                                                                                                                                                                                  | D <sub>4</sub>                                         | D <sub>3</sub> | D <sub>2</sub>                                          | D <sub>1</sub>                                          | D <sub>0</sub>                                          |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|--|

| 1                       | 0                                                                                                                                                                                                       | R <sub>5</sub>                                                                                                                                                                                                                                                                                                  | R <sub>4</sub>                                         | R <sub>3</sub> | R <sub>2</sub>                                          | R <sub>1</sub>                                          | R <sub>0</sub>                                          |  |

|                         |                                                                                                                                                                                                         | C                                                                                                                                                                                                                                                                                                               | HANNELS 5-                                             | 3              | CHANNELS 2–0                                            |                                                         |                                                         |  |

| 25% V <sub>FLTREF</sub> |                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                               | 0                                                      | 0              | Х                                                       | 0                                                       | 0                                                       |  |

| 50% V <sub>FLTREF</sub> |                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                               | 0                                                      | 1              | Х                                                       | 0                                                       | 1                                                       |  |

| 75% V <sub>FLTREF</sub> |                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                               | 1                                                      | 0              | Х                                                       | 1                                                       | 0                                                       |  |

| V <sub>FLTREF</sub>     |                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                               | 1                                                      | 1              | Х                                                       | 1                                                       | 1                                                       |  |

| t <sub>FR</sub> = 10 ms |                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                               | Х                                                      | Х              | 0                                                       | Х                                                       | Х                                                       |  |

| t <sub>FR</sub> = 40 ms |                                                                                                                                                                                                         | Х                                                                                                                                                                                                                                                                                                               | Х                                                      | Х              | 1                                                       | Х                                                       | Х                                                       |  |

| t <sub>FR</sub> = 10 ms |                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                               | Х                                                      | Х              | Х                                                       | Х                                                       | Х                                                       |  |

| t <sub>FR</sub> = 40 ms |                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                               | Х                                                      | Х              | Х                                                       | Х                                                       | Х                                                       |  |

|                         | $\begin{array}{c} A_{1} \\ 1 \\ \hline 25\% \ V_{FLTREF} \\ 50\% \ V_{FLTREF} \\ 75\% \ V_{FLTREF} \\ \hline V_{FLTREF} \\ t_{FR} = 10 \ ms \\ t_{FR} = 40 \ ms \\ \hline t_{FR} = 10 \ ms \end{array}$ | $\begin{tabular}{ c c c c c } \hline A_1 & A_0 & & \\ \hline 1 & 0 & & \\ \hline 25\% \ V_{FLTREF} & & \\ \hline 50\% \ V_{FLTREF} & & \\ \hline 75\% \ V_{FLTREF} & & \\ \hline V_{FLTREF} & & \\ \hline V_{FLTREF} & & \\ \hline t_{FR} = 10 \ ms & & \\ \hline t_{FR} = 10 \ ms & & \\ \hline \end{tabular}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |                | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |

## Table 4. Refresh and Reference Register

## Flag Mask – Register 3

The drain feedback from each channel's  $DRN_X$  input is combined with the channel's  $K_X$  mask bit (Table 5). When  $K_X = 1$ , a channel's mask is cleared and its feedback to the FLTB and STAB flags is enabled. At powerup, each bit is set to 0 (all masks set).

## Table 5. Flag Mask Register

|                                |                | -              | -     |                |                |                |                |                |

|--------------------------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|

| A <sub>2</sub>                 | A <sub>1</sub> | A <sub>0</sub> | $D_5$ | $D_4$          | $D_3$          | $D_2$          | D <sub>1</sub> | D <sub>0</sub> |

| 0                              | 1              | 1              | $K_5$ | K <sub>4</sub> | K <sub>3</sub> | K <sub>2</sub> | K <sub>1</sub> | K <sub>0</sub> |

| 0 = MASK SET<br>1 = MASK CLEAR |                |                |       |                |                |                |                |                |

The STAB flag is influenced when a mask bit changes  $CLR \rightarrow SET$  after one valid SPI frame. FLTB is influenced after two valid SPI frames. This is correct behavior for FLTB since, while a fault persists, the FLTB will be set *when* CSB goes LO $\rightarrow$ HI at the end of an SPI frame. The mask instruction is decoded *after* CSB goes LO $\rightarrow$ HI so FLTB will only reflect the mask bit change after the next SPI frame. Both FLTB and STAB require only one valid SPI frame when a mask bit changes SET $\rightarrow$ CLR.

## Null Register – Register 4

Fault information is always returned when any register is addressed. The null register (Table 6) provides a way to read back fault information without regard to the content of  $D_X$ .

## Table 6. Null Register

| A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1              | Х              | Х              | Х              | Х              | Х              | Х              | Х              | Х              |

## **Gate Driver Control and Enable**

Each GAT<sub>X</sub> output may be turned on by either its respective parallel IN<sub>X</sub> input or the internal G<sub>X</sub> (Gate Select) register bit via SPI communication. The device's common ENA<sub>X</sub> enable inputs can be used to implement global control functions, such as system reset, overvoltage or input override by a watchdog controller. Each parallel input and the ENA2 input have individual internal pulldown current sources. The ENA1 input has an internal pulldown resistor. Unused parallel inputs should be connected to GND and unused enable inputs should be connected to V<sub>CC1</sub>. Parallel input is recommended when low frequency ( $\leq 2.0$  kHz) PWM operation of the outputs is desired.

ENA2 disables all  $GAT_X$  outputs when brought low. When ENA1 is brought low, all  $GAT_X$  outputs, the timer clock, and the flags are disabled. The fault and gate registers are cleared and the flags are reset. New serial  $G_X$  data is ignored while ENA1 is low but other registers can be programmed.

When both the ENA1 and ENA2 inputs are high, the outputs will reflect the current parallel or serial input states. This allows ENA1 to be used to perform a soft reset and ENA2 to be used to disable the  $GAT_X$  outputs during initialization of the NCV7517B.

The  $IN_X$  input state and the  $G_X$  register bit data are logically combined with the internal (active low) power-on reset signal (POR), the  $ENA_X$  input states, and the shorted load state (SHRT<sub>X</sub>) to control the corresponding  $GAT_X$  output such that:

$$\label{eq:GAT_X} \begin{split} \mathsf{GAT}_X = \mathsf{POR} \cdot \mathsf{ENA1} \cdot \mathsf{ENA2} \cdot \overline{\mathsf{SHRT}_X} \cdot (\mathsf{IN}_X + \mathsf{G}_X) \\ & (\mathsf{eq. 1}) \end{split}$$

The  $GAT_X$  state truth table is given in Table 7.

| POR | ENA1 | ENA2 | SHRT <sub>X</sub> | $IN_{X}$ | G <sub>X</sub> | GAT <sub>X</sub> |

|-----|------|------|-------------------|----------|----------------|------------------|

| 0   | Х    | Х    | х                 | Х        | Х              | L                |

| 1   | 0    | 0    | Х                 | Х        | Х              | L                |

| 1   | 0    | 1    | Х                 | Х        | Х              | L                |

| 1   | 1    | 0    | Х                 | Х        | Х              | L                |

| 1   | 1    | 1    | 1                 | 0        | 0              | L                |

| 1   | 1    | 1    | 1                 | 1        | Х              | Н                |

| 1   | 1    | 1    | 1                 | Х        | 1              | Н                |

| 1   | 1    | 1    | 0                 | Х        | Х              | L                |

| 1   | 1→0  | 1    | Х                 | Х        | →0             | →L               |

| 1   | 1    | 1→0  | Х                 | Х        | G <sub>X</sub> | →L               |

| 1   | 1    | 0→1  | Х                 | 0        | G <sub>X</sub> | →G <sub>X</sub>  |

#### Table 7. Gate Driver Truth Table

#### **Gate Drivers**

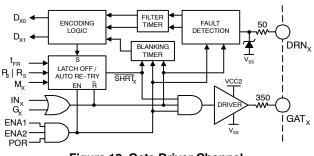

The non-inverting  $GAT_X$  drivers are symmetrical resistive switches (350  $\Omega$  typ.) to the V<sub>CC2</sub> and V<sub>SS</sub> voltages. While the outputs are designed to provide symmetrical gate drive to an external MOSFET, load current switching symmetry is dependent on the characteristics of the external MOSFET and its load. Figure 12 shows the gate driver block diagram.

Figure 12. Gate Driver Channel

#### **Fault Diagnostics and Behavior**

Each channel has independent fault diagnostics and employs blanking and filter timers to suppress false faults. An external MOSFET is monitored for fault conditions by connecting its drain to a channel's  $DRN_X$  feedback input through an external series resistor.

When either ENA1 or ENA2 is low, diagnostics are disabled. When both ENA1 and ENA2 are high, diagnostics are enabled.

Shorted load (or short to  $V_{LOAD}$ ) faults can be detected when a driver is on. Open load or short to GND faults can be detected when a driver is off. On-state faults will initiate MOSFET protection behavior, set the FLTB flag and the respective channel's  $D_X$ bits in the device's fault latches. Off-state faults will simply set the FLTB flag and the channel's  $D_X$  bits.

Fault types are uniquely encoded in a 2-bit per channel format. Fault information for all channels simultaneously is retrieved by SPI read (Figure 11). Table 8 shows the fault-encoding scheme for channel 0. The remaining channels are identically encoded.

|                | Table 6. Tault Data Elicouling |              |  |  |  |  |  |  |  |  |

|----------------|--------------------------------|--------------|--|--|--|--|--|--|--|--|

| CHAN           | NEL 0                          | STATUS       |  |  |  |  |  |  |  |  |

| D <sub>1</sub> | D <sub>0</sub>                 |              |  |  |  |  |  |  |  |  |

| 0              | 0                              | NO FAULT     |  |  |  |  |  |  |  |  |

| 0              | 1                              | OPEN LOAD    |  |  |  |  |  |  |  |  |

| 1              | 0                              | SHORT TO GND |  |  |  |  |  |  |  |  |

| 1              | 1                              | SHORTED LOAD |  |  |  |  |  |  |  |  |

#### **Table 8. Fault Data Encoding**

## **Blanking and Filter Timers**

Blanking timers are used to allow drain feedback to stabilize after a channel is commanded to change states. Filter timers are used to suppress glitches while a channel is in a stable state.

A turn-on blanking timer is started when a channel is commanded on. Drain feedback is sampled after  $t_{BL(ON)}$ . A turn-off blanking timer is started when a channel is commanded off. Drain feedback is sampled after  $t_{BL(OFF)}$ .

A filter timer is started when a channel is in a stable state and a fault detection threshold associated with that state has been crossed. Drain feedback is sampled after  $t_{FF}$ .

Blanking timers for all channels are started when both ENA1 and ENA2 go high or when either  $ENA_X$  goes high while the other is high. The blanking time for each channel depends on the commanded state when  $ENA_X$  goes high.

While each channel has independent blanking and filter timers, the parameters for the  $t_{BL(ON)}$ ,  $t_{BL(OFF)}$ , and  $t_{FF}$  times are the same for all channels.

## **Shorted Load Detection**

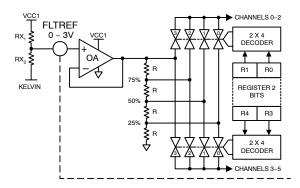

An external reference voltage applied to the FLTREF input serves as a common reference for all channels (Figure 13). The FLTREF voltage must be within the range of 0 to  $V_{CC1}$ -2.0 V and can be derived via a voltage divider between  $V_{CC1}$  and GND.

Shorted load detection thresholds can be programmed via SPI in four 25% increments that are ratiometric to the applied FLTREF voltage. Separate thresholds can be selected for channels 0–2 and for channels 3–5 (Table 4).

A shorted load fault is detected when a channel's  $DRN_X$  feedback is greater than its selected fault reference after either the turn-on blanking or the filter has timed out.

Figure 13. Shorted Load Reference Generator

## Shorted Load Fault Recovery

Shorted load fault disable mode for each channel is individually SPI programmable via the  $M_X$  bits in the device's Disable Mode register (Table 3).

When latch-off mode is selected the corresponding  $GAT_X$  output is turned off upon detection of a fault. Fault recovery is initiated by toggling (ON $\rightarrow$ OFF $\rightarrow$ ON) the channel's respective IN<sub>X</sub> parallel input, serial G<sub>X</sub> bit, or ENA2.

When auto-retry mode is selected (default mode) the corresponding  $GAT_X$  output is turned off for the duration of the programmed fault refresh time ( $t_{FR}$ ) upon detection of a fault. The output is automatically turned back on (if still commanded on) when the refresh time ends. The channel's DRN<sub>X</sub> feedback is resampled after the turn-on blanking time. The output will automatically be turned off if a fault is again detected. This behavior will continue for as long as the channel is commanded on and the fault persists.

In either mode, a fault may exist at turn–on or may occur some time afterward. To be detected, the fault must exist longer than either  $t_{BL(ON)}$  at turn–on or longer than  $t_{FF}$ some time after turn–on. The length of time that a MOSFET stays on during a shorted load fault is thus limited to either  $t_{BL(ON)}$  or  $t_{FF}$ .

In auto-retry mode, a persistent shorted load fault will result in a low duty cycle ( $t_{FD} \approx t_{BL(ON)}/t_{FR}$ ) for the affected channel and help prevent thermal failure of the channel's MOSFET.

**CAUTION** – CONTINUOUS INPUT TOGGLING VIA  $IN_X$ ,  $G_X$  or ENA2 WILL OVERRIDE EITHER DISABLE MODE. Care should be taken to service a shorted load fault quickly when one has been detected.

#### **Fault Recovery Refresh Time**

Refresh time for shorted load faults is SPI programmable to one of two values for channels 0–2 (register bit R2) and for channels 3–5 (register bit R5) via the Refresh and Reference register (Table 4).

A global refresh timer with taps at nominally 10 ms and 40 ms is used for auto-retry timing. The first faulted channel triggers the timer and the full refresh period is guaranteed for that channel. An additional faulted channel may initially retry immediately after its turn-on blanking time, but subsequent retries will have the full refresh time period.

If all channels in a group (e.g. channels 0-2) become faulted, they will become synchronized to the selected refresh period for that group. If all channels become faulted and are set for the same refresh time, all will become synchronized to the refresh period.

## **Open Load and Short to GND Detection**

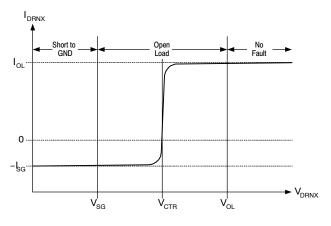

A window comparator with fixed references proportional to  $V_{CC1}$  along with a pair of bias currents is used to detect open load or short to GND faults when a channel is off. Each channel's DRN<sub>X</sub> feedback is compared to the references after either the turn–off blanking or the filter has timed out. Figure 14 shows the DRN<sub>X</sub> bias and fault detection zones. The diagnostics are disabled and the bias currents are turned off when ENA<sub>X</sub> is low.

No fault is detected if the feedback voltage at DRN<sub>X</sub> is greater than the V<sub>OL</sub> open load reference. If the feedback is less than the V<sub>SG</sub> short to GND reference, a short to GND fault is detected. If the feedback is less than V<sub>OL</sub> and greater than V<sub>SG</sub>, an open load fault is detected.

Figure 14. DRN<sub>X</sub> Bias and Fault Detection Zones

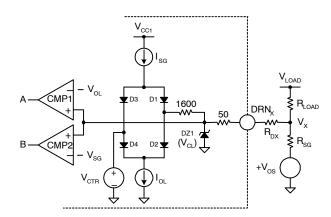

Figure 15 shows the simplified detection circuitry. Bias currents  $I_{SG}$  and  $I_{OL}$  are applied to a bridge along with bias voltage  $V_{CTR}$  (50%  $V_{CC1}$  typ.).

Figure 15. Short to GND/Open-Load Detection

When a channel is off and V<sub>LOAD</sub> and R<sub>LOAD</sub> are present, R<sub>SG</sub> is absent, and V<sub>DRNX</sub> >> V<sub>CTR</sub>, bias current I<sub>OL</sub> is supplied from V<sub>LOAD</sub> to ground through external resistors R<sub>LOAD</sub> and R<sub>DX</sub>, and through the internal 1650  $\Omega$ resistance and bridge diode D2. Bias current I<sub>SG</sub> is supplied from V<sub>CC1</sub> to V<sub>CTR</sub> through D3. No fault is detected if the feedback voltage (V<sub>LOAD</sub> minus the total voltage drop caused by I<sub>SG</sub> and the resistance in the path) is greater than V<sub>OL</sub>.

When either  $V_{LOAD}$  or  $R_{LOAD}$  and  $R_{SG}$  are absent, the bridge will self-bias so that the voltage at  $DRN_X$  will settle to about  $V_{CTR}$ . An open load fault can be detected since the feedback is between  $V_{SG}$  and  $V_{OL}$ .

Short to GND detection can tolerate up to a 1.0 V offset (V<sub>OS</sub>) between the NCV7517B's GND and the short. When R<sub>SG</sub> is present and V<sub>DRNX</sub> << V<sub>CTR</sub>, bias current I<sub>SG</sub> is supplied from V<sub>CC1</sub> to V<sub>OS</sub> through D1, the internal 1650  $\Omega$ , and the external R<sub>DX</sub> and R<sub>SG</sub> resistances. Bias current I<sub>OL</sub> is supplied from V<sub>CTR</sub> to ground through D4.

A "weak" short to GND can be detected when either  $V_{LOAD}$  or  $R_{LOAD}$  is absent and the feedback ( $V_{OS}$  plus the total voltage rise caused by  $I_{OL}$  and the resistance in the path) is less than  $V_{OL}$ .

When  $V_{LOAD}$  and  $R_{LOAD}$  are present, a voltage divider between  $V_{LOAD}$  and  $V_{OS}$  is formed by  $R_{LOAD}$  and  $R_{SG}$ . A "hard" short to GND may be detected in this case depending on the ratio of  $R_{LOAD}$  and  $R_{SG}$  and the values of  $R_{DX}$ ,  $V_{LOAD}$ , and  $V_{OS}$ .

Note that the comparators see a voltage drop or rise due only to the 50  $\Omega$  internal resistance and the bias currents. This produces a small difference in the comparison to the actual feedback voltage at the DRN<sub>X</sub> input.

Several equations for choosing  $R_{DX}$  and for predicting open load or short to GND resistances, and a discussion of the dynamic behavior of the short to GND/open load diagnostic are provided in the Applications Information section of this data sheet.

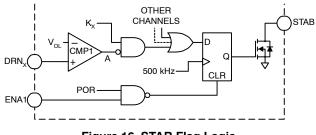

#### Status Flag (STAB)

The open-drain active-low status flag output can be used to provide a host controller with information about the state of a channel's  $DRN_x$  feedback. Feedback from all channels is logically ORed to the flag (Figure 16). The STAB outputs from several devices can be wire-ORed to a common pullup resistor connected to the controller's 3.3 or 5.0 V V<sub>DD</sub> supply.

When ENA1 is high, the drain feedback from a channel's  $DRN_x$  input is compared to the  $V_{OL}$  reference without regard to ENA2 or the commanded state of the channel's driver. The flag is reset and disabled when ENA1 is low or when all mask bits are set. See Table 9 for additional details.

The flag is set (low) when the feedback voltage is less than  $V_{OL}$ , and the channel's mask bit (Table 5) is cleared. The flag is reset (hi–Z) when the feedback voltage is greater than  $V_{OL}$ , and the channel's mask bit is cleared.

Figure 16. STAB Flag Logic

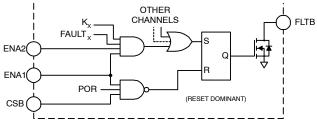

## Fault Flag (FLTB)

The open-drain active-low fault flag output can be used to provide immediate fault notification to a host controller. Fault detection from all channels is logically ORed to the flag (Figure 17). The FLTB outputs from several devices can be wire-ORed to a common pullup resistor connected to the controller's 3.3 or 5.0 V V<sub>DD</sub> supply.

The flag is set (low) when a channel detects any fault, the channel's mask bit (Table 5) is cleared, and both  $ENA_x$  and CSB are high. The flag is reset (hi–Z) and disabled when either ENA1 or CSB is low. See Table 9 for additional details.

Figure 17. FLTB Flag Logic

## **Fault Detection and Capture**

Each channel of the NCV7517B is capable of detecting shorted load faults when the channel is on, and short to ground or open load faults when the channel is off. Each fault type is uniquely encoded into two-bit per channel fault data. A drain feedback input for each channel compares the voltage at the drain of the channel's external MOSFET to several internal reference voltages. Separate detection references are used to distinguish the three fault types, and blanking and filter timers are used respectively to allow for output state transition settling and for glitch suppression.

Fault diagnostics are disabled when either enable input is low. When both enable inputs are high, each channel's drain feedback input is continuously compared to references appropriate to the channel's input state to detect faults, but the comparison result is only latched at the end of either a blanking or filter timer event.

Blanking timers for all channels are triggered when either enable input changes state from low to high while the other enable input is high, or when both enable inputs go high simultaneously. A single channel's blanking timer is triggered when its input state changes. If the comparison of the feedback to a reference indicates an abnormal condition when the blanking time ends, a fault has been detected and the fault data is latched into the channel's fault latch.

A channel's filter timer is triggered when its drain feedback comparison state changes. If the change indicates an abnormal condition when the filter time ends, a fault has been detected and the fault data is latched into the channel's fault latch.

Thus, a state change of the inputs  $(ENA_X, IN_X \text{ or } G_X)$  or a state change of an individual channel's feedback  $(DRN_X)$ comparison must occur for a timer to be triggered and a detected fault to be captured.

# Fault Capture, SPI Communication, and SPI Frame Error Detection

The fault capture and frame error detection strategies of the NCV7517B combine to ensure that intermittent faults can be captured and identified, and that the device cannot be inadvertently reprogrammed by a communication error.

The NCV7517B latches a fault when it is detected, and frame error detection will not allow any register to accept data if an invalid frame occurred.

When a fault has been detected, the FLTB flag is set and fault data is latched into a channel's fault latch. The latch captures and holds the fault data and ignores subsequent fault data for that channel until a valid SPI frame occurs.

Fault data from all channels is transferred from each channel's fault latch into the SPI shift register and the FLTB

flag is reset when CSB goes low at the start of the SPI frame. Fault latches are cleared and re-armed when CSB goes high at the end of the SPI frame only if a valid frame has occurred; otherwise the latches retain the detected fault data until a valid frame occurs. The FLTB flag will be set if a fault is still present.

Fault latches for all channels and the FLTB flag can also be cleared and re–armed by toggling ENA1 H–L–H. A full I/O truth table is given in Table 9.

## Fault Data Readback Examples

Several examples are shown to illustrate fault detection, capture and SPI read-back of fault data for one channel. A normal SPI frame returns 16 bits of data but only the two bits of serial data for the single channel are shown for clarity.

The examples assume:

- The NCV7517B is configured as in Figure 2

- Both enable inputs are high

- The channel's flag mask bit is cleared

- Disable mode is set to auto-retry

- The parallel input commands the channel

- SPI frame is always valid

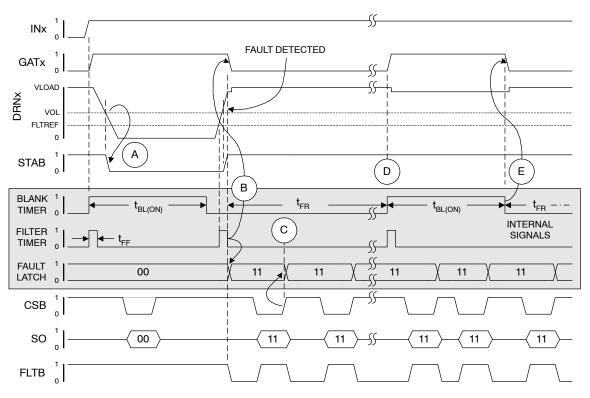

## Shorted Load Detected

Refer to Figure 18. The channel is commanded on when  $IN_X$  goes high.  $GAT_X$  goes high and the timers are started. At "A", the STAB flag is set as the  $DRN_X$  feedback falls through the  $V_{OL}$  threshold. A SPI frame sent soon after the  $IN_X$  command returns data indicating "no fault."

The blanking time ends and the filter timer is triggered as  $DRN_X$  rises through the FLTREF threshold. The STAB flag is reset as  $DRN_X$  passes through the  $V_{OL}$  threshold. DRN<sub>X</sub> is nearly at  $V_{LOAD}$  when the filter time ends at "B". A shorted load fault is detected and captured by the fault latch,  $GAT_X$  goes low, the FLTB flag is set, and the auto-retry timer is started.

An SPI frame sent soon after "B" returns data indicating "shorted load". The FLTB flag is reset when CSB goes low. At "C" when CSB goes high at the end of the frame, the fault latch is cleared and re-armed. Since  $IN_X$  and the DRN<sub>X</sub> feedback are unchanged, FLTB and the fault latch are set and the fault is recaptured.

When the auto-retry timer ends at "D",  $GAT_X$  goes high and the blanking and filter timers are started. Since  $IN_X$  and  $DRN_X$  are unchanged,  $GAT_X$  goes low when the blanking time ends at "E" and the auto-retry timer is started. Read-back data continues to indicate a "shorted load" and the FLTB flag continues to be set while the fault persists.

Figure 18. Shorted Load Detected

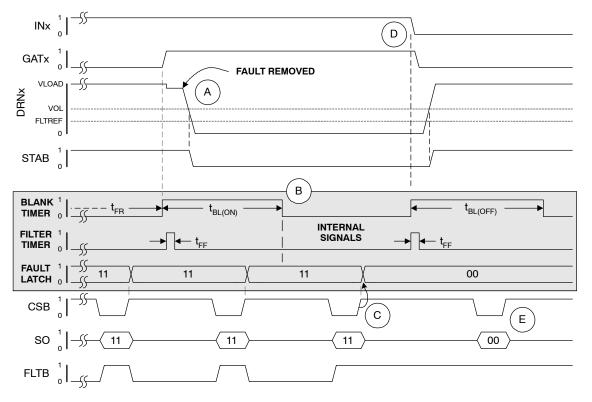

## **Shorted Load Recovery**

Figure 19 is a continuation of Figure 18.  $IN_X$  is high when the auto-retry timer ends.  $GAT_X$  goes high and the blanking and filter timers are started. The fault is removed before the blanking timer ends, and  $DRN_X$  starts to fall. As  $DRN_X$  passes through the V<sub>OL</sub> threshold at "A", the STAB flag is set.  $DRN_X$  continues to fall and settles below the FLTREF threshold.

An SPI frame is sent during the blanking time and returns data indicating a "shorted load" fault. Although the fault is removed, updates to the fault latches are suppressed while a blanking or filter timer is active. The same fault is captured again and FLTB is set when CSB goes high. At "B" the blanking time ends and the channel's fault bits will indicate "no fault" but because the latched data has not yet been read, the data remains unchanged.

The SPI frame sent after the blanking time ends returns a "shorted load" fault because the previous frame occurred during the blanking time. Since the channel's fault bits indicate "no fault", FLTB is reset and the fault latch is updated at "C" when CSB goes high. If another SPI frame is sent before "D", the returned data will indicate "no fault".