# **NCV7701**

# 2.0 Amp H-Bridge Driver

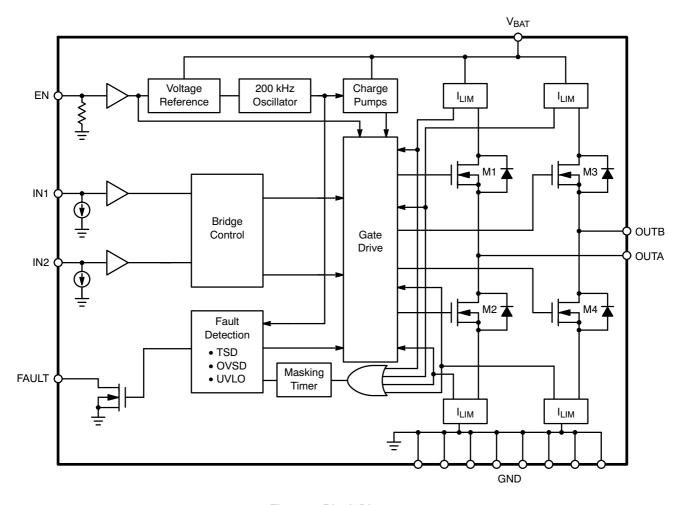

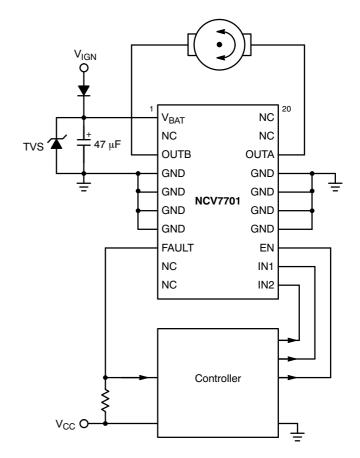

This automotive grade H-Bridge driver provides a flexible means for controlling loads requiring bidirectional drive currents. Bridge outputs are protected from overcurrent at each switch and overtemperature shutdown provides product robustness. The NCV7701 inputs can be interfaced to a range of voltages, including vehicle battery voltage. The product features a low quiescent current mode, allowing unswitched connection to the power source. The NCV7701 is produced using ON Semiconductor's POWERSENSE™ BCD technology.

### **Features**

- Forward, Reverse, Brake High, Brake Low Modes

- 1.0 A Output Current Capability (DC)

- Supply Voltage Range 7.0 V to 26 V

- 0.25 Ω R<sub>DS(ON)</sub> per Driver @ 25°C

- Sleep Mode ( $I_O < 10 \mu A$ )

- Overvoltage Protection

- Thermal Protection

- Undervoltage Disable Function

- Short Circuit Protection

- Cross Conduction Protection

- Synchronous Low-Side Rectification for Lower Power Dissipation

- Diagnostic Output (Open Drain)

- TTL/CMOS/Pullup to Battery Compatible Inputs

- 20 Lead SO Package with 8 Internally Fused Leads

- AEC Qualified

- PPAP Capable

- These are Pb-Free Devices\*

### **Typical Applications**

- DC Motors

- Stepper Motors

- Modulator Valves

# ON Semiconductor®

http://onsemi.com

MARKING DIAGRAM

SOIC-20 WB CASE 751D DW SUFFIX

A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week G = Pb-Free Package

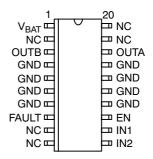

### **PIN CONNECTIONS**

### **ORDERING INFORMATION**

| Device       | Package               | Shipping <sup>†</sup> |

|--------------|-----------------------|-----------------------|

| NCV7701DWG   | SOIC-20W<br>(Pb-Free) | 38 Units/Rail         |

| NCV7701DWR2G | SOIC-20W<br>(Pb-Free) | 1000 Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Figure 1. Block Diagram

### **MAXIMUM RATINGS**

| Rating                                                                                              | Value      | Unit    |

|-----------------------------------------------------------------------------------------------------|------------|---------|

| Supply Voltage (DC) - V <sub>BAT</sub> (Note 1)                                                     | -0.3 to 45 | V       |

| Logic Input Voltage (DC)                                                                            | -0.3 to 12 | V       |

| Junction Temperature Range                                                                          | -40 to 150 | °C      |

| Storage Temperature Range                                                                           | -65 to 150 | °C      |

| Peak Transient (1.0 ms rise time, 300 ms period, 31 V Load Dump @ V <sub>BAT</sub> = 14 V) (Note 1) |            | V       |

| ESD Susceptibility Human Body Model Machine Model                                                   |            | kV<br>V |

| Package Thermal Resistance Junction-to-Case, $R_{\theta JC}$ Junction-to-Ambient, $R_{\theta JA}$   | 9.0<br>55  | °C/W    |

| Lead Temperature Soldering: Reflow: (SMD styles only) (Note 2)                                      | 230 peak   | °C      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. External reverse-battery and transient voltage suppression (TVS) required.

- 2. 60 second maximum above 183°C.

# **NCV7701**

$\textbf{ELECTRICAL CHARACTERISTICS} \quad (7.0 \text{ V} \leq \text{V}_{BAT} \leq 26 \text{ V}, -40^{\circ}\text{C} \leq \text{T}_{J} \leq 125^{\circ}\text{C}; \text{ unless otherwise specified.) Note 3}$

| Characteristic                                                           | Test Conditions                                                                                | Min | Тур    | Max       | Unit     |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|--------|-----------|----------|

| GENERAL                                                                  |                                                                                                |     |        |           |          |

| V <sub>BAT</sub> Quiescent Current:<br>Low Quiescent<br>Normal Operation | EN = 0 V, V <sub>BAT</sub> ≤ 12.8 V<br>2.5 V ≤ EN ≤ V <sub>BAT</sub> , V <sub>BAT</sub> = 14 V |     | -<br>- | 10<br>8.0 | μA<br>mA |

| EN LOGIC INPUT                                                           |                                                                                                | •   |        |           |          |

| Low Level Input Voltage                                                  | -                                                                                              | -   | _      | 0.7       | V        |

| High Level Input Voltage                                                 | -                                                                                              | 2.5 | -      | -         | V        |

| Input Bias Current                                                       | EN = 5.0 V                                                                                     | 15  | 50     | 100       | μΑ       |

| Input Leakage Current                                                    | EN = 0 V                                                                                       | -   | -      | 1.0       | μΑ       |

| IN1, IN2, LOGIC INPUTS                                                   |                                                                                                |     |        |           |          |

| Low Level Input Voltage                                                  | -                                                                                              | -   | -      | 0.8       | V        |

| High Level Input Voltage                                                 | -                                                                                              | 2.0 | -      | -         | V        |

| Input Bias Current                                                       | 5.0 V on Logic Input, EN = 5.0 V                                                               | 5.0 | 20     | 40        | μΑ       |

| Input Leakage Current                                                    | 0 V on Logic Input, EN = 0 V                                                                   | -   | -      | 1.0       | μΑ       |

| IC PROTECTION                                                            |                                                                                                |     |        |           |          |

| Overvoltage Shutdown                                                     | ı                                                                                              | 27  | 32     | 37        | V        |

| Overvoltage Hysteresis                                                   | -                                                                                              | 0.2 | 0.5    | 1.0       | V        |

| Undervoltage Voltage Lockout                                             | -                                                                                              | -   | -      | 6.5       | ٧        |

| Undervoltage Hysteresis                                                  | ı                                                                                              | 100 | 200    | 400       | mV       |

| Thermal Shutdown                                                         | (Guaranteed by Design)                                                                         | 160 | 185    | 210       | °C       |

| Thermal Hysteresis                                                       | (Guaranteed by Design)                                                                         | 10  | 22.5   | 35        | °C       |

| DRIVERS OUTA, OUTB                                                       |                                                                                                |     |        |           |          |

| Output High Voltage (V <sub>H</sub> )                                    | $V_{BAT}$ = 14 V, $I_{SOURCE}$ = 1.0 A, $V_{H}$ = $V_{BAT}$ - $OUT_{X}$                        | -   | 0.4    | 0.75      | V        |

| Output Low Voltage (V <sub>L</sub> )                                     | $V_{BAT}$ = 14 V, $I_{SOURCE}$ = 1.0 A, $V_{L}$ = $OUT_{X}$ - $V_{GND}$                        | -   | 0.4    | 0.75      | V        |

| Current Limit                                                            | V <sub>BAT</sub> = 14 V                                                                        | 3.0 | 4.0    | 5.0       | Α        |

| FAULT OUTPUT                                                             |                                                                                                |     |        |           |          |

| Output Leakage Current                                                   | V <sub>FAULT</sub> = 5.0 V, Fault Absent                                                       | -   | -      | 10        | μΑ       |

| Output Low Voltage                                                       | I <sub>FAULT</sub> = 0.5 mA, Fault Present                                                     | -   | -      | 1.0       | V        |

| AC CHARACTERISTICS                                                       |                                                                                                |     |        |           |          |

| Output Turn-On Delay                                                     | ı                                                                                              | -   | 5.0    | 10        | μs       |

| Output Turn-Off Delay                                                    | -                                                                                              | -   | 5.0    | 10        | μs       |

| Current Limit Mask Time                                                  | -                                                                                              | 20  | 40     | 60        | μS       |

|                                                                          |                                                                                                |     |        |           |          |

<sup>3.</sup> Designed to meet these characteristics over the stated voltage and temperature ranges, though may not be 100% parametrically tested in production.

Table 1. H-Bridge Mode Control

| EN | IN1 | IN2 | H-Bridge         | OUTA | OUTB |

|----|-----|-----|------------------|------|------|

| 0  | Х   | Х   | Off (Sleep Mode) | Off  | Off  |

| 1  | 0   | 0   | Brake Low        | Low  | Low  |

| 1  | 0   | 1   | Forward          | High | Low  |

| 1  | 1   | 0   | Reverse          | Low  | High |

| 1  | 1   | 1   | Brake High       | High | High |

# Table 2. Fault Diagnostics

| Fault Condition  | Fault Pin | H-Bridge                              |

|------------------|-----------|---------------------------------------|

| No Faults        | High Z    | Normal Operation                      |

| Undervoltage     | Low       | Off                                   |

| Overvoltage      | Low       | Off                                   |

| Thermal Shutdown | Low       | Off                                   |

| Current Limit    | Low       | 1 or more Drivers in<br>Current Limit |

### PACKAGE PIN DESCRIPTION

| Pin No.                       | Symbol    | Description        |

|-------------------------------|-----------|--------------------|

| 1                             | $V_{BAT}$ | IC supply voltage  |

| 2, 9, 10, 19, 20              | NC        | No connection      |

| 3                             | OUTB      | Bridge output      |

| 4, 5, 6, 7, 14,<br>15, 16, 17 | GND       | Power ground       |

| 8                             | FAULT     | Diagnostic output  |

| 11                            | IN2       | Mode control input |

| 12                            | IN1       | Mode control input |

| 13                            | EN        | Chip enable        |

| 18                            | OUTA      | Bridge output      |

### **Operating Description**

During powerup, the outputs are HI-Z regardless of the input states. When the undervoltage lockout threshold is exceeded, the outputs will reflect the input states. Outputs change to HI-Z whenever an undervoltage, overvoltage or thermal shutdown fault is detected. Normal operation will resume when faults are resolved.

## **Overcurrent Protection**

Current is monitored continuously in each switch of each half bridge when the ENA input is in a high state thus protecting each switch from faults due to short to GND, short to V<sub>BAT</sub> or shorted load conditions. Only the affected half-bridge is disabled for short to V<sub>BAT</sub> or short to GND faults. A mask timer is initiated after a fault is detected and prevents recognition of an overcurrent event until the mask time expires. Persistence of an overcurrent condition causes the bridge output to change to HI-Z and the FAULT output to latch low until the next transition occurs on either the input related to the faulted output or the ENA input is brought low then high again. This method of protection provides current limiting on a cycle-by-cycle basis and helps allow a stall torque current to be ignored during motor start. Continued overcurrent may eventually result in activation of the thermal shutdown circuitry, thus activating a second level of protection for the NCV7701.

Figure 2. Application Diagram

### NCV7701

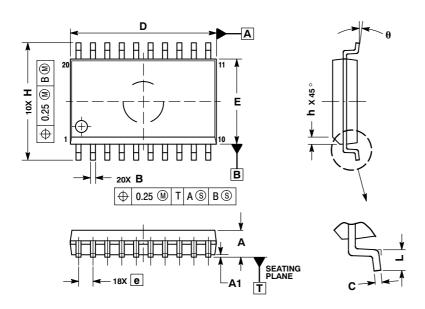

### PACKAGE DIMENSIONS

SOIC-20 WB CASE 751D-05 **ISSUE G**

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

- INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 2.35        | 2.65  |  |

| A1  | 0.10        | 0.25  |  |

| В   | 0.35        | 0.49  |  |

| С   | 0.23        | 0.32  |  |

| D   | 12.65       | 12.95 |  |

| Е   | 7.40        | 7.60  |  |

| е   | 1.27        | BSC   |  |

| Н   | 10.05       | 10.55 |  |

| h   | 0.25        | 0.75  |  |

| L   | 0.50        | 0.90  |  |

| Λ   | n o         | 70    |  |

POWERSENSE is a trademark of Semiconductor Components Industries, LLC.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered raderians of semiconductor components industries, Ite (SciLLC) solicit esserves the right to make changes without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

N. American Technical Support: 800-282-9855 Toll Free

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative