# Quad-Output Automotive System Power Supply IC with Integrated High-Side 2A Switch

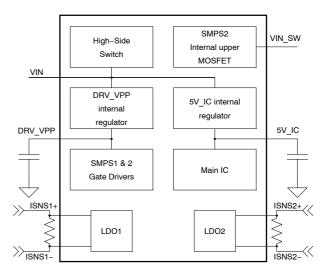

The NCV8855 is a multiple output controller / regulator IC with an integrated high-side load switch. The NCV8855 addresses automotive radio system and instrument cluster power supply requirements. In addition to the high-side load switch, the NCV8855 includes a switch-mode power supply (SMPS) buck controller, a 2.5 A SMPS buck regulator and two low dropout (LDO) linear regulator controllers. The NCV8855 in combination with the ultra-low quiescent current NCV861x IC forms an eight-output automotive radio or instrument cluster power solution. The NCV8855 has an internally set switching frequency of 170 kHz, with a SYNC pin for external frequency synchronization.

The NCV8855 is intended to supply power to various loads, such as a tuner, CD logic, audio processor and CD / tape control within a car radio. The high–side switch can be used for a CD / tape mechanism or switching an electrically–powered antenna or display unit. In an instrument cluster application, the NCV8855 can be used to power graphics display, flash memory and CAN transceivers. In addition, the high–side switch can be used to limit power to a TFT display during a battery over–voltage condition.

#### **Features**

- < 1 μA Shutdown Current

- Meets ES-XW7T-1A278-AB Test Pulse G Loaded Conditions

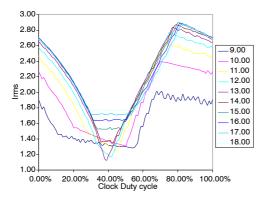

- $\bullet$  V<sub>IN</sub> Operating Range 9.0 to 18.0 V

- 1 SMPS Controller with Adjustable Current Limit

- 1 SMPS Regulator with Internal 300 mΩ NMOS Switch

- 2 LDO Controllers with Current Limit and Short Circuit Protection

- 1 High-side Load Switch with Internal 300 mΩ NMOS FET

- Adjustable Output Voltage for All Controllers / Regulators

- J 1 6 7 6

- 800 mV,  $\pm 1\%$  Reference Voltage

- System Enable Pin

- Single Enable Pin for Both LDO Controllers

- Independent Enable for High-side Load Switch

- Thermal Shutdown with Thermal Warning Indicator

- This is a Pb-Free Device

# **Applications**

- Automotive Radio

- Instrument Cluster, Driver Information System (DIS)

# ON Semiconductor®

http://onsemi.com

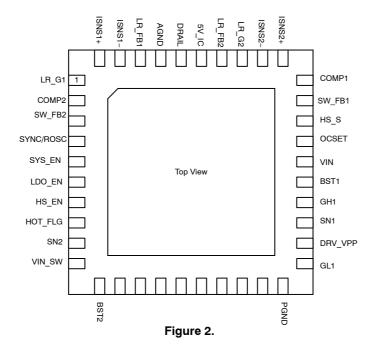

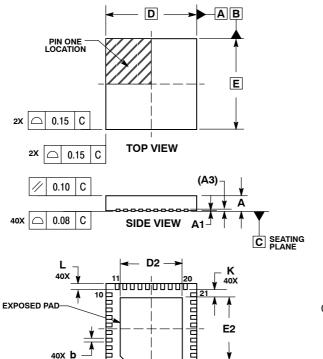

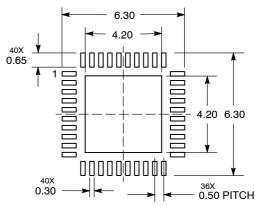

#### 40 PIN QFN, 6x6 MN SUFFIX CASE 488AR

### MARKING DIAGRAM

NCV8855 AWLYYWWG

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NCV8855BMNR2G | QFN-40<br>(Pb-Free) | 2500 / Tape &<br>Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

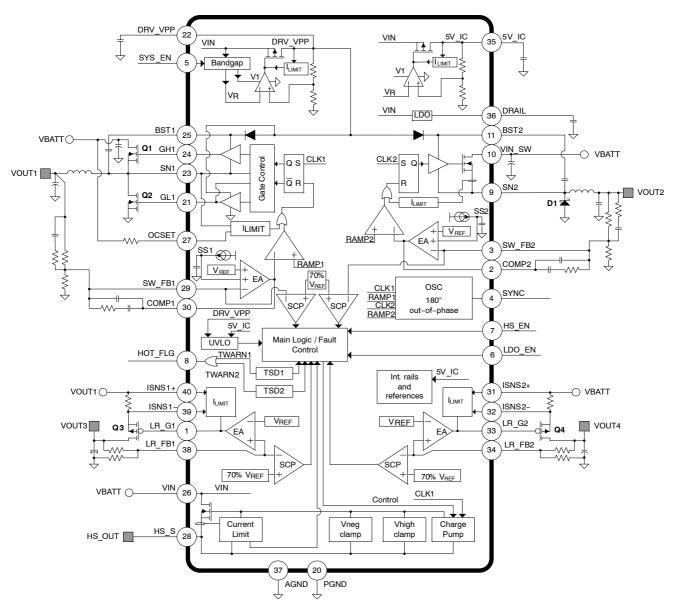

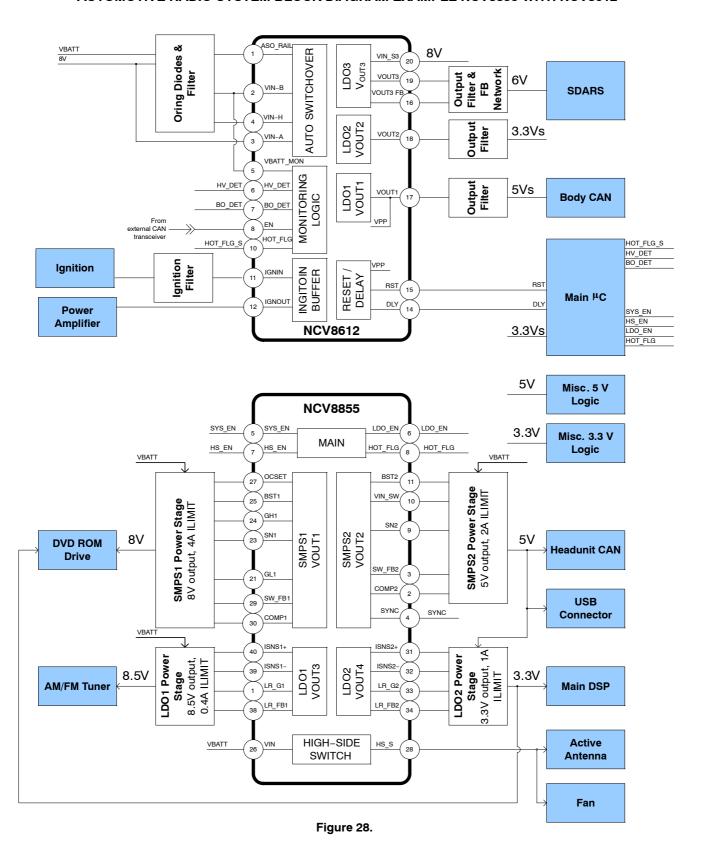

#### TYPICAL APPLICATION SCHEMATIC SHOWING DETAILED BLOCK DIAGRAM

Figure 1. Application Schematic / Block Diagram

| Components | Part Number  | Value                                      | Manufacturer     |

|------------|--------------|--------------------------------------------|------------------|

| D1         | MBRS4201T3   | 200 V, 4 A, Schottky, 0.61 V Vf, SMC       | ON Semiconductor |

| Q1, Q2     | NTD24N06     | 60 V, N type MOSFET, 32 m $\Omega$ , DPAK  | ON Semiconductor |

| Q3, Q4     | NTD20P06LT4G | –60V, P type MOSFET, 130 m $\Omega$ , DPAK | ON Semiconductor |

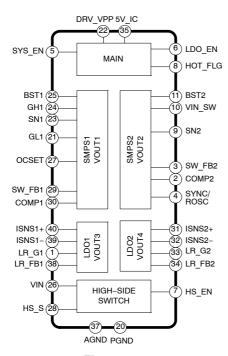

### **PIN FUNCTION DESCRIPTIONS**

| Pin No. | Symbol  | Description                                                                                                                                                                  |  |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5       | SYS_EN  | Main enable pin for the IC. A logic high on this pin will enable the part. Leaving this pin floating or driving it to ground will place the IC in shutdown mode.             |  |

| 6       | LDO_EN  | Enable pin for both LDO controllers. A logic high on this pin will enable both LDO controllers. If this pin is left floating, an internal pull down keeps the LDOs disabled. |  |

| 7       | HS_EN   | Enable pin for the high-side load switch. A logic high on this pin will enable the HSS. If this pin is left floating, an internal pull down keeps the HSS disabled.          |  |

| 8       | HOT_FLG | Thermal warning indicator. This pin provides an early warning signal of an impending thermal shutdown.                                                                       |  |

| 22      | DRV_VPP | Output of the internal 7.2 V linear regulator. Bypass this pin with 1 $\mu F$ to ground.                                                                                     |  |

| 35      | 5V_IC   | Output of the internal 5 V linear regulator. Bypass this pin with 0.1 μF to ground.                                                                                          |  |

| 36      | DRAIL   | Output of the internal 4.2 V linear regulator. Bypass this pin with 0.1 $\mu\text{F}$ to ground.                                                                             |  |

| 4       | SYNC    | Synchronization pin. Use this pin to synchronize the internal oscillator to an external clock. If synchronization is not used, connect this pin to AGND.                     |  |

| 37      | AGND    | Analog ground. Reference point for internal signals.                                                                                                                         |  |

### SWITCH-MODE POWER SUPPLY 1 (SMPS1) PIN CONNECTIONS

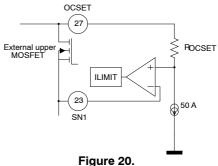

| 27 | OCSET  | Overcurrent set pin, used to set the current limit threshold. A resistor connected from this pin and the upper MOSFET Drain sets the current limit protection level.                                                                                       |  |

|----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29 | SW_FB1 | Output voltage feedback pin. Connect a resistor divider network to VOUT1 to set the desired output voltage.                                                                                                                                                |  |

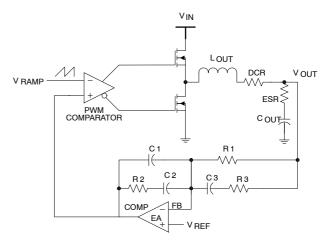

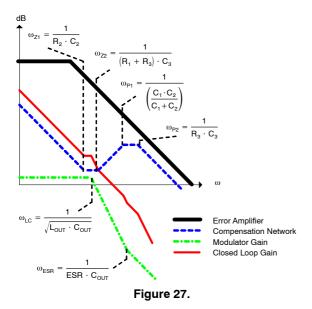

| 30 | COMP1  | This pin is the output of the error amplifier and the non-inverting input of the PWM comparator. Use this pin in conjunction with the SW_FB1 pin to compensate the voltage-mode control feedback loop.                                                     |  |

| 25 | BST1   | This pin is the supply rail for the upper N–Channel MOSFET. An internal bootstrap diode brings DRV_VPP to this pin. Connect a ceramic capacitor ( $C_{BST1}$ ) between this pin and the SN1 pin. A typical value for $C_{BST1}$ is 0.1 $\mu$ F.            |  |

| 24 | GH1    | GH1 is the output pin of the internal upper N-Channel MOSFET gate driver. Keep the trace from this pin to the gate of the upper MOSFET as short as possible to achieve the best turn-on and turn-off performance and to reduce electro-magnetic emissions. |  |

| 23 | SN1    | This pin is the return path of the upper floating gate driver. Connect this pin to the source of the upper MOSFET. This pin is also used to sense the current flowing through the upper MOSFETs.                                                           |  |

| 21 | GL1    | GL1 is the output pin of the synchronous rectifier gate driver. Connect this pin to the lower N-channel MOSFET.                                                                                                                                            |  |

| 20 | PGND   | This pin is the return path for SMPS1 lower MOSFET driver current. Connect this pin to the source of the lower MOSFET.                                                                                                                                     |  |

### PINS NOT INTERNALLY CONNECTED TO SILICON

| EP            | - | Exposed pad of QFN package. Connect to printed circuit board ground to improve thermal performance. |  |

|---------------|---|-----------------------------------------------------------------------------------------------------|--|

| 12 thru<br>19 |   | These pins can be left floating or tied to ground to improve thermal performance.                   |  |

### SWITCH-MODE POWER SUPPLY 2 (SMPS2) PIN CONNECTIONS

| 10 | VIN_SW | This pin is the supply rail for the internal upper N-Channel MOSFET. Bypass this pin with a local ceramic capacitor. Additional bulk capacitance may be required based off output requirements. Refer to application section for more information.       |  |

|----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3  | SW_FB2 | Output voltage feedback pin. Connect a resistor divider network to VOUT2 to set the desired output voltage.                                                                                                                                              |  |

| 2  | COMP2  | This pin is the output of the error amplifier and the non-inverting input of the PWM comparator. Use this pin in conjunction with the SW_FB2 pin to compensate the voltage-controlled feedback loop.                                                     |  |

| 11 | BST2   | This pin is the supply rail for the internal upper N–Channel MOSFET. An internal bootstrap diode brings DRV_VPP to this pin. Connect a ceramic capacitor ( $C_{BST2}$ ) between this pin and the SN2 pin. A typical value for $C_{BST2}$ is 0.1 $\mu$ F. |  |

| 9  | SN2    | Source output of the internal upper N-channel MOSFET.                                                                                                                                                                                                    |  |

#### **PIN FUNCTION DESCRIPTIONS**

| Pin No. | Symbol                                                           | Description                                                                                                                                                                                                                                                     |  |  |  |

|---------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LOW DRO | LOW DROPOUT LINEAR REGULATOR CONTROLLER 1 (LDO1) PIN CONNECTIONS |                                                                                                                                                                                                                                                                 |  |  |  |

| 38      | LR_FB1                                                           | LDO controller output voltage feedback pin. Connect a resistor divider network to VOUT3 to set the desired output voltage.                                                                                                                                      |  |  |  |

| 1       | LR_G1                                                            | Error amplifier output of the LDO controller. Connect to gate of P-Channel MOSFET pass element.                                                                                                                                                                 |  |  |  |

| 40      | ISNS1+                                                           | Current sense positive input. Connect this pin to the supply side of the current sense resistor. This pin also serves as the supply rail for the linear regulator controller. A local bypass capacitor with a value of 0.1 $\mu$ F to 1 $\mu$ F is recommended. |  |  |  |

| 39      | ISNS1-                                                           | Current sense negative input. When using a current sense resistor, connect this pin to the pass element side of the current sense resistor. If current limit is not used, connect this pin to the supply rail of the pass element.                              |  |  |  |

### LOW DROPOUT LINEAR REGULATOR CONTROLLER 2 (LDO2) PIN CONNECTIONS

| 34 | LR_FB2 | LDO controller output voltage feedback pin. Connect a resistor divider network to VOUT3 to set the desired output voltage.                                                                                                                                      |  |

|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 33 | LR_G2  | Error amplifier output of the LDO controller. Connect to gate of P-Channel MOSFET pass element.                                                                                                                                                                 |  |

| 31 | ISNS2+ | Current sense positive input. Connect this pin to the supply side of the current sense resistor. This pin also serves as the supply rail for the linear regulator controller. A local bypass capacitor with a value of 0.1 $\mu$ F to 1 $\mu$ F is recommended. |  |

| 32 | ISNS2- | Current sense negative input. When using a current sense resistor, connect this pin to the pass element side of the current sense resistor. If current limit is not used, connect this pin to the supply rail of the pass element.                              |  |

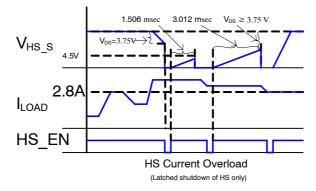

# HIGH-SIDE LOAD SWITCH (HSS) PIN CONNECTIONS

| 26 | VIN  | This pin is the supply rail for the internal high-side load switch, DRV_VPP and 5V_IC. Bypass this pin with a 1 $\mu$ F ceramic capacitor. |  |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 28 | HS_S | Source node output of the internal high-side N-Channel MOSFET load switch.                                                                 |  |

### MAXIMUM RATINGS (Voltages are with respect to AGND unless noted otherwise)

| Pin Name                                                                                                                              | Value       | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| Max dc voltage (GH1, BST1, SN1, SN2, BST2, HS_S)                                                                                      | -0.3 to 30  | ٧    |

| Negative Transient (t < 50 ns) (SN1, SN2)                                                                                             | -2          | ٧    |

| Max dc voltage: 5V_IC                                                                                                                 | 6           | V    |

| Max dc voltage: DRV_VPP                                                                                                               | 9           | V    |

| Max dc voltage (BST1 & GH1w/respect to SN1, GL1, BST2 w/respect to SN2)                                                               | -0.3 to 15  | ٧    |

| Max dc voltage (OCSET, ISNS1+, ISNS1-, LR_G1, VIN, VIN_SW, ISNS2+, ISNS2-, LR_G2)                                                     | -0.3 to 40  | V    |

| Peak Transient (ES-XW7T-1A278-AB Test Pulse G - Loaded Conditions) (OCSET, ISNS1+, ISNS1-, LR_G1, VIN, VIN_SW, ISNS2+, ISNS2-, LR_G2) | -0.3 to 45  | V    |

| Max dc voltage (SW_FB1, COMP1, LR_FB1, LDO_EN, HOT_FLG, SW_FB2, COMP2, LR_FB2, HS_EN, SYS_EN, SYNC)                                   | -0.3 to 7   | ٧    |

| Max dc voltage: PGND                                                                                                                  | -0.3 to 0.3 | V    |

| Maximum Operating Junction Temperature Range, T <sub>J</sub>                                                                          | -40 to 150  | °C   |

| Maximum Storage Temperature Range, T <sub>STG</sub>                                                                                   | -55 to +150 | °C   |

| Peak Reflow Soldering Temperature: Pb-Free 60 to 150 seconds at 217°C                                                                 | 260 peak    | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **ATTRIBUTES**

| Description                                                                                     | Symbol          | Value         | Unit          |

|-------------------------------------------------------------------------------------------------|-----------------|---------------|---------------|

| Thermal Characteristic                                                                          |                 | 36            | °C/W          |

| $R_{\theta,JA}$ generated from 1 sq in / 1 oz copper 1 sided PCB                                | $R_{\theta JC}$ | 3             | °C/W          |

| ESD Capability<br>Human Body Model (SN1, SN2)<br>Human Body Model (All Others)<br>Machine Model |                 | 1<br>2<br>150 | kV<br>kV<br>V |

| Moisture Sensitivity Level                                                                      | MSL             | 1             |               |

#### RECOMMENDED OPERATING CONDITIONS

| Description                     | Value          |

|---------------------------------|----------------|

| VBATT range (refer to Figure 1) | 9 V to 18 V    |

| Ambient Temperature range       | −40°C to 105°C |

**ELECTRICAL CHARACTERISTICS** ( $V_{IN\_SW} = V_{IS} = V_{ISNS1+} = V_{ISNS1-} = V_{ISNS2+} = V_{ISNS2-} = 13.2 \text{ V}$ , SYS\_EN = LDO\_EN = HS\_EN = 5 V, VOUT3 = 3.3 V, VOUT4 = 8.5 V, IOUT[1:4] = 0 A) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq T_{J} \leq 150^{\circ}\text{C}$  unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Parameter                              | Symbol           | Conditions                                                   | Min | Тур  | Max | Unit |

|----------------------------------------|------------------|--------------------------------------------------------------|-----|------|-----|------|

| SUPPLY VOLTAGES AND SYSTEM             | SPECIFICA        | TION                                                         |     |      |     |      |

| Supply Current and Operating Voltage F | Range            |                                                              |     |      |     |      |

| VIN_SW quiescent current               |                  | No Switching, $V_{SW}_{FB2}$ = 1V, SN2 = PGND1, $T_J$ = 25°C |     | 175  |     | μΑ   |

| VIN_SW shutdown current                |                  | SYS_EN = 0 V, T <sub>J</sub> = 25°C                          |     | 100  | 500 | nA   |

| High VIN detect voltage                | V <sub>OVP</sub> | VIN rising                                                   | 18  | 18.5 | 19  | V    |

| High VIN detect hysteresis             |                  | VIN falling                                                  | 0.2 | 0.6  | 1   |      |

| VIN quiescent current                  |                  | T <sub>J</sub> = 25°C                                        |     | 4    |     | mA   |

| VIN shutdown current                   |                  | SYS_EN = 0 V, T <sub>J</sub> = 25°C                          |     | 100  | 500 | nA   |

- 1. Guaranteed by design, not fully tested in production.

- 2. Indirectly guaranteed by test coverage of other parameters.

**ELECTRICAL CHARACTERISTICS** ( $V_{IN\_SW} = V_{IS} = V_{ISNS1+} = V_{ISNS2+} = V_{ISNS2+} = V_{ISNS2-} = 13.2 \text{ V}$ , SYS\_EN = LDO\_EN = HS\_EN = 5 V, VOUT3 = 3.3 V, VOUT4 = 8.5 V, IOUT[1:4] = 0 A) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq T_{J} \leq 150^{\circ}\text{C}$  unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Internal Voltage Reference Internal Voltage Reference Internal Voltage reference range  Internal Linear Regulator 5 V Supply Rail  5V_IC UVLO threshold voltage  5V_IC UVLO hysteresis  Voltage range  Current limit Load regulation Line regulation Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis  Voltage range  VV | VREF  DRV_VPP      | $\begin{split} &T_J = 25^{\circ}C\\ &-40^{\circ}C \leq T_J \leq 150^{\circ}C\\ &V_{5V\_IC} \ rising\\ &V_{5V\_IC} \ falling\\ &No \ load\\ &1mA \leq I_{5V\_IC} \leq 10 \ mA\\ &I_{5V\_IC} = 5 \ mA, 9 \ V \leq VIN \leq 18 \ V\\ &V_{DRV\_VPP} \ rising\\ &V_{DRV\_VPP} \ falling\\ &No \ load \end{split}$                     | 0.792<br>0.784<br>4.00<br>100<br>4.8<br>10<br>4.00<br>100<br>6.9 | 4.35<br>150<br>5<br>21<br>4.35<br>150<br>7.1 | 0.808<br>0.816<br>4.70<br>300<br>5.2<br>50<br>100<br>4.70<br>300 | V  V  mV  V  mA  mV  V  V  mV |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------|-------------------------------|

| Internal voltage reference range  Internal Linear Regulator 5 V Supply Rail  5V_IC UVLO threshold voltage  5V_IC UVLO hysteresis  Voltage range  Current limit  Load regulation  Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                       |                    | $-40^{\circ}C \leq T_{J} \leq 150^{\circ}C$ $V_{5V\_IC} \text{ rising}$ $V_{5V\_IC} \text{ falling}$ $No \text{ load}$ $1\text{mA} \leq I_{5V\_IC} \leq 10 \text{ mA}$ $I_{5V\_IC} = 5 \text{ mA}, 9 \text{ V} \leq \text{VIN} \leq 18 \text{ V}$ $V_{DRV\_VPP} \text{ rising}$ $V_{DRV\_VPP} \text{ falling}$ $No \text{ load}$ | 0.784<br>4.00<br>100<br>4.8<br>10<br>4.00<br>100<br>6.9          | 4.35<br>150<br>5<br>21<br>4.35<br>150        | 0.816  4.70  300  5.2  50  100  4.70  300                        | V mV V mA mV V V              |

| Internal Linear Regulator 5 V Supply Rail  5V_IC UVLO threshold voltage  5V_IC UVLO hysteresis  Voltage range  Current limit  Load regulation  Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                         |                    | $-40^{\circ}C \leq T_{J} \leq 150^{\circ}C$ $V_{5V\_IC} \text{ rising}$ $V_{5V\_IC} \text{ falling}$ $No \text{ load}$ $1\text{mA} \leq I_{5V\_IC} \leq 10 \text{ mA}$ $I_{5V\_IC} = 5 \text{ mA}, 9 \text{ V} \leq \text{VIN} \leq 18 \text{ V}$ $V_{DRV\_VPP} \text{ rising}$ $V_{DRV\_VPP} \text{ falling}$ $No \text{ load}$ | 0.784<br>4.00<br>100<br>4.8<br>10<br>4.00<br>100<br>6.9          | 4.35<br>150<br>5<br>21<br>4.35<br>150        | 0.816  4.70  300  5.2  50  100  4.70  300                        | V mV V mA mV V V              |

| 5V_IC UVLO threshold voltage  5V_IC UVLO hysteresis  Voltage range  Current limit  Load regulation  Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                                                                    | DRV_VPP            | $V_{5V\_IC} \ falling$ No load $1mA \leq I_{5V\_IC} \leq 10 \ mA$ $I_{5V\_IC} = 5 \ mA, 9 \ V \leq VIN \leq 18 \ V$ $V_{DRV\_VPP} \ rising$ $V_{DRV\_VPP} \ falling$ No load                                                                                                                                                     | 100<br>4.8<br>10<br>4.00<br>100<br>6.9                           | 150<br>5<br>21<br>4.35<br>150                | 300<br>5.2<br>50<br>50<br>100<br>4.70<br>300                     | mV<br>V<br>mA<br>mV<br>mV     |

| 5V_IC UVLO hysteresis  Voltage range  Current limit  Load regulation  Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                                                                                                  | DRV_VPP            | $V_{5V\_IC} \ falling$ No load $1mA \leq I_{5V\_IC} \leq 10 \ mA$ $I_{5V\_IC} = 5 \ mA, 9 \ V \leq VIN \leq 18 \ V$ $V_{DRV\_VPP} \ rising$ $V_{DRV\_VPP} \ falling$ No load                                                                                                                                                     | 100<br>4.8<br>10<br>4.00<br>100<br>6.9                           | 150<br>5<br>21<br>4.35<br>150                | 300<br>5.2<br>50<br>50<br>100<br>4.70<br>300                     | mV<br>V<br>mA<br>mV<br>mV     |

| Voltage range  Current limit  Load regulation  Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                                                                                                                         | DRV_VPP            | No load $ 1\text{mA} \leq I_{5\text{V\_IC}} \leq 10 \text{ mA} $ $ I_{5\text{V\_IC}} = 5 \text{ mA}, 9 \text{ V} \leq \text{VIN} \leq 18 \text{ V} $ $ \text{V}_{\text{DRV\_VPP}} \text{ rising} $ $ \text{V}_{\text{DRV\_VPP}} \text{ falling} $ No load                                                                        | 4.8<br>10<br>4.00<br>100<br>6.9                                  | 5<br>21<br>4.35<br>150                       | 5.2<br>50<br>50<br>100<br>4.70<br>300                            | V<br>mA<br>mV<br>mV           |

| Current limit Load regulation Line regulation Internal DRV_VPP Supply Rail DRV_VPP UVLO threshold voltage DRV_VPP UVLO hysteresis                                                                                                                                                                                                                             | DRV_VPP            | $1\text{mA} \leq I_{5\text{V\_IC}} \leq 10 \text{ mA}$ $I_{5\text{V\_IC}} = 5 \text{ mA}, 9 \text{ V} \leq \text{VIN} \leq 18 \text{ V}$ $V_{DR\text{V\_VPP}} \text{ rising}$ $V_{DR\text{V\_VPP}} \text{ falling}$ No load                                                                                                      | 4.00<br>100<br>6.9                                               | 21<br>4.35<br>150                            | 50<br>50<br>100<br>4.70<br>300                                   | mA<br>mV<br>mV                |

| Load regulation  Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                                                                                                                                                       | DRV_VPP            | $I_{5V\_IC} = 5 \text{ mA}, 9 \text{ V} \leq \text{VIN} \leq 18 \text{ V}$ $V_{DRV\_VPP} \text{ rising}$ $V_{DRV\_VPP} \text{ falling}$ No load                                                                                                                                                                                  | 4.00<br>100<br>6.9                                               | 4.35<br>150                                  | 50<br>100<br>4.70<br>300                                         | mV<br>mV                      |

| Line regulation  Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                                                                                                                                                                        | DRV_VPP            | $I_{5V\_IC} = 5 \text{ mA}, 9 \text{ V} \leq \text{VIN} \leq 18 \text{ V}$ $V_{DRV\_VPP} \text{ rising}$ $V_{DRV\_VPP} \text{ falling}$ No load                                                                                                                                                                                  | 100                                                              | 150                                          | 4.70<br>300                                                      | mV<br>V                       |

| Internal DRV_VPP Supply Rail  DRV_VPP UVLO threshold voltage  DRV_VPP UVLO hysteresis                                                                                                                                                                                                                                                                         | DRV_VPP            | V <sub>DRV_VPP</sub> rising V <sub>DRV_VPP</sub> falling No load                                                                                                                                                                                                                                                                 | 100                                                              | 150                                          | 4.70                                                             | V                             |

| DRV_VPP UVLO threshold voltage DRV_VPP UVLO hysteresis                                                                                                                                                                                                                                                                                                        | DRV_VPP            | V <sub>DRV_VPP</sub> falling No load                                                                                                                                                                                                                                                                                             | 100                                                              | 150                                          | 300                                                              |                               |

| DRV_VPP UVLO hysteresis                                                                                                                                                                                                                                                                                                                                       | DRV_VPP            | V <sub>DRV_VPP</sub> falling No load                                                                                                                                                                                                                                                                                             | 100                                                              | 150                                          | 300                                                              |                               |

|                                                                                                                                                                                                                                                                                                                                                               | DRV_VPP            | No load                                                                                                                                                                                                                                                                                                                          | 6.9                                                              |                                              |                                                                  | mV                            |

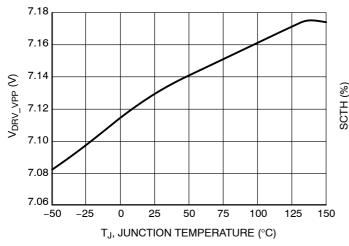

| Voltage range V                                                                                                                                                                                                                                                                                                                                               | DRV_VPP            |                                                                                                                                                                                                                                                                                                                                  |                                                                  | 7.1                                          |                                                                  | 4                             |

|                                                                                                                                                                                                                                                                                                                                                               |                    |                                                                                                                                                                                                                                                                                                                                  | 30                                                               |                                              | 7.3                                                              | ٧                             |

| Current limit                                                                                                                                                                                                                                                                                                                                                 |                    |                                                                                                                                                                                                                                                                                                                                  | 1                                                                | 67                                           | 110                                                              | mA                            |

| Load regulation                                                                                                                                                                                                                                                                                                                                               |                    | $1 \text{ mA} \leq I_{DRV\_VPP} \leq 25 \text{ mA}$                                                                                                                                                                                                                                                                              |                                                                  |                                              | 50                                                               | mV                            |

| Line regulation                                                                                                                                                                                                                                                                                                                                               |                    | $I_{DRV\_VPP}$ = 1 mA, 9 V $\leq$ VIN $\leq$ 18 V                                                                                                                                                                                                                                                                                |                                                                  |                                              | 200                                                              | mV                            |

| Dropout voltage                                                                                                                                                                                                                                                                                                                                               |                    | $I_{DRV\_VPP}$ = 25 mA, $\Delta V_{DRV\_VPP}$ = 2 %                                                                                                                                                                                                                                                                              |                                                                  |                                              | 400                                                              | mV                            |

| Oscillator                                                                                                                                                                                                                                                                                                                                                    |                    |                                                                                                                                                                                                                                                                                                                                  | •                                                                |                                              |                                                                  |                               |

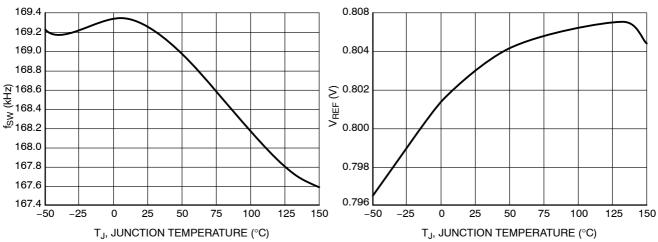

| Oscillator frequency                                                                                                                                                                                                                                                                                                                                          | f <sub>SW</sub>    |                                                                                                                                                                                                                                                                                                                                  | 154.7                                                            | 170                                          | 185.3                                                            | kHz                           |

| SYNC                                                                                                                                                                                                                                                                                                                                                          |                    |                                                                                                                                                                                                                                                                                                                                  | •                                                                |                                              |                                                                  |                               |

| Logic high                                                                                                                                                                                                                                                                                                                                                    |                    |                                                                                                                                                                                                                                                                                                                                  |                                                                  |                                              | 2.0                                                              | V                             |

| Logic low                                                                                                                                                                                                                                                                                                                                                     |                    |                                                                                                                                                                                                                                                                                                                                  | 0.8                                                              |                                              |                                                                  | V                             |

| Pull down current                                                                                                                                                                                                                                                                                                                                             |                    | V <sub>SYNC</sub> = 5 V<br>V <sub>SYNC</sub> = 0.8 V                                                                                                                                                                                                                                                                             | 2                                                                | 5<br>5                                       | 10                                                               | μΑ                            |

| Leakage current                                                                                                                                                                                                                                                                                                                                               |                    | SYS_EN = 0 V, V <sub>SYNC</sub> = 5 V                                                                                                                                                                                                                                                                                            |                                                                  | 100                                          | 500                                                              | nA                            |

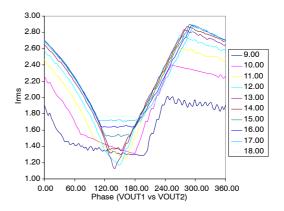

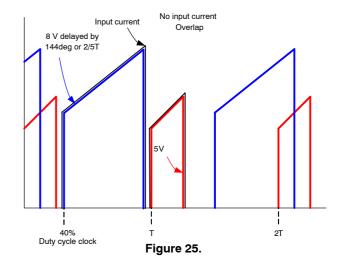

| Clock synchronization range                                                                                                                                                                                                                                                                                                                                   |                    |                                                                                                                                                                                                                                                                                                                                  | 190                                                              |                                              | 255                                                              | kHz                           |

| Synchronization delay to SMPS1                                                                                                                                                                                                                                                                                                                                |                    | From falling SYNC edge                                                                                                                                                                                                                                                                                                           | 200                                                              |                                              | 400                                                              | ns                            |

| Synchronization delay to SMPS2                                                                                                                                                                                                                                                                                                                                |                    | From rising SYNC edge                                                                                                                                                                                                                                                                                                            | 200                                                              |                                              | 400                                                              | ns                            |

| Minimum SYNC pulse width (HIGH)                                                                                                                                                                                                                                                                                                                               |                    | SMPS1 synchronizing                                                                                                                                                                                                                                                                                                              |                                                                  |                                              | 50                                                               | ns                            |

| Minimum SYNC pulse width (LOW)                                                                                                                                                                                                                                                                                                                                |                    | SMPS2 synchronizing                                                                                                                                                                                                                                                                                                              |                                                                  |                                              | 50                                                               | ns                            |

| Thermal Monitoring (T <sub>MON_HSS</sub> , High-side )                                                                                                                                                                                                                                                                                                        | junction t         | emperature monitor)                                                                                                                                                                                                                                                                                                              | •                                                                | •                                            |                                                                  |                               |

| Thermal warning temperature                                                                                                                                                                                                                                                                                                                                   | T <sub>WARN1</sub> |                                                                                                                                                                                                                                                                                                                                  | 140                                                              | 150                                          | 160                                                              | °C                            |

| T <sub>WARN1</sub> hysteresis                                                                                                                                                                                                                                                                                                                                 |                    |                                                                                                                                                                                                                                                                                                                                  | 10                                                               |                                              | 20                                                               | °C                            |

| Thermal shutdown temperature                                                                                                                                                                                                                                                                                                                                  | TSD1               |                                                                                                                                                                                                                                                                                                                                  | 160                                                              | 170                                          | 180                                                              | °C                            |

| Delta junction temperature<br>(TSD1-T <sub>WARN1</sub> )                                                                                                                                                                                                                                                                                                      |                    |                                                                                                                                                                                                                                                                                                                                  | 10                                                               | 20                                           | 30                                                               | °C                            |

| Thermal Monitoring (T <sub>MON_SW,</sub> SMPS2 inte                                                                                                                                                                                                                                                                                                           | ernal MOS          | FET temperature monitor)                                                                                                                                                                                                                                                                                                         | -                                                                |                                              |                                                                  |                               |

| Thermal warning temperature                                                                                                                                                                                                                                                                                                                                   | T <sub>WARN2</sub> |                                                                                                                                                                                                                                                                                                                                  | 140                                                              | 150                                          | 160                                                              | °C                            |

Guaranteed by design, not fully tested in production.

Indirectly guaranteed by test coverage of other parameters.

**ELECTRICAL CHARACTERISTICS** ( $V_{IN\_SW} = V_{IS} = V_{ISNS1+} = V_{ISNS2+} = V_{ISNS2+} = V_{ISNS2-} = 13.2 \text{ V}$ , SYS\_EN = LDO\_EN = HS\_EN = 5 V, VOUT3 = 3.3 V, VOUT4 = 8.5 V, IOUT[1:4] = 0 A) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq T_{J} \leq 150^{\circ}\text{C}$  unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Parameter                                                | Symbol              | Conditions                                               | Min | Тур    | Max | Unit |

|----------------------------------------------------------|---------------------|----------------------------------------------------------|-----|--------|-----|------|

| SUPPLY VOLTAGES AND SYSTEM                               | SPECIFICA           | TION                                                     |     |        |     |      |

| Thermal Monitoring (T <sub>MON_SW,</sub> SMPS2 i         | internal MOS        | FET temperature monitor)                                 |     |        |     |      |

| T <sub>WARN2</sub> hysteresis                            |                     |                                                          | 10  |        | 20  | °C   |

| Thermal shutdown temperature                             | TSD2                |                                                          | 160 | 170    | 180 | °C   |

| Delta junction temperature<br>(TSD2-T <sub>WARN2</sub> ) |                     |                                                          | 10  | 20     | 30  | °C   |

| HOT_FLG                                                  |                     |                                                          |     |        | 1   |      |

| Voltage low threshold                                    |                     | $T_J$ > TWARN[x], 1 kΩ pullup to 5 V                     |     |        | 0.4 | V    |

| Leakage current                                          |                     | 1 kΩ pull–up to 5 V, $T_J$ = 25°C                        |     | 100    | 500 | nA   |

| Sink capability                                          |                     | V <sub>HOT_FLG</sub> = 0.8 V                             | 4.6 |        |     | mA   |

| System Enable                                            |                     |                                                          | •   |        | •   |      |

| Logic high                                               |                     |                                                          | 2.0 |        |     | V    |

| Logic low                                                |                     |                                                          |     |        | 0.8 | V    |

| Pull down resistance                                     |                     | T <sub>J</sub> = 25°C                                    |     | 500    |     | kΩ   |

| High-Side Enable                                         |                     |                                                          | •   |        | •   |      |

| HS_EN logic high                                         |                     |                                                          |     |        | 2.0 | V    |

| HS_EN logic low                                          |                     |                                                          | 0.8 |        |     | V    |

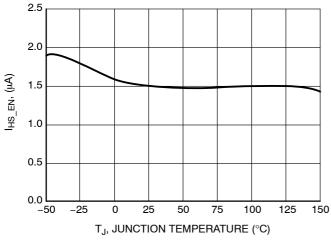

| Pull down current                                        |                     | V <sub>HS_EN</sub> = 5 V<br>V <sub>HS_EN</sub> = 0.8 V   | 2   | 5<br>5 | 10  | μΑ   |

| Leakage current                                          | I <sub>HS_EN</sub>  | SYS_EN = 0 V, V <sub>HS_EN</sub> = 5 V                   |     | 100    | 500 | nA   |

| LDO Enable                                               |                     |                                                          | •   |        | •   |      |

| Logic high                                               |                     |                                                          |     |        | 2.0 | V    |

| Logic low                                                |                     |                                                          | 0.8 |        |     | V    |

| Pull down current                                        |                     | V <sub>LDO_EN</sub> = 5 V<br>V <sub>LDO_EN</sub> = 0.8 V | 2   | 5<br>5 | 10  | μΑ   |

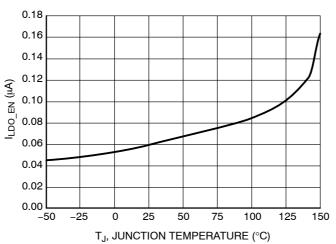

| Leakage current                                          | I <sub>LDO_EN</sub> | SYS_EN = 0 V, V <sub>LDO_EN</sub> = 5 V                  |     | 100    | 500 | nA   |

# SWITCH-MODE POWER SUPPLY CONTROLLER (SMPS1, VOUT1) SPECIFICATIONS

| Over Current Protection                |                  |                                                                              |     |     |     |    |

|----------------------------------------|------------------|------------------------------------------------------------------------------|-----|-----|-----|----|

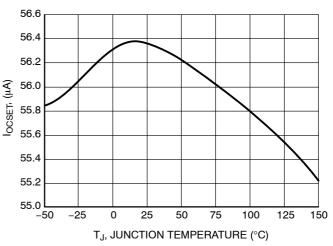

| OCSET current sink                     |                  | $R_{OCSET}$ = 10 kΩ connected to 13.2 V                                      | 45  | 55  | 65  | μΑ |

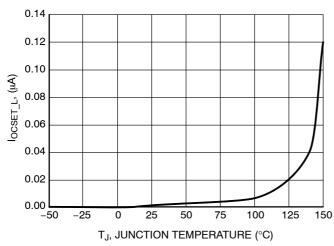

| OCSET leakage current                  |                  | SYS_EN = 0 V, V <sub>OCSET</sub> = 13.2 V,<br>T <sub>J</sub> = 25°C          |     | 100 | 500 | nA |

| OCSET comparator differential range    |                  | (Note 1)                                                                     | 50  |     | 750 | mV |

| OCSET comparator common–mode range     |                  | (Note 1)                                                                     | 4.0 |     | 19  | V  |

| Current limit response time            |                  | From rising edge of SN1                                                      | 100 | 200 | 275 | ns |

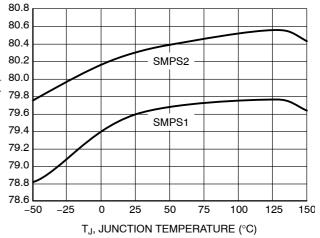

| Short circuit threshold voltage        | SCTH1            | V <sub>SW_FB1</sub> % of V <sub>REF</sub>                                    | 75  | 80  | 85  | %  |

| Short circuit protection startup delay |                  | From SYS_EN rising edge, % of t <sub>SS1</sub> ,<br>SW_FB1 = 0.5 V, (Note 2) | 100 | 125 | 150 | %  |

| Internal Soft-Start                    |                  |                                                                              |     |     |     |    |

| Soft-start time                        | t <sub>SS1</sub> |                                                                              | 3   | 5   | 7   | ms |

- 1. Guaranteed by design, not fully tested in production.

- 2. Indirectly guaranteed by test coverage of other parameters.

**Conditions**

3.3

2.8

1.1

1.6

80

120

3.0

1.2

1.8

140

250

30

30

3.2

1.3

2.0

200

300

70

70

ns

ns

ns

ns

ELECTRICAL CHARACTERISTICS (V<sub>IN</sub> SW = V<sub>IN</sub> = V<sub>ISNS1+</sub> = V<sub>ISNS1-</sub> = V<sub>ISNS2+</sub> = V<sub>ISNS2-</sub> = 13.2 V, SYS\_EN = LDO\_EN = HS\_EN = 5 V, VOUT3 = 3.3 V, VOUT4 = 8.5 V, IOUT[1:4] = 0 A) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq \text$ 150°C unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

Symbol

$V_{\text{RAMP1}}$

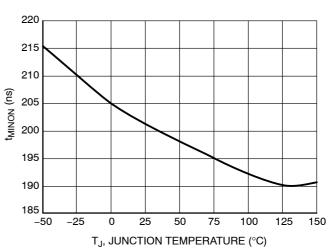

t<sub>MINOFF1</sub>

t<sub>MINON1</sub>

**t**NOLT

| SWITCH-MODE POWER SUPPLY O | CONTROLLER (SMPS1, VOUT1) SPECIFICATIONS                                                | ;   |    |      |      |

|----------------------------|-----------------------------------------------------------------------------------------|-----|----|------|------|

| Error Amplifier            |                                                                                         |     |    |      |      |

| Dc gain                    | (Note 1)                                                                                | 70  | 85 |      | dB   |

| Gain-bandwidth product     | (Note 1)                                                                                | 8   | 10 |      | MHz  |

| SW_FB1 input bias current  | SW_FB1 = 0.8 V                                                                          |     |    | 100  | nA   |

| Input offset voltage       | (Note 1)                                                                                |     |    | 800  | μV   |

| Slew rate                  | C <sub>COMP1</sub> = 50 pF, ±1 mA dc load Slew rate within ramp voltage levels (Note 1) | 6   | 8  |      | V/μs |

| COMP1 source current       | V <sub>COMP1</sub> = 2.2 V                                                              | 1.5 |    | 8    | mA   |

|                            | V <sub>COMP1</sub> = 3.2 V                                                              | 1.6 |    | 8    | mA   |

| COMP1 sink current         | V <sub>COMP1</sub> = 2.2 V                                                              | 1.1 |    | 8    | mA   |

|                            | V <sub>COMP1</sub> = 1.1 V                                                              | 0.7 |    | 8    | mA   |

| Minimum COMP1 voltage      | I <sub>COMP1</sub> = 500 μA                                                             |     |    | 1.05 | V    |

|                            | <del>i</del>                                                                            |     | 1  |      | 1    |

$I_{COMP1} = 2 \text{ mA}$

# **Duty Cycle Limitations** Minimum off time

SN1 falling to GL1 rising, non-overlap

Minimum pulse width

Maximum COMP1 voltage

Ramp maximum voltage

Ramp minimum voltage

Ramp voltage amplitude

**Parameter**

| Gate Driver        |                                                               |     |   |

|--------------------|---------------------------------------------------------------|-----|---|

| GH1 source current | $V_{GH1} - V_{SN1} = 4 \text{ V, T}_{J} = 25^{\circ}\text{C}$ | 1.5 | А |

| GH1 sink current   | $V_{GH1} - V_{SN1} = 2 \text{ V, T}_{J} = 25^{\circ}\text{C}$ | 1.5 | А |

| GL1 source current | $V_{GL1} - PGND = 4 \text{ V}, T_J = 25^{\circ}\text{C}$      | 1.5 | А |

| GL1 sink current   | V <sub>GL1</sub> – PGND = 1 V, T <sub>J</sub> = 25°C          | 1.5 | А |

GH1 falling to GL1 rising

GH1 rising to GH1 falling

#### GL1 falling to GH1 rising, non-overlap SN1 falling non-overlap threshold 1.0 1.8 3.0 ٧ voltage GL1 falling non-overlap threshold ٧ 2 voltage SN1 falling override timer 100 150 ns

#### SWITCH-MODE POWER SUPPLY REGULATOR (SMPS2, VOUT2) SPECIFICATIONS

| Over Current Protection                |       |                                                                    |     |      |     |    |

|----------------------------------------|-------|--------------------------------------------------------------------|-----|------|-----|----|

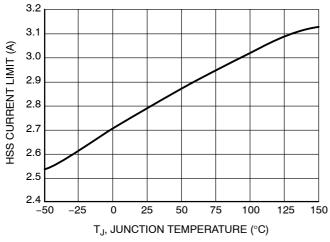

| Internal current limit                 |       |                                                                    | 2.5 | 3.05 | 4.2 | Α  |

| Current limit blanking time            |       |                                                                    | 100 |      | 200 | ns |

| Short circuit threshold voltage        | SCTH2 | V <sub>SW_FB2</sub> % of V <sub>REF</sub>                          | 75  | 85   | 95  | %  |

| Short circuit protection startup delay |       | From SYS_EN rising edge, % of t <sub>SS2</sub> ,<br>SW_FB2 = 0.5 V | 100 | 125  | 150 | %  |

- 1. Guaranteed by design, not fully tested in production.

- 2. Indirectly guaranteed by test coverage of other parameters.

**ELECTRICAL CHARACTERISTICS** ( $V_{IN\_SW} = V_{IS} = V_{ISNS1+} = V_{ISNS2+} = V_{ISNS2+} = V_{ISNS2-} = 13.2 \text{ V}$ , SYS\_EN = LDO\_EN = HS\_EN = 5 V, VOUT3 = 3.3 V, VOUT4 = 8.5 V, IOUT[1:4] = 0 A) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \leq T_{J} \leq 150^{\circ}\text{C}$  unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Parameter                            | Symbol               | Conditions                                                                              | Min | Тур | Max  | Unit |

|--------------------------------------|----------------------|-----------------------------------------------------------------------------------------|-----|-----|------|------|

| SWITCH-MODE POWER SUPPL              | Y REGULATO           | R (SMPS2, VOUT2) SPECIFICATIONS                                                         |     |     |      |      |

| Internal Soft-start                  |                      |                                                                                         |     |     |      |      |

| Soft-start time                      | t <sub>SS2</sub>     | SYNC floating                                                                           | 3   | 5   | 7    | ms   |

| Error Amplifier                      |                      |                                                                                         |     |     | -    |      |

| Dc gain                              |                      | (Note 1)                                                                                | 70  | 85  |      | dB   |

| Gain-bandwidth product               |                      | (Note 1)                                                                                | 8   | 10  |      | MHz  |

| SW_FB2 input bias current            |                      | SW_FB2 = 0.8 V                                                                          |     | 100 | 500  | nA   |

| Input offset voltage                 |                      |                                                                                         |     |     | 800  | μV   |

| Slew rate                            |                      | C <sub>COMP2</sub> = 50 pF, ±1 mA dc load Slew rate within ramp voltage levels (Note 1) | 6   | 8   |      | V/μs |

| COMP2 source current                 |                      | V <sub>COMP2</sub> = 2.2 V                                                              | 1.5 |     | 8    | mA   |

|                                      |                      | V <sub>COMP2</sub> = 3.2 V                                                              | 1.6 |     | 8    | mA   |

| COMP2 sink current                   |                      | V <sub>COMP2</sub> = 2.2 V                                                              | 1.1 |     | 8    | mA   |

|                                      |                      | V <sub>COMP2</sub> = 1.1 V                                                              | 0.7 |     | 8    | mA   |

| Minimum COMP2 voltage                |                      | I <sub>COMP2</sub> = 500 μA                                                             |     |     | 1.05 | V    |

| Maximum COMP2 voltage                |                      | I <sub>COMP2</sub> = 2 mA                                                               | 3.3 |     |      | V    |

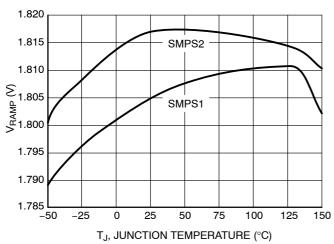

| Ramp maximum voltage                 |                      |                                                                                         | 2.8 | 3.0 | 3.2  | V    |

| Ramp minimum voltage                 |                      |                                                                                         | 1.1 | 1.2 | 1.3  | V    |

| Ramp voltage amplitude               | V <sub>RAMP2</sub>   |                                                                                         | 1.6 | 1.8 | 2.0  | V    |

| Duty Cycle Limitations               | •                    |                                                                                         |     |     |      |      |

| Minimum off time                     | t <sub>MINOFF2</sub> | SN2 falling to SN2 rising                                                               | 80  | 140 | 200  | ns   |

| Minimum pulse width                  | t <sub>MINON2</sub>  | SN2 rising to SN2 falling,                                                              | 120 | 250 | 300  | ns   |

| Switching MOSFET                     | •                    |                                                                                         |     |     |      |      |

| N-channel MOSFET R <sub>DS(on)</sub> |                      | T <sub>J</sub> = 25°C, Guaranteed at Probe                                              |     | 300 | 360  | mΩ   |

| Turn-on time                         |                      | $SN2 \rightarrow 0$ V to 13.2 V, IOUT = 1 A (inductive load), $T_J = 25^{\circ}C$       |     | 30  |      | ns   |

| Turn-off time                        |                      | SN2 $\rightarrow$ 13.2 V to 0 V, IOUT = 1 A (inductive load), T <sub>J</sub> = 25°C     |     | 30  |      | ns   |

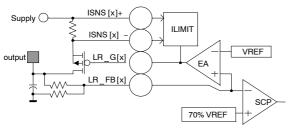

# LOW DROPOUT LINEAR REGULATOR CONTROLLER (LDO1, VOUT3) SPECIFICATIONS

| Output Voltage Regulation         |                   |                                                                                     |       |      |      |    |

|-----------------------------------|-------------------|-------------------------------------------------------------------------------------|-------|------|------|----|

| Output voltage accuracy           |                   | V <sub>LR FB1</sub> tied to VOUT3 directly, NTD20P06L pass device                   | -2    |      | 2    | %  |

| Output voltage line regulation    |                   | IOUT3 = 10 mA, 4.5 V $\leq$ V <sub>ISNS1+</sub> $\leq$ 5.5 V, NTD20P06L pass device | -0.25 | 0.01 | 0.25 | %  |

| Output voltage load regulation    |                   | 1 mA $\leq$ IOUT3 $\leq$ 500 mA, $V_{ISNS1+} = 5$ V, NTD20P06L pass device          | -0.5  | 0.2  | 0.5  | %  |

| Output load capacitance range     | C <sub>OUT3</sub> | (Note 1)                                                                            | 10    |      | 100  | μF |

| Output load capacitance ESR range |                   | (Note 1)                                                                            | 0.01  |      | 5    | Ω  |

| Power supply ripple rejection     | PSRR1             | NTD20P06L pass device (Note 1)                                                      |       | 60   |      | dB |

| Current Limit                     |                   |                                                                                     |       |      |      |    |

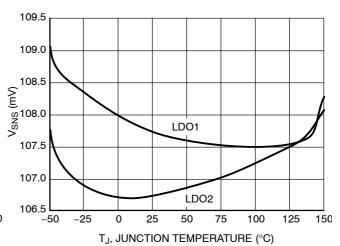

| Current limit threshold voltage   | V <sub>SNS1</sub> | V <sub>ISNS1+</sub> - V <sub>ISNS1-</sub>                                           | 90    | 110  | 130  | mV |

- Guaranteed by design, not fully tested in production.

Indirectly guaranteed by test coverage of other parameters.

**ELECTRICAL CHARACTERISTICS** ( $V_{IN\_SW} = V_{IN} = V_{ISNS1+} = V_{ISNS2+} = V_{ISNS2+} = V_{ISNS2-} = 13.2 \text{ V}$ , SYS\_EN = LDO\_EN = HS\_EN = 5 V, VOUT3 = 3.3 V, VOUT4 = 8.5 V, IOUT[1:4] = 0 A) Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$  unless noted otherwise. Min/Max values are guaranteed by test, design or statistical correlation.

| Parameter                               | Symbol                 | Conditions                                                                                                                               | Min   | Тур   | Max                                            | Unit |

|-----------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------------------------------------------------|------|

| LOW DROPOUT LINEAR REGULAT              | OR CONTR               | OLLER (LDO1, VOUT3) SPECIFICATION                                                                                                        | ONS   |       |                                                |      |

| Current Limit                           |                        |                                                                                                                                          |       |       |                                                |      |

| ISNS1+ leakage current                  | I <sub>ISNS1+</sub>    | SYS_EN = 0, T <sub>J</sub> = 25°C, V <sub>ISNS1+</sub> = 13.2 V                                                                          |       | 100   | 500                                            | nA   |

| ISNS1 - leakage current                 | I <sub>ISNS1-</sub>    | SYS_EN = 0, T <sub>J</sub> = 25°C, V <sub>ISNS1-</sub> = 13.2 V                                                                          |       | 100   | 500                                            | nA   |

| Short circuit threshold voltage         |                        | V <sub>LR_FB1</sub> % of V <sub>REF</sub>                                                                                                | 60    | 70    | 80                                             | %    |

| Short circuit blanking time             |                        | From rising edge of LDO_EN                                                                                                               | 10    | 12    | 14                                             | ms   |

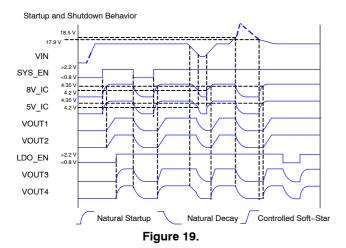

| Error Amplifier                         |                        |                                                                                                                                          |       |       |                                                |      |