NE5080

## DESCRIPTION

The NE5080 is the transmitter chip, of a two chip set, designed to be the heart of an FSK modem. (The NE5081 is the receiver chip.) The chips are compatible with the IEEE 802.4 standard for a "Single Channel Phase-Continuous-FSK Bus." The specifications shown in this data sheet are those guaranteed when the transmitter is tuned for the frequencies given in the 802 standard. However, both the NE5080 and the NE5081 may be used at other frequencies. The ratio of logic high to logic low frequencies requency.

### FEATURES

- Meets IEEE 802.4 standard

- · Data rates to several Megabaud

- Half or full duplex operation

- Jabber function on chip

## **APPLICATIONS**

- Local Area Networks

- Point-to-point communications

- Factory automation

- Process control

- Office automation

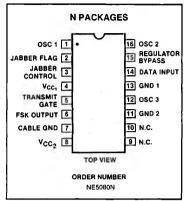

## PIN CONFIGURATION

## **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL & PARAMETER                                  | RATING                     | UNIT |  |

|-----------------------------------------------------|----------------------------|------|--|

| Supply Voltage V <sub>CC1</sub><br>V <sub>CC2</sub> | + 6                        | v    |  |

| Input Voltage Range (Data, Gate)                    | - 0.3 to + V <sub>CC</sub> | v    |  |

| Power Dissipation                                   | 800                        | mW   |  |

| Operating Temperature Range                         | 0 to +70                   | °C   |  |

| Max Junction Temperature                            | + 150                      | °C   |  |

| Storage Temperature Range                           | - 65 to + 150              | °C   |  |

| Lead Temperature (soldering, 10 sec)                | 300                        | °C   |  |

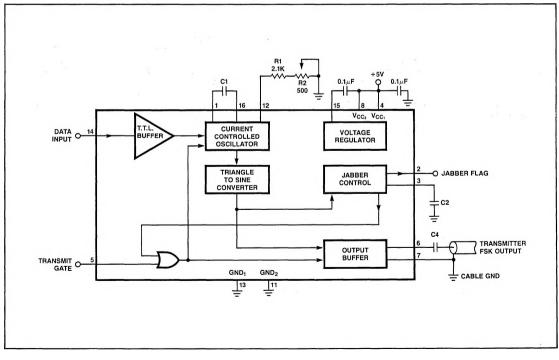

## **BLOCK DIAGRAM**

## GENERAL DESCRIPTION

The NE5080 is designed to transmit high frequency asynchronous data on coaxial cable, at rates from DC to 2 Megabaud (see note 1). The chip accepts serial data and transmits it as a periodic signal whose frequency depends on whether the data is high or low.

The device is meant to operate at a frequency of 6.25MHz for a logic high and 3.75MHz for a logic low (see note 2). The frequency is set up by external trimming components; however, the ratio of the high and low frequencies is set internally and cannot be altered.

The FSK output can be turned off by use of the transmit gate pin. When turned off, the transmitter has a high output impedance and the oscillator is disabled.

The length of time a transmitter can transmit can be controlled by the use of the Jabber control pin (see description of Jabber Control Pin).

#### **Jabber Control Pin**

During the time the transmitter is transmitting, this pin sources a current. This current can be used to set the maximum time that the transmitter can be on. There are three options that can be used:

- Use the current to charge a capacitor. When the voltage across the cap gets to approx. 1.4V the transmitter will turn off. A logic low applied to pin 3 will reset the Jabber function; an open collector output should be used for this purpose. A logic high applied to the pin will disable the transmitter.

- Use to externally sense the current and have external circuitry to control the length of time the transmitter is on.

## **NE5080 PIN FUNCTION**

| PIN | FUNCTION                                                                                                                                              |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | OSC 1—one end of an external capacitor used to set the carrier<br>frequency                                                                           |  |  |  |  |  |

| 2   | JABBER FLAG—this pin goes to a logic high if the transmitter<br>attempts to transmit for a longer time than allowed by the Jabber<br>control function |  |  |  |  |  |

| 3   | JABBER CONTROL—used to control transmit time. See note on Jabber<br>function                                                                          |  |  |  |  |  |

| 4   | V <sub>CC1</sub> —voltage supply                                                                                                                      |  |  |  |  |  |

| 5   | TRANSMIT GATE—a logic low on this pin will enable the transmitter;<br>a logic high will disable it                                                    |  |  |  |  |  |

| 6   | TRANSMITTER FSK OUTPUT                                                                                                                                |  |  |  |  |  |

| 7   | CABLE GROUND—the shield of the coax cable should be connected<br>to this pin and to Pin 11                                                            |  |  |  |  |  |

| 8   | V <sub>CC2</sub> —Connect to pin 4 close to device                                                                                                    |  |  |  |  |  |

| 9   | No Connection                                                                                                                                         |  |  |  |  |  |

| 10  | No Connection                                                                                                                                         |  |  |  |  |  |

| 11  | GROUND 2—connect to Analog ground close to device                                                                                                     |  |  |  |  |  |

| 12  | OSC 3—a variable resistor between this point and ground is used to set<br>the carrier frequencies.                                                    |  |  |  |  |  |

| 13  | GROUND 1—connect to Analog ground close to device                                                                                                     |  |  |  |  |  |

| 14  | DATA INPUT                                                                                                                                            |  |  |  |  |  |

| 15  | <b>REGULATOR BYPASS</b> —a bypass capacitor between this pin and $V_{CC_1}$ is required for the internal voltage regulator function                   |  |  |  |  |  |

| 16  | OSC 2—one end of a capacitor that is between pin 1 and pin 16 and is<br>used to set the carrier frequency                                             |  |  |  |  |  |

The pin can be tied to ground and is then not active. Transmission is then controlled solely by the signal at the transmit gate pin.

### Jabber Flag Pin

This pin will go to a logic high when the Jabber Control pin is used to shut off the transmitter. It will latch and can be reset by applying a logic low to the Jabber Control pin.

#### Notes:

- 1. The NE5080 is capable of transmitting up to 1 Megabaud of differential Manchester code at a center frequency of 5MHz.

- Although the chip is designed to meet the requirements of IEEE standard 802.4 (Token-Passing Single Channel Phase-Continuous-FSK Bus), it can be used at other frequencies. See "Determining Component Values."

| PARAMETER                                                                  | SYMBOL                                                                   | TEST CONDITIONS                                                     | NE5080 |      |                    |                            |  |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------|--------|------|--------------------|----------------------------|--|

| PARAMETER                                                                  | STMBUL                                                                   | SYMBOL TEST CONDITIONS                                              |        | Тур. | Max.               | UNIT                       |  |

| Output Frequency (Logic High)                                              | F <sub>1</sub>                                                           | Data Input ≥2.0V (See Note 1)                                       | 6.17   | 6.25 | 6.33               | MHz                        |  |

| Output Frequency (Logic Low)                                               | Fo                                                                       | Data Input ≤0.8V (See Note 1)                                       | 3.67   | 3.75 | 3.83               | MHz                        |  |

| Output Amplitude                                                           | V <sub>0</sub>                                                           | Data Input ≥2.0V or ≤0.8V<br>Output Load = 37.5Ω                    | 0.5    |      | 1.0                | V <sub>RMS</sub>           |  |

| Output Impedance (gated off)                                               | Roff                                                                     | Transmit gate ≥2.0V                                                 | 100    |      |                    | КΩ                         |  |

| Output Impedance (gated on)                                                | R <sub>on</sub>                                                          | Transmit gate ≤0.8V                                                 | 1      |      | 37.5               | Ω                          |  |

| Output Capacitance                                                         | C <sub>0</sub>                                                           | Transmit gate ≥2.0V or ≤0.8V                                        |        |      | 10                 | pF                         |  |

| Feed through                                                               | VF                                                                       | Transmit gate ≥2.0V<br>2.0MHz sq. wave (TTL Levels) Input           |        |      | 1                  | mV <sub>RMS</sub>          |  |

| Jabber Current                                                             | l,                                                                       | Transmit gate ≤0.8V<br>Input ≥2.0V or ≤0.8V                         |        | 1.25 |                    | μΑ                         |  |

| Supply Current                                                             | lcc                                                                      | V <sub>CC1</sub> connected to V <sub>CC2</sub>                      |        | 75   | 100                | mA                         |  |

| LOGIC LEVELS                                                               |                                                                          |                                                                     | 0      |      |                    | <b>.</b>                   |  |

| Data Input<br>Logic High<br>Logic Low<br>Input Current<br>Input Current    | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub><br>I <sub>IL</sub> | Input high voltage<br>Input low voltage<br>Vin = 2.4V<br>Vin = 0.4V | 2.0    |      | 0.8<br>40<br>- 1.6 | Volts<br>Volts<br>μA<br>mA |  |

| Transmit Gate<br>Logic High<br>Logic Low<br>Input Current<br>Input Current | V <sub>IH</sub><br>VIL<br>I <sub>IH</sub><br>I <sub>IL</sub>             | Input high voltage<br>Input low voltage<br>VG = 2.4V<br>VG = 0.4V   | 2.0    |      | 0.8<br>40<br>- 1.6 | Volts<br>Volts<br>μA<br>mA |  |

| Jabber Flag<br>Logic High<br>Logic Low                                     | V <sub>OH</sub><br>V <sub>OL</sub>                                       | IOH = -400µA<br>IOL=4.0mA                                           | 2.4    |      | 0.4                | Volts<br>Volts             |  |

| Jabber Control<br>Logic High<br>Logic Low                                  | V <sub>IH</sub><br>VIL                                                   | Input high voltage<br>Input low voltage                             | 2.0    |      | 0.8                | Volts<br>Volts             |  |

## **ELECTRICAL CHARACTERISTICS** $V_{CC_{1,2}} = 4.75 - 5.25V$ $T_A = 0^{\circ}C$ to $+70^{\circ}C$

NOTE

(1) Tuned per instructions in Applications section.

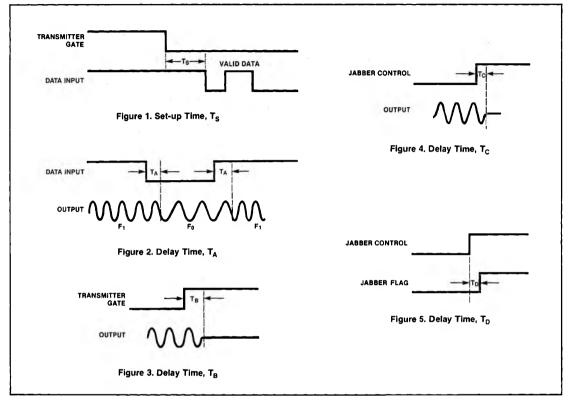

## AC ELECTRICAL CHARACTERISTICS

| SYMBOL & PARAMETER                              | TO FROM                | CDOM               |          | NE5080 |      |      |    |

|-------------------------------------------------|------------------------|--------------------|----------|--------|------|------|----|

|                                                 |                        | TEST CONDITIONS    | Min.     | Typ.   | Max. | UNIT |    |

| Set Up Time — T <sub>S</sub>                    | Data In                | Gate On            | Figure 1 | 2      | 0.1  |      | μS |

| Delay Time — T <sub>A</sub>                     | Output Freq.<br>Change | Data<br>Transition | Figure 2 |        |      | 150  | nS |

| Delay Time — T <sub>B</sub>                     | Output<br>Disabled     | Gate Off           | Figure 3 |        | 0.4  | 2    | μS |

| Delay Time — T <sub>C</sub>                     | Output<br>Disabled     | Jabber<br>Control  | Figure 4 |        |      | 100  | nS |

| Delay Time — T <sub>D</sub>                     | Jabber<br>Flag         | Jabber<br>Control  | Figure 5 |        |      | 100  | nS |

| Jabber Control Reset<br>Pulse Width (Logic Low) |                        |                    |          | 100    |      |      | nS |

TIMING DIAGRAMS