### NE/SA/SE5205A

#### DESCRIPTION

The NE/SA/SE5205A family of wideband amplifiers replace the NE/SA/SE5205 family. The 'A' parts are fabricated on a rugged 2µm bipolar process featuring excellent statistical process control. Electrical performance is nominally identical to the original parts.

The NE/SA/SE5205A is a high-frequency amplifier with a fixed insertion gain of 20dB. The gain is flat to ±0.5dB from DC to 450MHz, and the -3dB bandwidth is greater than 600MHz in the EC package. This performance makes the amplifier ideal for cable TV applications. For lower frequency applications, the part is also available in industrial standard dual in-line and small outline packages. The NE/SA/SE5205A operates with a single supply of 6V, and only draws 24mA of supply current, which is much less than comparable hybrid parts. The noise figure is 4.8dB in a 75 $\Omega$  system and 6dB in a 50 $\Omega$  system.

Until now, most RF or high-frequency designers had to settle for discrete or hybrid solutions to their amplification problems. Most of these solutions required trade-offs that the designer had to accept in order to use high-frequency gain stages. These include high-power consumption, large component count, transformers, large packages with heat sinks, and high part cost. The NE/SA/SE5205A solves these problems by incorporating a wide-band amplifier on a single monolithic chip.

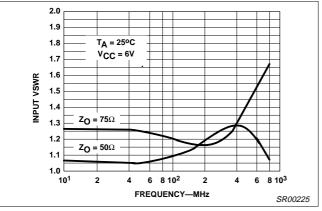

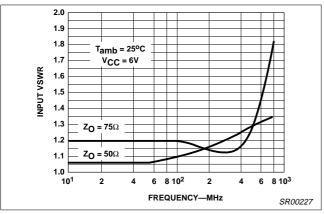

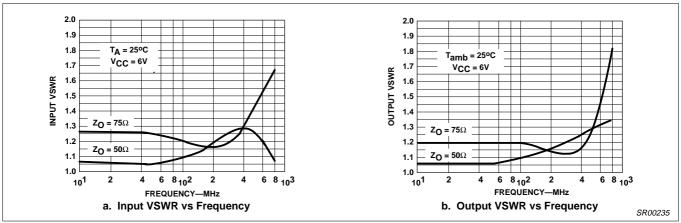

The part is well matched to 50 or 75 $\Omega$  input and output impedances. The Standing Wave Ratios in 50 and 75 $\Omega$  systems do not exceed 1.5 on either the input or output from DC to the -3dB bandwidth limit.

Since the part is a small monolithic IC die, problems such as stray capacitance are minimized. The die size is small enough to fit into a very cost-effective 8-pin small-outline (SO) package to further reduce parasitic effects.

No external components are needed other than AC coupling capacitors because the NE/SA/SE5205A is internally compensated and matched to 50 and 75 $\Omega$ . The amplifier has very good distortion specifications, with second and third-order intermodulation intercepts of +24dBm and +17dBm respectively at 100MHz.

The device is ideally suited for  $75\Omega$  cable television applications such as decoder boxes, satellite receiver/decoders, and front-end amplifiers for TV receivers. It is also useful for amplified splitters and antenna amplifiers.

The part is matched well for  $50\Omega$  test equipment such as signal generators, oscilloscopes, frequency counters and all kinds of signal analyzers. Other applications at  $50\Omega$  include mobile radio, CB radio and data/video transmission in fiber optics, as well as broad-band LANs and telecom systems. A gain greater than 20dB can be achieved by cascading additional NE/SA/SE5205As in series as required, without any degradation in amplifier stability.

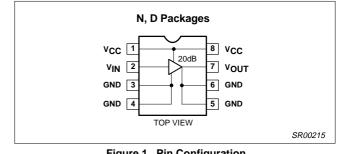

#### **PIN CONFIGURATIONS**

Figure 1. Pin Configuration

#### FEATURES

- 600MHz bandwidth

- 20dB insertion gain

- 4.8dB (6dB) noise figure ZO=75Ω (ZO=50Ω)

- No external components required

- Input and output impedances matched to  $50/75\Omega$  systems

- Surface mount package available

- MIL-STD processing available

- 2000V ESD protection

#### APPLICATIONS

- 75Ω cable TV decoder boxes

- Antenna amplifiers

- Amplified splitters

- Signal generators

- Frequency counters

- Oscilloscopes

- Signal analyzers

- Broad-band LANs

- Fiber-optics

- Modems

- Mobile radio

- Security systems

- Telecommunications

#### ORDERING INFORMATION

| DESCRIPTION                              | TEMPERATURE RANGE | ORDER CODE | DWG #   |

|------------------------------------------|-------------------|------------|---------|

| 8-Pin Plastic Small Outline (SO) package | 0 to +70°C        | NE5205AD   | SOT96-1 |

| 8-Pin Plastic Dual In-Line Package (DIP) | 0 to +70°C        | NE5205AN   | SOT97-1 |

| 8-Pin Plastic Small Outline (SO) package | -40 to +85°C      | SA5205AD   | SOT96-1 |

| 8-Pin Plastic Dual In-Line Package (DIP) | -40 to +85°C      | SA5205AN   | SOT97-1 |

| 8-Pin Plastic Dual In-Line Package (DIP) | -55 to +125°C     | SE5205AN   | SOT97-1 |

## NE/SA/SE5205A

Product specification

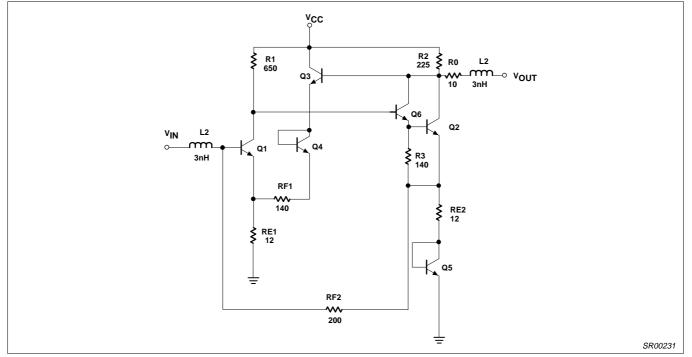

Figure 2. Equivalent Schematic

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | PARAMETER                                                                | RATING      | UNIT             |

|-------------------|--------------------------------------------------------------------------|-------------|------------------|

| V <sub>CC</sub>   | Supply voltage                                                           | 9           | V                |

| V <sub>AC</sub>   | AC input voltage                                                         | 5           | V <sub>P-P</sub> |

| T <sub>A</sub>    | Operating ambient temperature range                                      |             |                  |

|                   | NE grade                                                                 | 0 to +70    | °C               |

|                   | SA grade                                                                 | -40 to +85  | °C               |

|                   | SE grade                                                                 | -55 to +125 | °C               |

| P <sub>DMAX</sub> | Maximum power dissipation, $T_A=25^{\circ}C$ (still-air) <sup>1, 2</sup> |             |                  |

|                   | N package                                                                | 1160        | mW               |

|                   | D package                                                                | 780         | mW               |

NOTES:

1. Derate above 25°C, at the following rates:

N package at 9.3mW/°C

D package at 6.2mW/°C

2. See "Power Dissipation Considerations" section.

### NE/SA/SE5205A

#### **DC ELECTRICAL CHARACTERISTICS**

$V_{CC}{=}6V,$   $Z_{S}{=}Z_{L}{=}Z_{O}{=}50\Omega$  and  $T_{A}{=}25^{\circ}C$  in all packages, unless otherwise specified.

| SYMBOL           | PARAMETER                                       | TEST CONDITIONS              |            | SE5205A  |            |            | NE/SA5205A |            |          |

|------------------|-------------------------------------------------|------------------------------|------------|----------|------------|------------|------------|------------|----------|

|                  |                                                 |                              | Min        | Тур      | Max        | Min        | Тур        | Max        | UNIT     |

| V <sub>CC</sub>  | Operating supply voltage range                  | Over temperature             | 5<br>5     |          | 6.5<br>6.5 | 5<br>5     |            | 8<br>8     | V<br>V   |

| I <sub>CC</sub>  | Supply current                                  | Over temperature             | 20<br>19   | 25<br>25 | 32<br>33   | 20<br>19   | 25<br>25   | 32<br>33   | mA<br>mA |

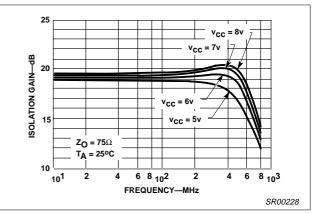

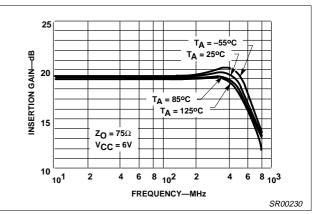

| S21              | Insertion gain                                  | f=100MHz<br>Over temperature | 17<br>16.5 | 19       | 21<br>21.5 | 17<br>16.5 | 19         | 21<br>21.5 | dB       |

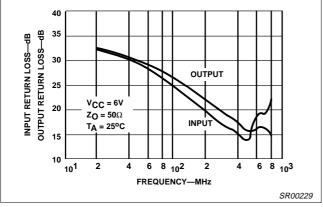

| S11              | Input return loss                               | f=100MHz D, N                |            | 25       |            |            | 25         |            | dB       |

|                  |                                                 | DC - f <sub>MAX</sub> D, N   | 12         |          |            | 12         |            |            |          |

| 0.00             | Output return loss                              | f=100MHz D, N                |            | 27       |            |            | 27         |            | dB       |

| S22              |                                                 | DC - f <sub>MAX</sub>        | 12         |          |            | 12         |            |            |          |

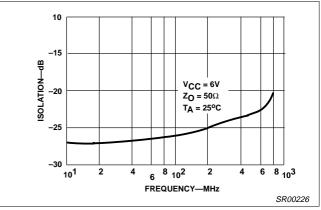

| S12              | Isolation                                       | f=100MHz                     |            | -25      |            |            | -25        |            | dB       |

| 512              |                                                 | DC - f <sub>MAX</sub>        | -18        |          |            | -18        |            |            |          |

| t <sub>R</sub>   | Rise time                                       |                              |            | 500      |            |            | 500        |            | ps       |

| t <sub>P</sub>   | Propagation delay                               |                              |            | 500      |            |            | 500        |            | ps       |

| BW               | Bandwidth                                       | ±0.5dB D, N                  |            | 300      |            |            | 450        |            | MHz      |

| f <sub>MAX</sub> | Bandwidth                                       | -3dB D, N                    |            |          |            | 550        |            |            | MHz      |

|                  | Noise figure (75Ω)                              | f=100MHz                     |            | 4.8      |            |            | 4.8        |            | dB       |

|                  | Noise figure (50Ω)                              | f=100MHz                     |            | 6.0      |            |            | 6.0        |            | dB       |

|                  | Saturated output power                          | f=100MHz                     |            | +7.0     |            |            | +7.0       |            | dBm      |

|                  | 1dB gain compression                            | f=100MHz                     |            | +4.0     |            |            | +4.0       |            | dBm      |

|                  | Third-order intermodulation intercept (output)  | f=100MHz                     |            | +17      |            |            | +17        |            | dBm      |

|                  | Second-order intermodulation intercept (output) | f=100MHz                     |            | +24      |            |            | +24        |            | dBm      |

### NE/SA/SE5205A

### NE/SA/SE5205A

Figure 11. Input VSWR vs Frequency

Figure 12. Output VSWR vs Frequency

Figure 13. Input (S<sub>11</sub>) and Output (S<sub>22</sub>) Return Loss vs Frequency

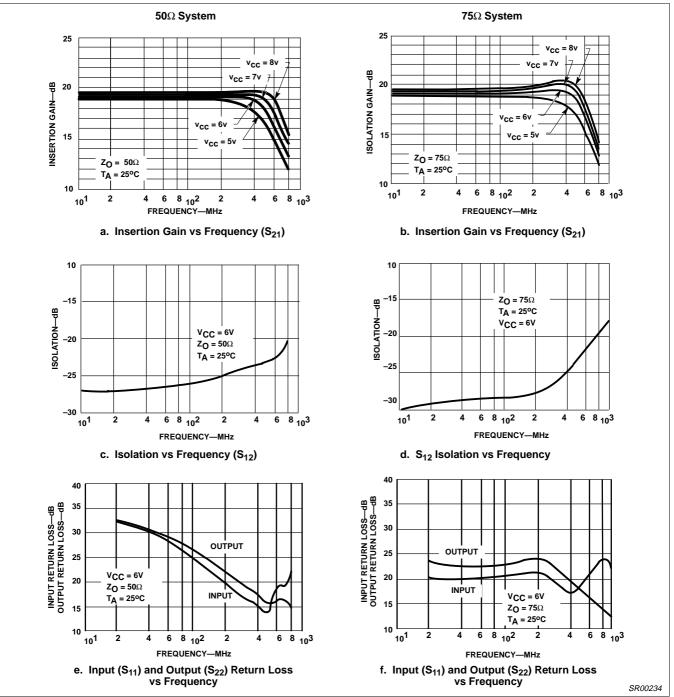

Figure 15. Insertion Gain vs Frequency (S<sub>21</sub>)

Figure 16. Insertion Gain vs Frequency (S<sub>21</sub>)

#### NE/SA/SE5205A

#### THEORY OF OPERATION

The design is based on the use of multiple feedback loops to provide wide-band gain together with good noise figure and terminal impedance matches. Referring to the circuit schematic in Figure 17, the gain is set primarily by the equation:

$$\frac{V_{OUT}}{V_{IN}} = \frac{(R_{F1} + R_{E1})}{R_{F1}}$$

(1)

which is series-shunt feedback. There is also shunt-series feedback due to  $\mathsf{R}_{F2}$  and  $\mathsf{R}_{E2}$  which aids in producing wideband terminal impedances without the need for low value input shunting resistors that would degrade the noise figure. For optimum noise performance,  $\mathsf{R}_{E1}$  and the base resistance of  $\mathsf{Q}_1$  are kept as low as possible while  $\mathsf{R}_{F2}$  is maximized.

The noise figure is given by the following equation:

NF =

$$10 \log \left[ 1 + \left[ \frac{r_{b} + R_{E1} + \frac{KT}{2ql_{C1}}}{R_{0}} \right] \right] dB$$

(2)

where I<sub>C1</sub>=5.5mA, R<sub>E1</sub>=12 $\Omega$ , r<sub>b</sub>=130 $\Omega$ , KT/q=26mV at 25°C and R<sub>0</sub>=50 for a 50 $\Omega$  system and 75 for a 75 $\Omega$  system.

The DC input voltage level VIN can be determined by the equation:

VIN=VBE1+(IC1+IC3) RE1

where  $R_{E1}{=}12\Omega,$   $V_{BE}{=}0.8V,$   $I_{C1}{=}5mA$  and  $I_{C3}{=}7mA$  (currents rated at  $V_{CC}{=}6V).$

Under the above conditions, VIN is approximately equal to 1V.

Level shifting is achieved by emitter-follower Q<sub>3</sub> and diode Q<sub>4</sub> which provide shunt feedback to the emitter of Q<sub>1</sub> via R<sub>F1</sub>. The use of an emitter-follower buffer in this feedback loop essentially eliminates problems of shunt feedback loading on the output. The value of R<sub>F1</sub>=140 $\Omega$  is chosen to give the desired nominal gain. The DC output voltage V<sub>OUT</sub> can be determined by:

$V_{OUT} = V_{CC} - (I_{C2} + I_{C6})R2, (4)$

where V<sub>CC</sub>=6V, R<sub>2</sub>=225 $\Omega$ , I<sub>C2</sub>=8mA and I<sub>C6</sub>=5mA.

From here it can be seen that the output voltage is approximately 3.1V to give relatively equal positive and negative output swings. Diode  $Q_5$  is included for bias purposes to allow direct coupling of  $R_{F2}$  to the base of  $Q_1$ . The dual feedback loops stabilize the DC operating point of the amplifier.

The output stage is a Darlington pair ( $Q_6$  and  $Q_2$ ) which increases the DC bias voltage on the input stage ( $Q_1$ ) to a more desirable value, and also increases the feedback loop gain. Resistor  $R_0$ optimizes the output VSWR (Voltage Standing Wave Ratio). Inductors  $L_1$  and  $L_2$  are bondwire and lead inductances which are roughly 3nH. These improve the high-frequency impedance matches at input and output by partially resonating with 0.5pF of pad and package capacitance.

Figure 17. Schematic Diagram

#### NE/SA/SE5205A

#### POWER DISSIPATION CONSIDERATIONS

When using the part at elevated temperature, the engineer should consider the power dissipation capabilities of each package.

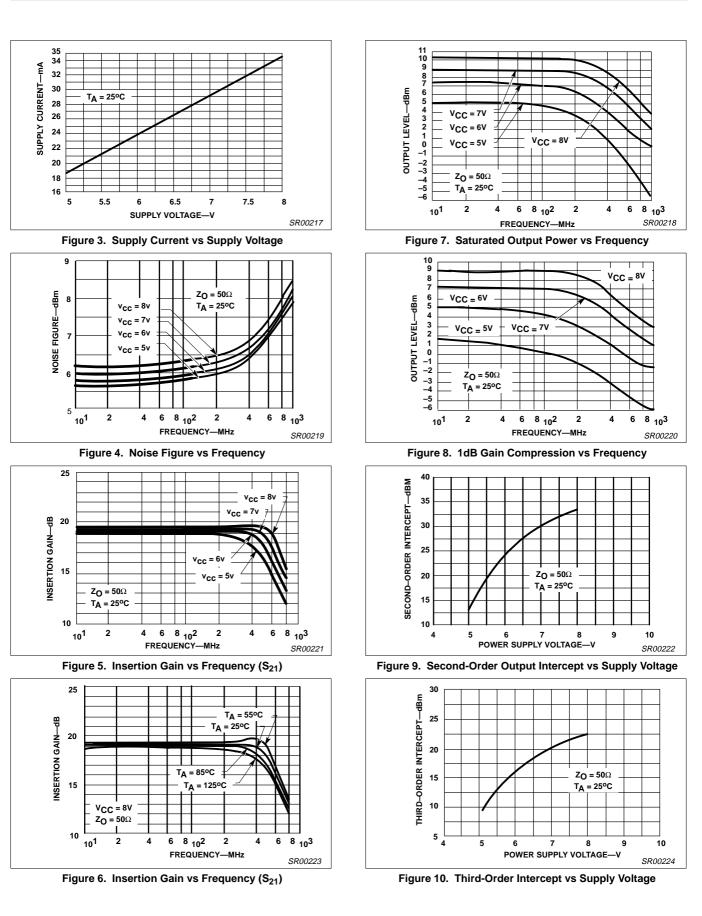

At the nominal supply voltage of 6V, the typical supply current is 25mA (32mA Max). For operation at supply voltages other than 6V, see Figure 3 for  $I_{CC}$  versus  $V_{CC}$  curves. The supply current is inversely proportional to temperature and varies no more than 1mA between 25°C and either temperature extreme. The change is 0.1% per over the range.

The recommended operating temperature ranges are air-mount specifications. Better heat sinking benefits can be realized by mounting the D package body against the PC board plane.

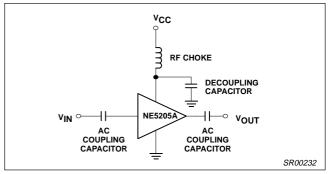

#### PC BOARD MOUNTING

In order to realize satisfactory mounting of the NE5205A to a PC board, certain techniques need to be utilized. The board must be double-sided with copper and all pins must be soldered to their respective areas (i.e., all GND and  $V_{CC}$  pins on the SO package). The power supply should be decoupled with a capacitor as close to the V<sub>CC</sub> pins as possible and an RF choke should be inserted between the supply and the device. Caution should be exercised in the connection of input and output pins. Standard microstrip should be observed wherever possible. There should be no solder bumps or burrs or any obstructions in the signal path to cause launching problems. The path should be as straight as possible and lead lengths as short as possible from the part to the cable connection. Another important consideration is that the input and output should be AC coupled. This is because at V<sub>CC</sub>=6V, the input is approximately at 1V while the output is at 3.1V. The output must be decoupled into a low impedance system or the DC bias on the output of the amplifier will be loaded down causing loss of output power. The easiest way to decouple the entire amplifier is by soldering a high frequency chip capacitor directly to the input and

output pins of the device. This circuit is shown in Figure 18. Follow these recommendations to get the best frequency response and noise immunity. The board design is as important as the integrated circuit design itself.

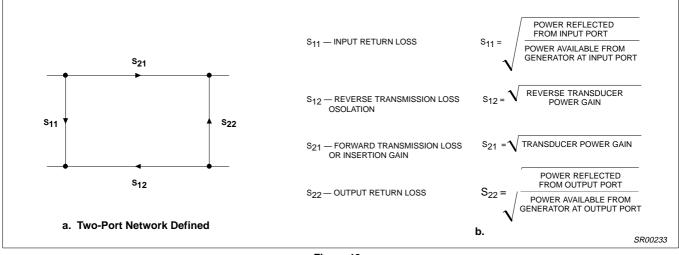

#### SCATTERING PARAMETERS

The primary specifications for the NE/SA/SE5205A are listed as S-parameters. S-parameters are measurements of incident and reflected currents and voltages between the source, amplifier and load as well as transmission losses. The parameters for a two-port network are defined in Figure 19.

Actual S-parameter measurements using an HP network analyzer (model 8505A) and an HP S-parameter tester (models 8503A/B) are shown in Figure 20.

Values for the figures below are measured and specified in the data sheet to ease adaptation and comparison of the NE/SA/SE5205A to other high-frequency amplifiers.

Figure 18. Circuit Schematic for Coupling and Power Supply Decoupling

Figure 19.

### NE/SA/SE5205A

#### NE/SA/SE5205A

The most important parameter is  $S_{21}$ . It is defined as the square root of the power gain, and, in decibels, is equal to voltage gain as shown below:

#### $Z_D=Z_{IN}=Z_{OUT}$ for the NE/SA/SE5205A

$$P_{IN} + \frac{V_{IN}}{Z_{D}} \circ \underbrace{P_{IN}}_{P_{IN}} + \frac{V_{OUT}}{Z_{D}} \circ \underbrace{P_{OUT}}_{P_{OUT}} + \frac{V_{OUT}}{Z_{D}} \circ \underbrace{P_{OUT}}_{P_{OUT}} + \frac{V_{OUT}}{Z_{D}} \circ \underbrace{P_{OUT}}_{P_{IN}} + \frac{V_{OUT}}{Z_{D}} \circ \underbrace{P_{OUT}}_{P_{IN}} + \underbrace{P_{OUT}}_{P_{IN}} \circ \underbrace{P_{OUT}}_{P_{IN}} \circ$$

P<sub>I</sub>=V<sub>I</sub><sup>2</sup>

P<sub>I</sub>=Insertion Power Gain

V<sub>I</sub>=Insertion Voltage Gain

Measured value for the NE/SA/SE5205A =  $|S_{21}|^2$  = 100

$$\therefore P_{I} = \frac{P_{OUT}}{P_{IN}} = |S_{21}|^{2} = 100$$

and  $V_{I} = \frac{V_{OUT}}{V_{IN}} = \sqrt{P_{I}} = S_{21} = 10$

In decibels:

P<sub>I(dB)</sub> =10 Log | S<sub>21</sub> | <sup>2</sup> = 20dB

$V_{I(dB)} = 20 \text{ Log } S_{21} = 20 \text{ dB}$

$\therefore P_{I(dB)} = V_{I(dB)} = S_{21(dB)} = 20dB$

Also measured on the same system are the respective voltage standing wave ratios. These are shown in Figure 21. The VSWR can be seen to be below 1.5 across the entire operational frequency range.

Relationships exist between the input and output return losses and the voltage standing wave ratios. These relationships are as follows:

$\begin{array}{l} \text{INPUT RETURN LOSS=S_{11} dB} \\ \text{S}_{11} \text{dB=20 Log} \mid \text{S}_{11} \mid \end{array}$

OUTPUT RETURN LOSS= $S_{22}dB$  $S_{22}dB=20 \text{ Log } | S_{22} |$

INPUT VSWR=≤1.5

OUTPUT VSWR=≤1.5

## 1dB GAIN COMPRESSION AND SATURATED OUTPUT POWER

The 1dB gain compression is a measurement of the output power level where the small-signal insertion gain magnitude decreases

1dB from its low power value. The decrease is due to nonlinearities in the amplifier, an indication of the point of transition between small-signal operation and the large signal mode.

The saturated output power is a measure of the amplifier's ability to deliver power into an external load. It is the value of the amplifier's output power when the input is heavily overdriven. This includes the sum of the power in all harmonics.

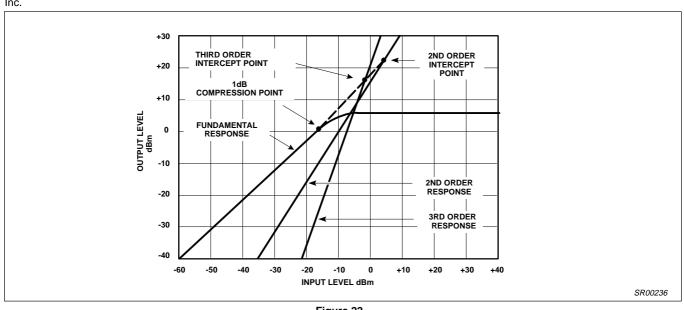

#### INTERMODULATION INTERCEPT TESTS

The intermodulation intercept is an expression of the low level linearity of the amplifier. The intermodulation ratio is the difference in dB between the fundamental output signal level and the generated distortion product level. The relationship between intercept and intermodulation ratio is illustrated in Figure 22, which shows product output levels plotted versus the level of the fundamental output for two equal strength output signals at different frequencies. The upper line shows the fundamental output plotted against itself with a 1dB to 1dB slope. The second and third order products lie below the fundamentals and exhibit a 2:1 and 3:1 slope, respectively.

The intercept point for either product is the intersection of the extensions of the product curve with the fundamental output.

The intercept point is determined by measuring the intermodulation ratio at a single output level and projecting along the appropriate product slope to the point of intersection with the fundamental. When the intercept point is known, the intermodulation ratio can be determined by the reverse process. The second order IMR is equal to the difference between the second order intercept and the fundamental output level. The third order IMR is equal to twice the difference between the third order intercept and the fundamental output level. These are expressed as:

IP2=POUT+IMR2

IP3=POUT+IMR3/2

where POUT is the power level in dBm of each of a pair of equal level fundamental output signals, IP2 and IP3 are the second and third order output intercepts in dBm, and IMR2 and IMR3 are the second and third order intermodulation ratios in dB. The intermodulation intercept is an indicator of intermodulation performance only in the small signal operating range of the amplifier. Above some output level which is below the 1dB compression point, the active device moves into large-signal operation. At this point the intermodulation products no longer follow the straight line output slopes, and the intercept description is no longer valid. It is therefore important to measure IP2 and IP3 at output levels well below 1dB compression. One must be careful, however, not to select too low levels because the test equipment may not be able to recover the signal from the noise. For the NE/SA/SE5205A we have chosen an output level of -10.5dBm with fundamental frequencies of 100.000 and 100.01MHz, respectively.

## NE/SA/SE5205A

Figure 21. Input/Output VSWR vs Frequency

# ADDITIONAL READING ON SCATTERING PARAMETERS

For more information regarding S-parameters, please refer to High-Frequency Amplifiers by Ralph S. Carson of the University of Missouri, Rolla, Copyright 1985; published by John Wiley & Sons, Inc. "S-Parameter Techniques for Faster, More Accurate Network Design", HP App Note 95-1, Richard W. Anderson, 1967, HP Journal.

"S-Parameter Design", HP App Note 154, 1972.

Figure 22.