### **NE/SE5560**

#### DESCRIPTION

The NE/SE5560 is a control circuit for use in switched-mode power supplies. This single monolithic chip incorporates all the control and housekeeping (protection) functions required in switched-mode power supplies, including an internal temperature-compensated reference source, internal Zener references, sawtooth generator, pulse-width modulator, output stage and various protection circuits.

#### FEATURES

- Stabilized power supply

- Temperature-compensated reference source

- Sawtooth generator

- Pulse-width modulator

- Remote on/off switching

- Current limiting

- Low supply voltage protection

- Loop fault protection

- Demagnetization/overvoltage protection

- Maximum duty cycle clamp

- Feed-forward control

- External synchronization

#### **ORDERING INFORMATION**

| DESCRIPTION                                      | TEMPERATURE RANGE | ORDER CODE | DWG #    |

|--------------------------------------------------|-------------------|------------|----------|

| 16-Pin Plastic Dual In-Line Package (DIP)        | 0 to 70°C         | NE5560N    | SOT38-4  |

| 16-Pin Plastic Small Outline Large (SOL) Package | 0°C to 70°C       | NE5560D    | SOT162-1 |

| 16-Pin Plastic Dual In-Line Package (DIP)        | -55°C to 125°C    | SE5560N    | SOT38-4  |

| 16-Pin Cerdip Dual In-Line Package (CERDIP)      | -55°C to 125°C    | SE5560F    | 0582B    |

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                           | RATING                | UNIT |

|------------------|-------------------------------------|-----------------------|------|

|                  | Supply <sup>1</sup>                 |                       |      |

| V <sub>CC</sub>  | Voltage-forced mode                 | +18                   | V    |

| I <sub>CC</sub>  | Current-fed mode                    | 30                    | mA   |

|                  | Output transistor (at 20-30V max)   |                       |      |

| I <sub>OUT</sub> | Output current                      | 40                    | mA   |

|                  | Collector voltage (Pin 15)          | V <sub>CC</sub> +1.4V | V    |

|                  | Max. emitter voltage (Pin 14)       | +5                    | V    |

| T <sub>A</sub>   | Operating ambient temperature range |                       |      |

|                  | SE5560                              | -55 to +125           | °C   |

|                  | NE5560                              | 0 to 70               | °C   |

| T <sub>STG</sub> | Storage temperature range           | -65 to +150           | °C   |

NOTES:

1. Does not include current for timing resistors or capacitors.

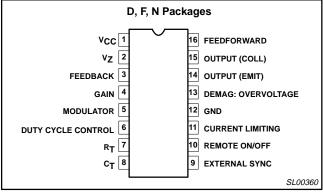

**PIN CONFIGURATION**

Figure 1. Pin Configuration

1

#### Product specification

### NE/SE5560

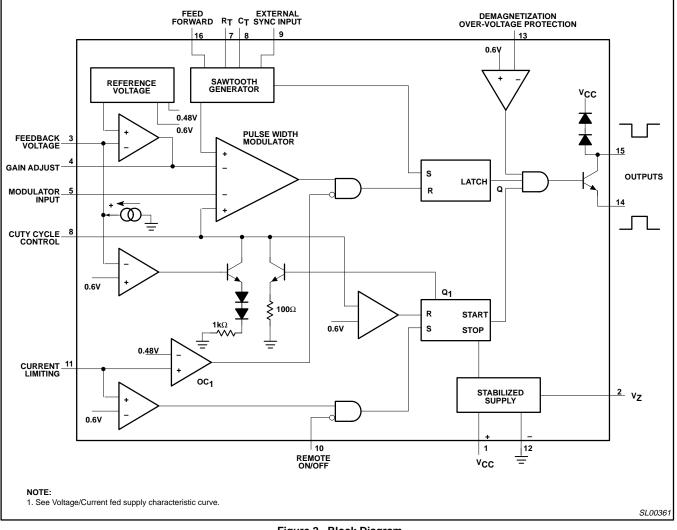

#### **BLOCK DIAGRAM**

Figure 2. Block Diagram

## NE/SE5560

## DC ELECTRICAL CHARACTERISTICS

$T_A{=}25^{\circ}C,\,V_{CC}{=}12V\!,$  unless otherwise specified.

| SYMBOL            | PARAMETER                                          | TEST CONDITIONS                         | SE5560 |      |      | NE5560   |      |      | UNIT                     |

|-------------------|----------------------------------------------------|-----------------------------------------|--------|------|------|----------|------|------|--------------------------|

|                   |                                                    |                                         | Min    | Тур  | Max  | Min      | Тур  | Max  |                          |

| Reference s       | sections                                           |                                         |        |      |      |          |      |      |                          |

| $V_{REF}$         | Internal reference voltage                         | 25°C                                    | 3.69   | 3.72 | 3.81 | 3.57     | 3.72 | 3.95 | V                        |

|                   |                                                    | Over temperature                        | 3.65   |      | 3.85 | 3.53     |      | 4.00 | V                        |

|                   | Temperature coefficient of V <sub>REF</sub>        |                                         |        | -100 |      |          | -100 |      | ppm/°C                   |

| VZ                | Internal Zener reference                           | I <sub>L</sub> =-7mA                    | 7.8    | 8.4  | 8.8  | 7.8      | 8.4  | 8.8  | V                        |

|                   | Temperature coefficient of $V_Z$                   |                                         |        | 200  |      |          | 200  |      | ppm/°C                   |

| Oscillator s      | ection                                             | -                                       |        |      |      |          |      |      |                          |

|                   | Frequency range                                    | Over temperature                        | 50     |      | 100k | 50       |      | 100k | Hz                       |

|                   | Initial accuracy oscillator                        | R=5kΩ                                   |        | 5    |      |          | 5    |      | %                        |

|                   | Duty cycle range                                   | f <sub>O</sub> =20kHz                   | 0      |      | 98   | 0        |      | 98   | %                        |

| Modulator         | -                                                  | -                                       |        |      |      |          |      |      |                          |

|                   | Modulation input current                           | Voltage at Pin 5=2V Over<br>temperature |        | 0.2  | 20   |          | 0.2  | 20   | μΑ                       |

| Housekeep         | ing function                                       |                                         |        |      |      |          |      |      |                          |

| he se             | Pin 6, input current                               | At 2V                                   |        |      |      |          |      |      |                          |

| I <sub>IN</sub> , |                                                    | Over temperature                        |        | 0.2  | 20   |          | 0.2  | 20   | μΑ                       |

|                   |                                                    |                                         |        |      |      |          |      |      |                          |

|                   | Pin 6, duty cycle limit control                    | For 50% max duty cycle                  |        |      |      |          |      |      |                          |

|                   |                                                    | 15kHz to 50kHz/41% of Vz                | 40     | 50   | 60   | 40       | 50   | 60   | % of duty                |

|                   |                                                    |                                         | 40     | 00   |      | 40       | 00   | 00   | cycle                    |

|                   | Pin 1, low supply voltage<br>protection thresholds |                                         | 8      | 9.0  | 10.5 | 8        | 9.0  | 10.5 | V                        |

|                   | Pin 3, feedback loop protection trip threshold     |                                         | 400    | 600  | 720  | 400      | 600  | 720  | mV                       |

|                   |                                                    | At 2V                                   |        |      |      |          |      |      |                          |

|                   | Pin 3, pull-up current                             |                                         | -7     | -15  | -35  | -7       | -15  | -35  | μA                       |

|                   | Pin 13,                                            |                                         |        |      |      |          |      |      |                          |

|                   | demagnetization/over-voltage                       | Over temperature                        | 470    | 600  | 720  | 470      | 600  | 720  | mV                       |

|                   | protection trip on threshold                       |                                         |        |      |      |          |      |      |                          |

|                   |                                                    | At 0.25V                                |        |      | 10   |          |      | 10   |                          |

| I <sub>IN</sub>   | Pin 13, input current                              | 25°C                                    |        | -0.6 | -10  |          | -0.6 | -10  | μA                       |

|                   | Die 40. faard fan waard date weele                 | Over temperature                        | l      |      | -20  | <b> </b> |      | -20  | 0(                       |

|                   | Pin 16, feed-forward duty cycle control            | Voltage at Pin 16=2V <sub>Z</sub>       | 30     | 40   | 50   | 30       | 40   | 50   | % original<br>duty cycle |

|                   |                                                    | At 16V, V <sub>CC</sub> =18V            |        |      |      |          |      |      |                          |

|                   | *Pin 16, feed-forward input current                | 25°C                                    |        | 0.2  | 5    |          | 0.2  | 5    | μA                       |

|                   |                                                    | Over temperature                        |        |      | 10   |          |      | 10   | μA                       |

| External sy       | nchronization                                      | -                                       | -      |      | -    | -        |      |      |                          |

|                   | Pin 9 Off                                          |                                         | 0      |      | 0.8  | 0        |      | 0.8  | V                        |

|                   | On                                                 |                                         | 2      |      | Vz   | 2        |      | VZ   | V                        |

|                   | Sink current                                       | Voltage at Pin 9=0V, 25°C               |        | -65  | -100 |          | -65  | -125 | μA                       |

|                   |                                                    | Over temperature                        |        |      | -125 |          |      | -125 | μΑ                       |

| Remote            | •                                                  | · · ·                                   | •      |      | •    | •        |      |      |                          |

|                   | Pin 10 Off                                         |                                         | 0      |      | 0.8  | 0        |      | 0.8  | V                        |

|                   | On                                                 |                                         | 2      |      | Vz   | 2        |      | Vz   | V                        |

|                   |                                                    | At 0V                                   |        |      |      |          |      | -    |                          |

|                   | Sink current                                       | 25°C                                    |        | -85  | -100 |          | -85  | -125 | μA                       |

|                   |                                                    | Over temperature                        |        |      | -125 |          |      | -125 | μA                       |

|                   | Į                                                  |                                         | L      | I    |      | L        | I    |      | μι                       |

## NE/SE5560

#### DC ELECTRICAL CHARACTERISTICS (Continued)

| OVMDO           | PARAMETER                                                                                                      | TEST CONDITIONS                                                  | SE5560 |       |       | NE5560 |       |       |      |

|-----------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------|-------|-------|--------|-------|-------|------|

| SYMBOL          |                                                                                                                |                                                                  | Min    | Тур   | Max   | Min    | Тур   | Max   | UNIT |

| Current lim     | iting                                                                                                          |                                                                  |        |       |       |        |       |       |      |

| I <sub>IN</sub> | Pin 11 Input current                                                                                           | Voltage at<br>Pin 11=250mV                                       |        | -2    | -20   |        | -2    | -20   | μΑ   |

|                 |                                                                                                                | 25°C                                                             |        |       |       |        |       |       |      |

|                 |                                                                                                                | Over temperature                                                 |        |       | -40   |        |       | -40   | μA   |

|                 | Single pulse inhibit delay                                                                                     | Inhibit delay time for 20%<br>overdrive at 40mA I <sub>OUT</sub> |        | 0.7   | 0.8   |        | 0.7   | 0.8   | μs   |

| OC2             | Trip Levels: Shut down, slow start, low level                                                                  |                                                                  | 0.500  | 0.600 | 0.700 | 0.500  | 0.600 | 0.700 | V    |

| OC1             | Current limit, high level                                                                                      |                                                                  | 0.400  | 0.480 | 0.560 | 0.400  | 0.560 | 0.500 | V    |

| ∆OC             | Low Level in terms of high level, $OC_2$                                                                       |                                                                  | 0.750  | 0.800 | 0.850 | 0.750  | 0.800 | 0.850 | V    |

| Error ampli     | fier                                                                                                           |                                                                  | •      |       | •     |        |       | • •   |      |

| V <sub>OH</sub> | Output voltage swing                                                                                           |                                                                  | 6.2    |       | 9.5   | 6.2    |       | 9.5   | V    |

| V <sub>OL</sub> | Output voltage swing                                                                                           |                                                                  |        |       | 0.7   |        |       | 0.7   | V    |

|                 | Open-loop gain                                                                                                 |                                                                  | 54     | 60    |       | 54     | 60    |       | dB   |

| R <sub>F</sub>  | Feedback resistor                                                                                              |                                                                  | 10k    |       |       | 10k    |       |       | Ω    |

| BW              | Small-signal bandwidth                                                                                         |                                                                  |        | 3     |       |        | 3     |       | MHz  |

| Output stag     | ge in the second se |                                                                  |        |       |       |        |       |       |      |

|                 | V <sub>CE</sub> (SAT) I <sub>C</sub> =40mA                                                                     |                                                                  |        |       | 0.5   |        |       | 0.5   | V    |

|                 | Output current (Pin 15)                                                                                        |                                                                  | 40     |       |       | 40     |       |       | mA   |

|                 | Max. emitter voltage (Pin 14)                                                                                  |                                                                  | 5      | 6     |       | 5      | 6     |       | V    |

| Supply volt     | age/current <sup>1</sup>                                                                                       |                                                                  |        |       |       |        |       |       |      |

| I <sub>CC</sub> | Supply current                                                                                                 | I <sub>Z</sub> =0, voltage-forced,                               |        |       |       |        |       |       |      |

|                 |                                                                                                                | V <sub>CC</sub> =12V, 25°C                                       |        |       | 10    |        |       | 10    | mA   |

|                 |                                                                                                                | Over temp.                                                       |        |       | 15    |        |       | 15    | mA   |

| V <sub>CC</sub> | Supply voltage                                                                                                 | I <sub>CC</sub> =10mA current-fed                                | 20     |       | 23    | 19     |       | 24    | V    |

| V <sub>CC</sub> | Supply voltage                                                                                                 | I <sub>CC</sub> =30mA current-fed                                | 20     |       | 30    | 20     |       | 30    | V    |

NOTES:

1. Does not include current for timing resistors or capacitors.

### NE/SE5560

|        | NE5560                      |                                   |  |  |  |  |  |

|--------|-----------------------------|-----------------------------------|--|--|--|--|--|

| Pin No | Function                    | Maximum Voltage                   |  |  |  |  |  |

| 1      | V <sub>CC</sub>             | See Note 1                        |  |  |  |  |  |

| 2      | VZ                          | Do not force (8.4V)               |  |  |  |  |  |

| 3      | Feedback                    | Vz                                |  |  |  |  |  |

| 4      | Gain                        |                                   |  |  |  |  |  |

| 5      | Modulator                   | Vz                                |  |  |  |  |  |

| 6      | Duty Cycle Control          | Vz                                |  |  |  |  |  |

| 7      | R <sub>T</sub>              | Current force mode                |  |  |  |  |  |

| 8      | CT                          |                                   |  |  |  |  |  |

| 9      | External Sync               | Vz                                |  |  |  |  |  |

| 10     | Remote On/Off               | Vz                                |  |  |  |  |  |

| 11     | Current Limiting            | V <sub>CC</sub>                   |  |  |  |  |  |

| 12     | GND                         | GND                               |  |  |  |  |  |

| 13     | Demagnetization/Overvoltage | V <sub>CC</sub>                   |  |  |  |  |  |

| 14     | Output (Emit)               | Vz                                |  |  |  |  |  |

| 15     | Output (Collector)          | V <sub>CC</sub> +2V <sub>BE</sub> |  |  |  |  |  |

| 16     | Feed-forward                | V <sub>CC</sub>                   |  |  |  |  |  |

#### **MAXIMUM PIN VOLTAGES**

NOTES:

1. When voltage-forced, maximum is 18V; when current-fed, maximum is 30mA. See voltage-/current-fed supply characteristic curve.

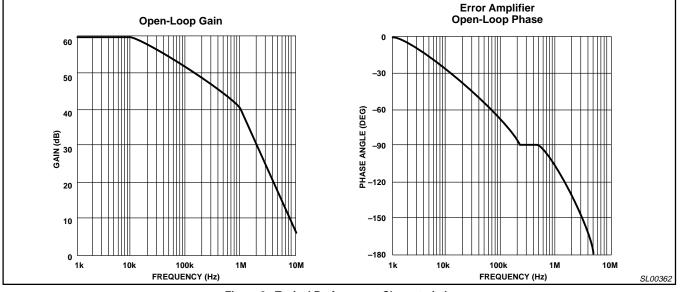

Figure 3. Typical Performance Characteristics

### NE/SE5560

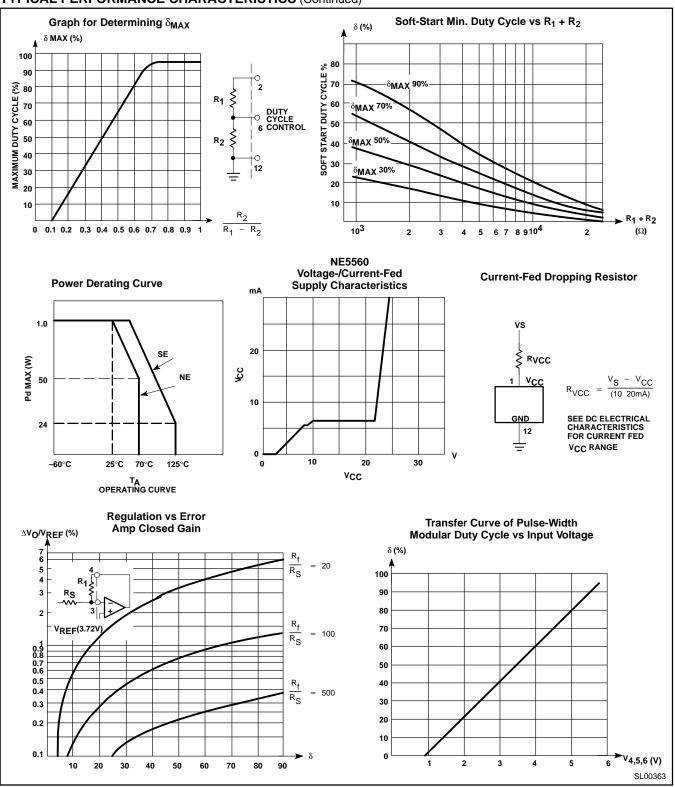

#### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

Figure 4. Typical Performance Characteristics

## NE/SE5560

#### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

Figure 5. Typical Performance Characteristics

#### THEORY OF OPERATION

- The following functions are incorporated:

- A temperature-compensated reference source.

- An error amplifier with Pin 3 as input. The output is connected to Pin 4 so that the gain is adjustable with external resistors.

- A sawtooth generator with a TTL-compatible synchronization input (Pins 7, 8, 9).

- A pulse-width modulator with a duty cycle range from 0 to 95%.

The PWM has two additional inputs:

Pin 6 can be used for a precise setting of  $\delta_{MAX}$

Pin 5 gives a direct access to the modulator, allowing for real constant-current operation:

- A gate at the output of the PWM provides a simple dynamic current limit.

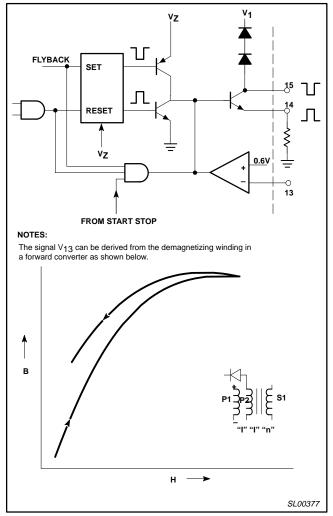

- A latch that is set by the flyback of the sawtooth and reset by the output pulse of the above mentioned gate prohibits double pulsing.

- Another latch functions as a start-stop circuit; it provides a fast switch-off and a slow start.

- A current protection circuit that operates via the start-stop circuit. This is a combined function with the current limit circuit, therefore Pin 11 has two trip-on levels; the lower one for cycle-by-cycle current limiting, the upper one for current protection by means of switch-off and slow-start.

- A TTL-compatible remote on/off input at Pin 10, also operating via the start-stop circuit.

- An inhibit input at Pin 13. The output pulse can be inhibited immediately.

- An output gate that is commanded by the latches and the inhibit circuit.

- An output transistor of which both the collector (Pin 15) and the emitter (Pin 14) are externally available. This allows for normal or inverse output pulses.

- A power supply that can be either voltage- or current-driven (Pins 1 and 12). The internally-generated stabilized output voltage VZ is connected to Pin 2.

- A special function is the so-called feed-forward at Pin 16. The amplitude of the sawtooth generator is modulated in such a way that the duty cycle becomes inversely proportional to the voltage on this pin:  $\delta \sim 1/V16$ .

- Loop fault protection circuits assure that the duty cycle is reduced to zero or a low value for open- or short-circuited feedback loops.

#### Stabilized Power Supply (Pins 1, 2, 12)

The power supply of the NE5560 is of the well known series regulation type and provides a stabilized output voltage of typically 8.5V.

This voltage  $V_Z$  is also present at Pin 2 and can be used for precise setting of  $\delta_{MAX}$  and to supply external circuitry. Its max. current capability is 5mA.

The circuit can be fed directly from a DC voltage source between 10.5V and 18V or can be current-driven via a limiting resistor. In the latter case, internal pinch-off resistors will limit the maximum supply voltage: typical 23V for 10mA and max. 30V for 30mA.

The low supply voltage protection is active when  $V_{(1-12)}$  is below 10.5V and inhibits the output pulse (no hysteresis).

When the supply voltage surpasses the 10.5V level, the IC starts delivering output pulses via the slow-start function.

### NE/SE5560

The current consumption at 12V is less than 10mA, provided that no current is drawn from  $V_Z$  and  $R_{(7-12)}{\geq}20k\Omega.$

#### The Sawtooth Generator

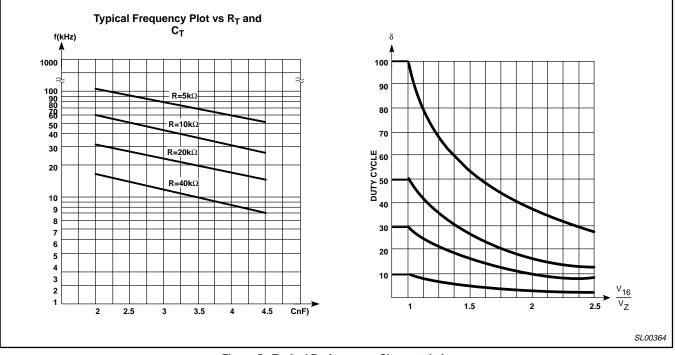

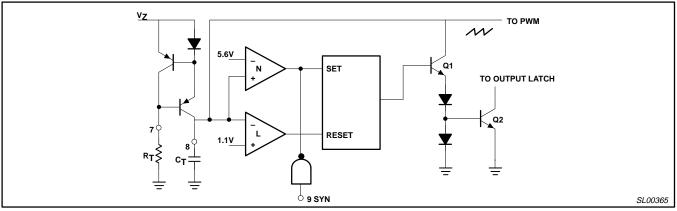

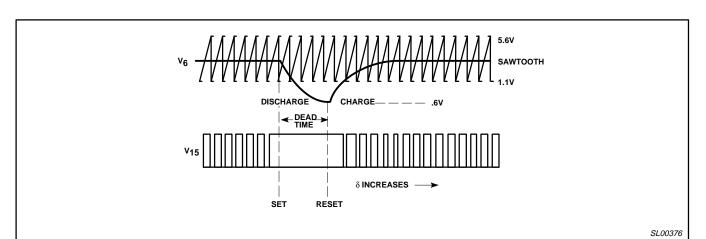

Figure 6 shows the principal circuitry of the oscillator. A resistor between Pin 7 and Pin 12 (GND) determines the constant current that charges the timing capacitor  $C_{(8-12)}$ .

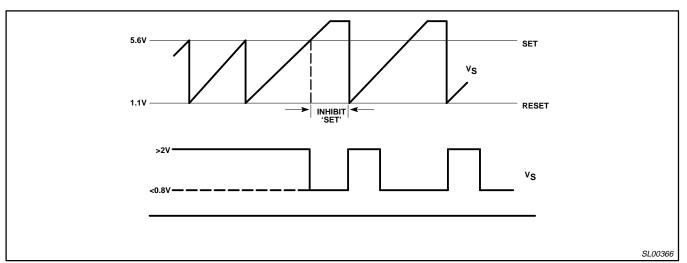

This causes a linear increasing voltage on Pin 8 until the upper level of 5.6V is reached. Comparator H sets the RS flip-flop and Q1 discharges  $C_{(8-12)}$  down to 1.1V, where comparator L resets the flip-flop. During this flyback time, Q2 inhibits the output.

Synchronization at a frequency lower than the free-running frequency is accomplished via the TTL gate on Pin 9. By activating this gate ( $V^9$ <2V), the setting of the sawtooth is prevented. This is indicated in Figure 7.

Figure 8 shows a typical plot of the oscillator frequency against the timing capacitor. The frequency range of the NE5560 goes from <50Hz up to >100kHz.

#### **Reference Voltage Source**

The internal reference voltage source is based on the bandgap voltage of silicon. Good design practice assures a temperature dependency typically ±100ppm/°C. The reference voltage is connected to the positive input of the error amplifier and has a typical value of 3.72V.

#### **Error Amplifier Compensation**

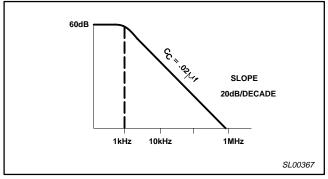

For closed-loop gains less than 40dB, it is necessary to add a simple compensation capacitor as shown in Figures 8 and 9.

#### **Error Amplifier with Loop-Fault Protection Circuits**

This operational amplifier is of a generally used concept and has an open-loop gain of typically 60dB. As can be seen in Figure 9, the inverting input is connected to Pin 3 for a feedback information proportional to  $V_O$ .

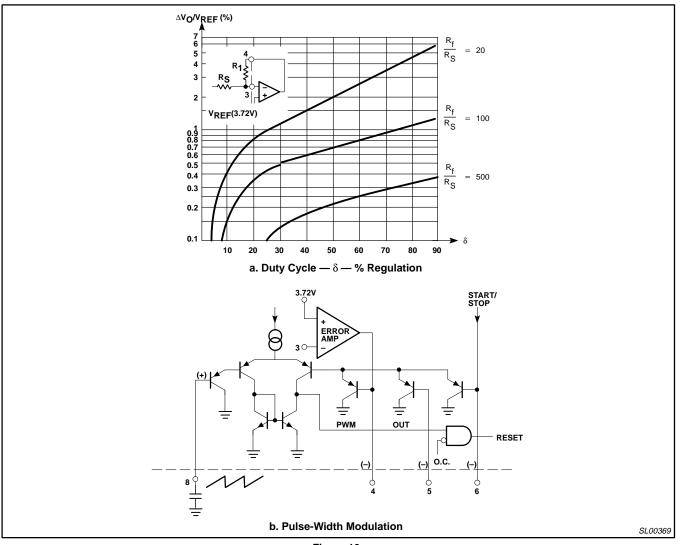

The output goes to the PWM circuit, but is also connected to Pin 4, so that the required gain can be set with R<sub>S</sub> and R<sub>(3-4)</sub>. This is indicated in Figure 9, showing the relative change of the feedback voltage as a function of the duty cycle. Additionally, Pin 4 can be used for phase shift networks that improve the loop stability.

When the SMPS feedback loop is interrupted, the error amplifier would settle in the middle of its active region because of the feedback via  $R_{(3-4)}$ . This would result in a large duty cycle. A current source on Pin 3 prevents this by pushing the input voltage high via

the voltage drop over R<sub>(3-4)</sub>. As a result, the duty cycle will become zero, provided that R<sub>(3-4)</sub>>100k. When the feedback loop is short-circuited, the duty cycle would jump to the adjusted maximum duty cycle. Therefore, an additional comparator is active for feedback voltages at Pin 3 below 0.6V. Now an internal resistor of typically 1k is shunted to the impedance on the  $\delta_{MAX}$  setting Pin 6. Depending on this impedance,  $\delta$  will be reduced to a value  $\delta_0$ . This will be discussed further.

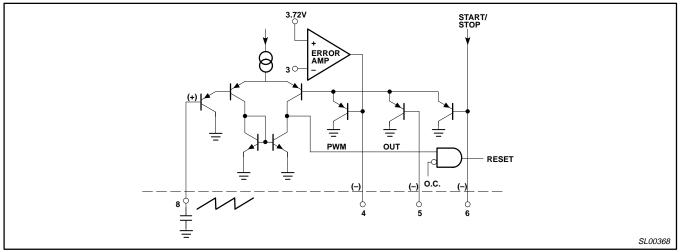

#### The Pulse-Width Modulator

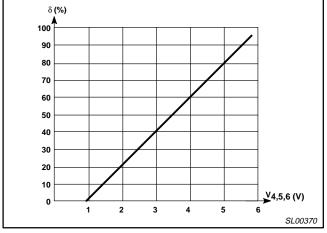

The function of the PWM circuit is to translate a feedback voltage into a periodical pulse of which the duty cycle depends on that feedback voltage. As can be seen in Figure 10, the PWM circuit in the NE5560 is a long-tailed pair in which the sawtooth on Pin 8 is compared with the LOWEST voltage on either Pin 4 (error amplifier), Pin 5, or Pin 6 ( $\delta_{MAX}$  and slow-start). The transfer graph is given in Figure 11. The output of the PWM causes the resetting of the output bi-stable.

#### Limitation of the Maximum Duty Cycle

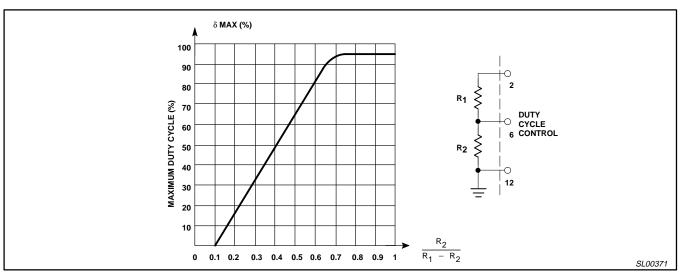

With Pins 5 and 6 not connected and with a rather low feedback voltage on Pin 3, the NE5560 will deliver output pulses with a duty cycle of  $\approx$  95%. In many SMPS applications, however, this high  $\delta$  will cause problems. Especially in forward converters, where the transformer will saturate when  $\delta$  exceeds 50%, a limitation of the maximum duty cycle is a must.

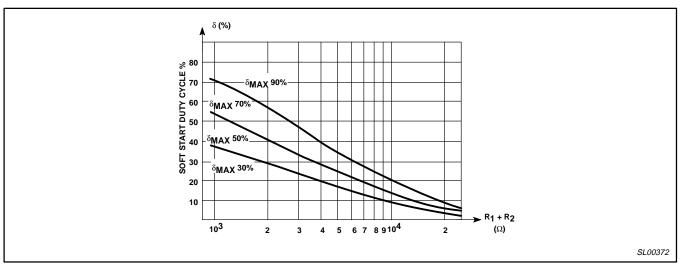

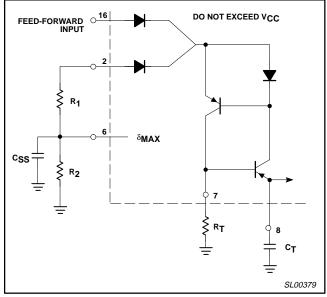

A DC voltage applied to Pin 6 (PWM input) will set  $\delta_{MAX}$  at a value in accordance with Figure 11. For low tolerances of  $\delta_{MAX}$ , this voltage on Pin 6 should be set with a resistor divider from V<sub>Z</sub> (Pin 2). The upper and lower sawtooth levels are also set by means of an internal resistor divider from V<sub>Z</sub>, so forming a bridge configuration with the  $\delta_{MAX}$  setting is low because tolerances in V<sub>Z</sub> are compensated and the sawtooth levels are determined by internal resistor matching rather than by absolute resistor tolerance. Figure 12 can be used for determining the tap on the bleeder for a certain  $\delta_{MAX}$  setting.

As already mentioned, Figure 13 gives a graphical representation of this. The value  $\delta o$  is limited to the lower and the higher side;

- It must be large enough to ensure that at maximum load and minimum input voltage the resulting feedback voltage on Pin 3 exceeds 0.6V.

- It must be small enough to limit the amount of energy in the SMPS when a loop fault occurs. In practice, a value of 10-15% will be a good compromise.

Figure 6. Sawtooth Generator

## NE/SE5560

Figure 7. Sawtooth Oscillator Synchronization

Figure 8. Error Amplifier Compensation Open-Loop Gain

Figure 9. Error Amplifier

### NE/SE5560

Figure 10.

Figure 11. Transfer Curve of Pulse-Width Modulator Duty Cycle vs Input Voltage

#### Extra PWM Input (Pin 5)

The PWM has an additional inverting input: Pin 5. It allows for attacking the duty cycle via the PWM circuit, independently from the feedback and the  $\delta_{MAX}$  information. This is necessary when the SMPS must have a real constant-current behavior, possibly with a fold-back characteristic. However, the realization of this feature must be done with additional external components. When not used, Pin 5 should be tied to Pin 6.

## NE/SE5560

Figure 12. Graph for Determining  $\delta_{\text{MAX}}$

Figure 13. Soft-Start Minimum Duty Cycle vs R<sub>1</sub> + R<sub>2</sub>

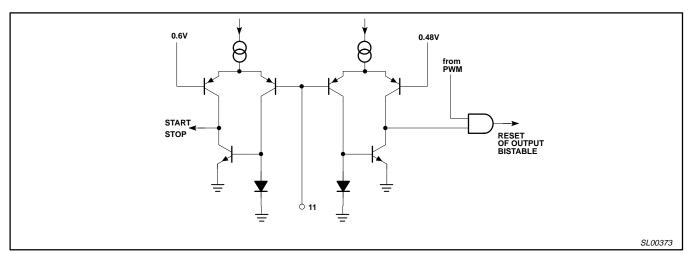

Figure 14. Current Protection Input

1994 Aug 31

## NE/SE5560

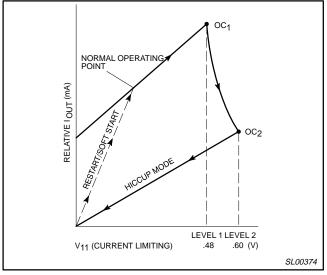

Figure 15. Output Characteristics

# Dynamic Current Limit and Current Protection (Pin 11)

In many applications, it is not necessary to have a real constant-current output of the SMPS.

Protection of the power transistor will be the prime goal. This can be realized with the NE5560 in an economical way. A resistor (or a current transformer) in the emitter of the power transistor gives a replica of the collector current. This signal must be connected to Pin 11. As can be seen in Figure 14, this input has two comparators with different reference levels. The output of the comparator with the lower 0.48V reference is connected to the same gate as the output of the PWM.

When activated, it will immediately reset the output flip-flop, so reducing the duty cycle. The effectiveness of this cycle-by-cycle

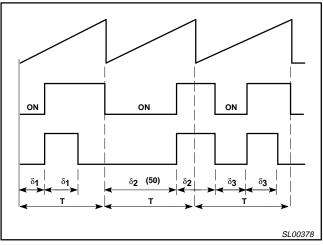

current limit diminishes at low duty cycle values. When  $\delta$  becomes very small, the storage time of the power transistor becomes dominant. The current will now increase again, until it surpasses the reference of the second comparator. The output of this comparator activates the start-stop circuit and causes an immediate inhibit of the output pulses. After a certain deadtime, the circuit starts again with very narrow output pulses. The effect of this two-level current protection circuit is visualized in Figure 15.

#### **The Start-Stop Circuit**

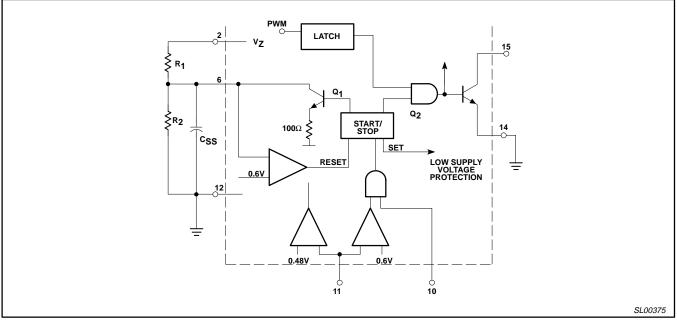

The function of this protection circuit is to stop the output pulses as soon as a fault occurs and to keep the output stopped for several periods. After this dead-time, the output starts with a very small, gradually increasing duty cycle. When the fault is persistent, this will cause a cyclic switch-off/switch-on condition. This "hiccup" mode effectively limits the energy during fault conditions. The realization and the working of the circuit are indicated in Figures 12 and 13. The dead time and the soft-start are determined by an external capacitor that is connected to Pin 6 ( $\delta_{MAX}$  setting).

An RS flip-flop can be set by three different functions:

- 1. Remote on/off on Pin 10.

- 2. Overcurrent protection on Pin 11.

- 3. Low supply voltage protection (internal).

As soon as one of these functions cause a setting of the flip-flop, the output pulses are blocked via the output gate. In the same time transistor Q1 is forward-biased, resulting in a discharge of the capacitor on Pin 6.

The discharging current is limited by an internal 150 $\Omega$  resistor in the emitter of Q1. The voltage at Pin 6 decreases to below the lower level of the sawtooth. When V6 has dropped to 0.6V, this will activate a comparator and the flip-flop is reset. The output stage is no longer blocked and Q1 is cut off. Now V<sub>Z</sub> will charge the capacitor via R1 to the normal  $\delta_{MAX}$  voltage. The output starts delivering very narrow pulses as soon as V6 exceeds the lower sawtooth level. The duty cycle of the output pulse now gradually increases to a value determined by the feedback on Pin 3, or by the static  $\delta_{MAX}$  setting on Pin 6.

Figure 16. Start-Stop Circuit

Figure 17. Start-Stop Circuit

#### Remote On/Off Circuit (Pin 10)

In systems where two or more power supplies are used, it is often necessary to switch these supplies on and off in a sequential way. Furthermore, there are many applications in which a supply must be switched by a logical signal. This can be done via the TTL-compatible remote on/off input on Pin 10. The output pulse is inhibited for levels below 0.8V. The output of the IC is no longer blocked when the remote on/off input is left floating or when a voltage >2V is applied. Start-up occurs via the slow-start circuit.

#### The Output Stage

The output stage of the NE5560 contains a flip-flop, a push-pull driven output transistor, and a gate, as indicated in Figure 18. The flip-flop is set by the flyback of the sawtooth. Resetting occurs by a signal either from the PWM or the current limit circuit. With this configuration, it is assured that the output is switched only once per period, thus prohibiting double pulsing. The collector and emitter of the output transistor are connected to respectively Pin 15 and Pin 14, allowing for normal or inverted output pulses. An internally-grounded emitter would cause intolerable voltage spikes over the bonding wire, especially at high output currents.

This current capability of the output transistor is 40mA peak for V<sub>CE</sub>  $\cong$  0.4V. An internal clamping diode to the supply voltage protects the collector against overvoltages. The max. voltage at the emitter (Pin 14) must not exceed +5V. A gate, activated by one of the set or reset pulses, or by a command from the start-stop circuit will immediately switch-off the output transistor by short-circuiting its base. The external inhibitor (Pin 13) operates also via this base.

#### **Demagnetization Sense**

As indicated in Figure 18, the output of this NPN comparator will block the output pulse, when a voltage above 0.6V is applied to Pin 13. A specific application for this function is to prevent saturation of forward-converter transformers. This is indicated in Figure 19.

#### Feed-Forward (Pin 16)

The basic formula for a forward converter is

$$V_{OUT} = \frac{dV_{IN}}{n}$$

(n = transformer ratio)

This means that in order to keep  $V_{OUT}$  at a constant value, the duty cycle  $\delta$  must be made inversely proportional to the input voltage. A pre-regulation (feed-forward) with the function  $\delta{\sim}1/V_{IN}$  can ease the feedback-loop design.

Figure 18. Output Stage

This loop now only has to regulate for load variations which require only a low feedback gain in the normal operation area. The transformer of a forward converter must be designed in such a way

NE/SE5560

## NE/SE5560

that it does not saturate, even under transient conditions, where the max. inductance is determined by  $\delta_{MAX} \times V_{IN}$  max. A regulation of  $\delta_{MAX} \sim 1/V_{IN}$  will allow for a considerable reduction or simplification of the transformer. The function of  $\delta \sim 1/V_{IN}$  can be realized by using Pin 16 of the NE5560.

Figure 19. Output Stage Inhibit

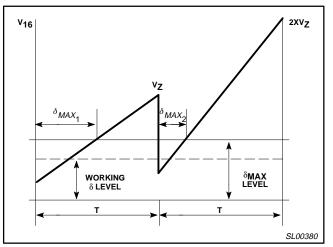

Figure 20 shows the electrical realization. When the voltage at Pin 16 exceeds the stabilized voltage  $V_Z$  (Pin 2), it will increase the charging current for the timing capacitor on Pin 8.

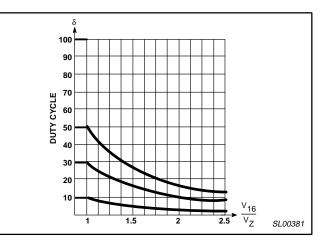

The operating frequency is not affected, because the upper trip level for sawtooth increases also. Note that the  $\delta_{MAX}$  voltage on Pin 6 remains constant because it is set via V<sub>Z</sub>. Figure 21 visualizes the effect on  $\delta_{MAX}$  and the normal operating duty cycle  $\delta$ . For V<sub>16</sub>=2×V<sub>Z</sub>, these duty cycles have halved. The graph for  $\delta$ =f(V<sub>16</sub>) is given in Figure 22.

#### NOTE:

V<sub>16</sub> must be less than Pin 1 voltage.

#### APPLICATIONS

#### NE/SE5560 Push-Pull Regulator

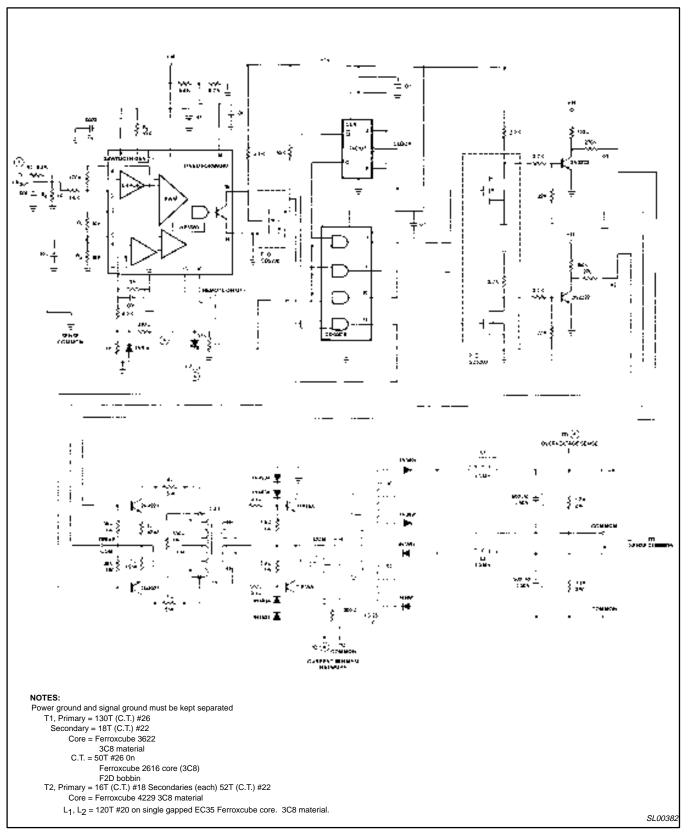

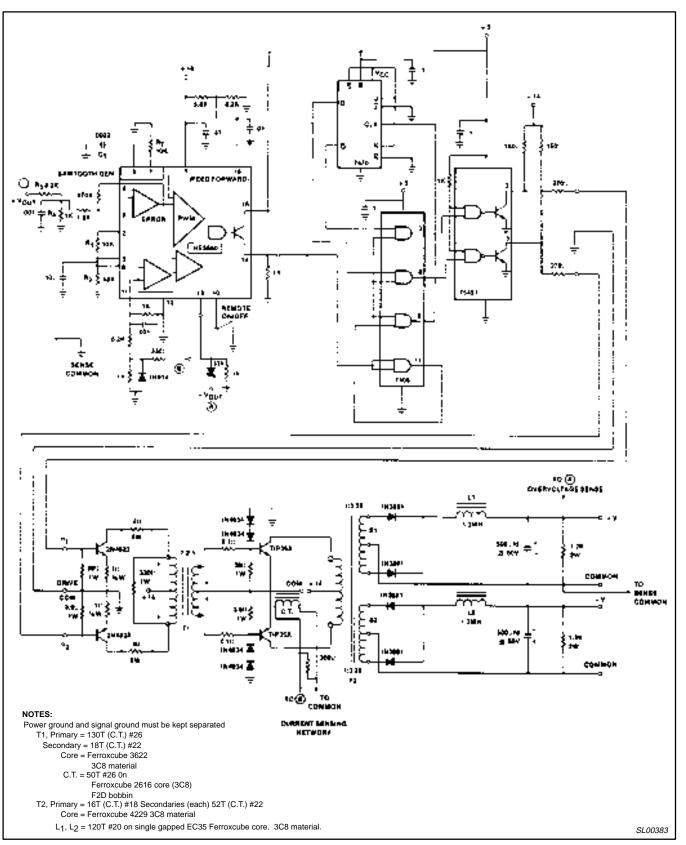

This application describes the use of the Philips Semiconductors NE/SE5560 adapted to function as a push-pull switched mode regulator, as shown in Figures 23 and 24.

Input voltage range is +12V to +18V for a nominal output of +30V and -30V at a maximum load current of 1A with an average efficiency of 81%.

Features include feed-forward input compensation, cycle-to-cycle drive current protection and other voltage sensing, line (to positive output) regulation <1% for an input range of +13V to +18V and load regulation to positive output of <3% for  $\Delta I_L(+)$  of 0.1 to 1A.

The main pulse-width modulator operates to 48kHz with power switching at 24kHz.

Figure 20. External  $\delta$  Maximum Control

Figure 21. Feed-Forward Circuitry

Figure 22. Feed-Forward Regulation

# NE/SE5560

Product specification

Figure 23. NE/SE5560 Push-Pull Switched-Mode Regulated Supply with CMOS Drive Conversion Logic

#### Product specification

## NE/SE5560

Figure 24. NE/SE5560 Push-Pull Switched-Mode Regulated With TTL Drive Conversion Logic