# **Protection Interface Circuit** for PMICs with Integrated OVP Control

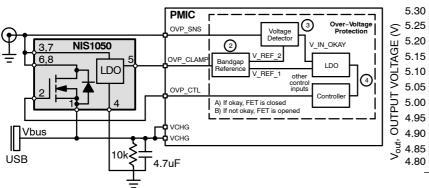

The NIS1050 is a protection IC targeted at the latest generation of PMICs from the leading mobile phone and UMPC chipset vendors. It includes a highly stable low-current LDO and a low impedance power N-Channel MOSFET.

The LDO provides a low current, five volt supply to the PMIC, and the NFET is the external pass element for the OVIC circuit. These stages combine with the internal PMIC to protect the charging circuit from low-impedance overvoltage conditions that can occur from either the AC/DC or USB supply.

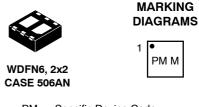

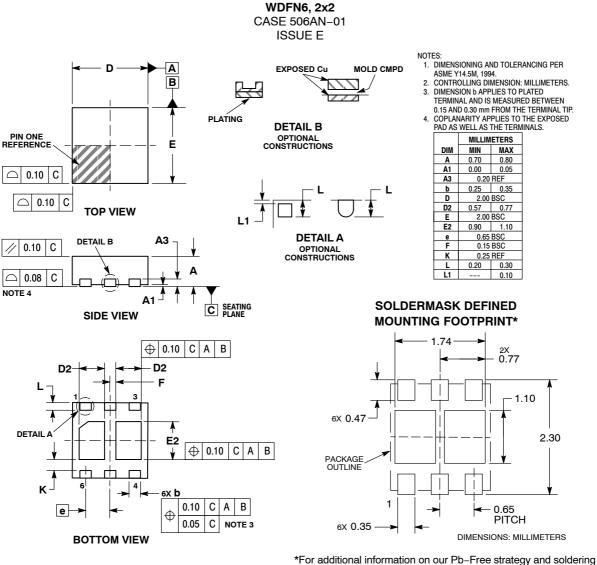

The NIS1050 is available in the low–profile 6-lead 2x2mm WDFN6 surface mount package.

### Features

- Lower Power Dissipation and Higher Efficiency vs. Zener Shunt Regulator

- LDO Highly Stable across Temperature, Operates Without Bypass Capacitors

- Wide 3-30 V Power Supply Voltage Input Range

- Low–Profile (0.75mm) 6-Lead 2x2mm WDFN6 Package

- This is a Pb–Free Device

### **Typical Applications**

• Power Interface for New Generation PMICs from Leading Mobile Phone and UMPC Chipset Vendors

# **ON Semiconductor®**

http://onsemi.com

PM = Specific Device Code M = Date Code

### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NIS1050MNTBG | WDFN6<br>(Pb-Free) | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

Figure 1. Typical Application

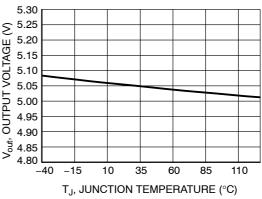

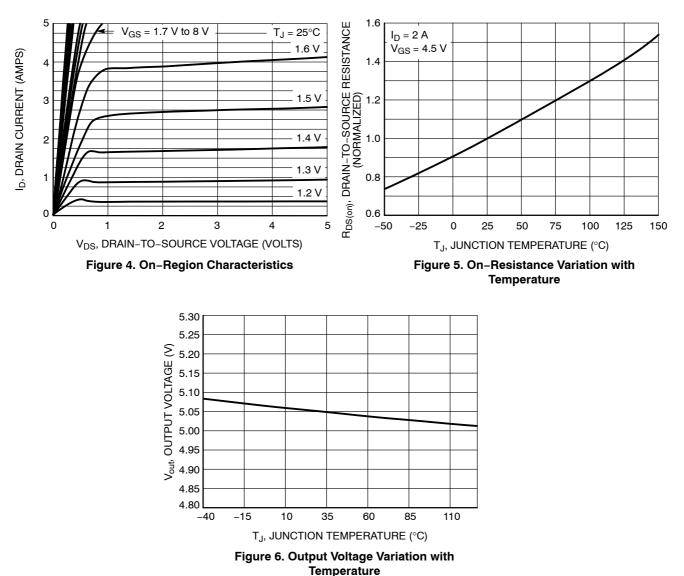

Figure 2. Output Voltage Variation with Temperature

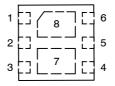

### Figure 3. Pin Assignment

### Table 1. FUNCTIONAL PIN DESCRIPTION

| Pin  | Function | Description                                                                                                                                           |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Source   | This is the source of the power FET and connects to the PMIC pin of the same name.                                                                    |

| 2    | Gate     | This pin is the gate of the FET switch.                                                                                                               |

| 3, 7 | Vin      | Positive input voltage to the device.                                                                                                                 |

| 4    | Ground   | Negative input voltage to the device. This is used as the internal reference for the IC.                                                              |

| 5    | Vout     | This is the output of the internal LDO. It passes the input voltage through to the output and clamps that voltage if it exceeds the regulation limit. |

| 6, 8 | Drain    | Positive input voltage to the device.                                                                                                                 |

### **Table 2. MAXIMUM RATINGS**

| Rating                                                                                         | Symbol           | Value      | Unit |

|------------------------------------------------------------------------------------------------|------------------|------------|------|

| Input Voltage, Operating, Steady-State (OVP_sense to Gnd)                                      | V <sub>in</sub>  | -0.3 to 30 | V    |

| Gate-to-Source Voltage                                                                         | V <sub>GS</sub>  | ±8         | V    |

| Drain Current, Peak (10 μs pulse)                                                              | I <sub>Dpk</sub> | 20         | A    |

| Drain Current, Continuous (Note 1, Steady-State)<br>$T_A = 25^{\circ}C$<br>$T_A = 85^{\circ}C$ | ۱ <sub>D</sub>   | 3.7<br>2.7 | A    |

| Total Power Dissipation @ T <sub>A</sub> = 25°C (Note 1, 2)                                    | P <sub>max</sub> | 750        | mW   |

| Operating Temperature Range                                                                    | ТJ               | -40 to 125 | °C   |

| Non-operating Temperature Range                                                                | TJ               | -55 to 150 | °C   |

| Maximum Lead Temperature for Soldering Purposes                                                | TL               | 260        | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Surface Mounted on FR4 Board using the minimum recommended pad size of 30 mm<sup>2</sup>, 2 oz Cu.

2. Dual die operation (equally-heated).

### **Table 3. THERMAL RESISTANCE RATINGS**

| Parameter                                           | Symbol              | Max | Unit |

|-----------------------------------------------------|---------------------|-----|------|

| SINGLE DIE OPERATION (SELF-HEATED)                  |                     |     |      |

| Junction-to-Ambient - Steady State (Note 3)         | R <sub>θJA</sub>    | 83  | °C/W |

| Junction-to-Ambient – Steady State Min Pad (Note 4) | R <sub>θJA</sub>    | 177 |      |

| Junction-to-Ambient – t $\leq$ 5 s (Note 3)         | R <sub>θJA</sub>    | 54  |      |

| DUAL DIE OPERATION (EQUALLY-HEATED)                 | · · · ·             |     |      |

| Junction-to-Ambient – Steady State (Note 3)         | R <sub>θJA</sub>    | 58  | °C/W |

| Junction-to-Ambient – Steady State Min Pad (Note 4) | R <sub>θJA</sub>    | 133 |      |

| Junction-to-Ambient – t $\leq$ 5 s (Note 3)         | $R_{	ext{	heta}JA}$ | 40  |      |

Surface Mounted on FR4 Board using 1 in sq pad size (Cu area = 1.127 in sq [2 oz] including traces).

Surface Mounted on FR4 Board using the minimum recommended pad size (30 mm<sup>2</sup>, 2 oz Cu).

| Characteristics                                                                                                                                           | Symbol                              | Min | Тур      | Max        | Unit    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----|----------|------------|---------|

| POWER FET                                                                                                                                                 |                                     | •   |          |            |         |

| Zero Gate Voltage Drain Current (V_{DS} = 24 V_{dc}, V_{GS} = 0 V) T_J = 85^{\circ}C                                                                      | I <sub>DSS</sub>                    |     |          | 1.0<br>10  | μΑ      |

| Gate-to-Source Leakage Current (V_{DS} = 0 V, V_{GS} = $\pm 8$ V)                                                                                         | I <sub>GSS</sub>                    |     |          | 100        | nA      |

| Gate Threshold Voltage (V_{GS} = V_{DS}, I_D = 250 \mu\text{A})                                                                                           | V <sub>GS(th)</sub>                 | 0.4 | 0.7      | 1.0        | V       |

| Negative Gate Threshold Temperature Coefficent                                                                                                            | V <sub>GS(th)</sub> /T <sub>J</sub> |     | 2.8      |            | mV/°C   |

| Drain-to-Source On-Resistance (Note 5)<br>$V_{GS}$ = 4.5 V, I <sub>D</sub> = 2.0 A<br>$V_{GS}$ = 2.5 V, I <sub>D</sub> = 2.0 A                            | R <sub>DS(on)</sub>                 |     | 47<br>56 | 70<br>90   | mΩ      |

| Forward Transconductance ( $V_{DS}$ = 5 V, $I_D$ = 2.0 A)                                                                                                 | 9 <sub>FS</sub>                     |     | 4.5      |            | S       |

| Input Capacitance ( $V_{DS}$ = 15 $V_{dc}$ , $V_{GS}$ = 0 $V_{dc}$ , f = 1 MHz)                                                                           | C <sub>ISS</sub>                    |     | 427      |            | pF      |

| Output Capacitance ( $V_{DS}$ = 15 $V_{dc}$ , $V_{GS}$ = 0 $V_{dc}$ , f = 1 MHz)                                                                          | C <sub>OSS</sub>                    |     | 51       |            | pF      |

| Reverse Transfer Capacitance (V <sub>DS</sub> = 15 V <sub>dc</sub> , V <sub>GS</sub> = 0 V <sub>dc</sub> , f = 1 MHz)                                     | C <sub>RSS</sub>                    |     | 32       |            | pF      |

| <b>LDO</b> (Unless otherwise noted, $T_J = 25^{\circ}C$ , Vin = 5.0 V)                                                                                    | ·                                   |     |          |            |         |

| Regulated Output Voltage (Vcc = 5.5 V lo = 1 mA)                                                                                                          | Vout                                | 4.6 | 5.0      | 5.3        | V       |

| Response to Input Transient (Vin 0 to 30 volts, <1 $\mu s$ rise time, 5.0 k $\Omega$ resistive load, Note 6) Time for signal above 5.5 volts Peak Voltage | t <sub>pulse</sub><br>Vpk           |     |          | 5.0<br>9.0 | μs<br>V |

| Headroom (Vin – Vout, lout = 1.2 mA, Vin = 4.6 V)                                                                                                         | V <sub>head</sub>                   |     |          | 150        | mV      |

| Headroom (Vin – Vout, lout = 10 mA, Vin = 4.8 V, $T_J$ = -40 to 125°C)                                                                                    | V <sub>head</sub>                   |     |          | 1000       | mV      |

| TOTAL DEVICE                                                                                                                                              |                                     |     |          |            |         |

| Input Bias Current                                                                                                                                        | I <sub>bias</sub>                   |     | 110      | 850        | μA      |

| Minimum Operating Voltage                                                                                                                                 | V <sub>in-min</sub>                 |     |          | 3.0        | V       |

Table 4. ELECTRICAL CHARACTERISTICS (Unless otherwise noted: Vcc (OVP sense) = 5.0 V, T<sub>1</sub> = 25°C)

5. Pulse test: Pulse width 300 μs, duty cycle 2%.

6. Guaranteed by design.

### **Mounting Considerations**

The LDO and MOSFET are both attached to thermal pads to provide a low impedance path for the heat generated in these devices. Both of these pads should have a solid connection to as much board copper area as possible in order to maintain a low operating temperature. The main purpose of both of these pads is for thermal connections, not electrical connections.

Pad 7 is the input voltage for the LDO. It is electrically connected to the Vcc pin. This connection is optional and will have a negligible difference in the electrical performance of the chip due to the current into the LDO.

Pad 8 is the drain of the power MOSFET. This pad will also have a low electrical impedance. Either pad 8, pad 6 or both may be used for electrical connections. The total impedance of the FET will not vary significantly since pad 6 is part of the lead-frame and therefore connected to pad 8 by a metal path on the lead frame. The majority of the package impedance comes from the resistance between the source and pin 1, since this is connected by bond wires.

### **Bypass Capacitors**

The LDO has been designed to operate in a stable mode without bypass capacitors; however, it is recommended to use a low ESR capacitor if fast, ac transients or other switching type currents will be present. Typically, a value of 1 to 10 nF is adequate for an output bypass capacitor. A 1 nF capacitor may be added to the input if the input source is noisy or if it has a high ac impedance due to long trace lengths.

### PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agsociated with such unintended or unauthorized use patent solut. Cwas negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit//Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

#### Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850

#### ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative