# PRELIMINARY

# **3V Operation Switching Driver for Class D Amplifier**

#### GENERAL DESCRIPTION

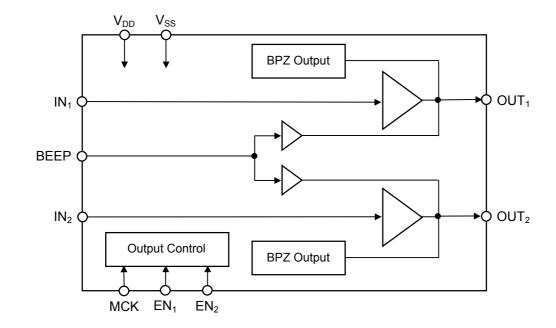

The **NJU8711** is a Switching Driver for class D Amplifier containing BEEP and BPZ (Bipolar Zero) output circuits, It converts 1bit digital signal input, such as PWM or PDM signal, to analog signal output with simple external LC low-pass filter.

The **NJU8711** realizes very high power-efficiency by class D operation. Therefore, It is suitable for portable audio set and others.

NJU8711V

#### ■ FEATURES

- 2 channel 1bit Audio Signal Input

- Standby(Hi-Z), BPZ Control

- Internal BPZ Charger

- Beep Function

- Operating Voltage : 2.7V to 3.6V

- CMOS Technology

BLOCK DIAGRAM

Package Outline : SSOP10

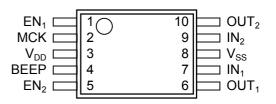

#### ■ PIN CONFIGURATION

# TERMINAL DESCRIPTION

| No.     | SYMBOL                               | I/O | Function                                                                                                                                                                                                                                                                                                                                                                      |

|---------|--------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3       | V <sub>DD</sub>                      | -   | Power Supply, V <sub>DD</sub> =3V                                                                                                                                                                                                                                                                                                                                             |

| 8       | V <sub>SS</sub>                      | -   | Power GND, V <sub>SS</sub> =0V                                                                                                                                                                                                                                                                                                                                                |

| 2       | МСК                                  | I   | Master Clock Input Terminal<br>The condition of the data input terminal is fetched with the rising<br>edge of this signal.                                                                                                                                                                                                                                                    |

| 1       | EN <sub>1</sub>                      | 1   | Output Control Terminal                                                                                                                                                                                                                                                                                                                                                       |

| 5       | $EN_2$                               | 1   | Output circuit is selected by the condition of this terminal.                                                                                                                                                                                                                                                                                                                 |

| 7       | IN <sub>1</sub>                      |     | Audio Signal Input Terminal                                                                                                                                                                                                                                                                                                                                                   |

| 9       | IN <sub>2</sub>                      | 1   | 1-bit Audio Signal inputs this terminal.                                                                                                                                                                                                                                                                                                                                      |

| 4       | BEEP                                 | Ι   | Beep Signal Input Terminal<br>Beep signal inputs this terminal.                                                                                                                                                                                                                                                                                                               |

| 6<br>10 | OUT <sub>1</sub><br>OUT <sub>2</sub> | 0   | <ul> <li>Output Terminal</li> <li>When Output Terminal selects Audio Signal, IN<sub>1</sub> terminal input data output to OUT<sub>1</sub> terminal and IN<sub>2</sub> terminal input data output to OUT<sub>2</sub> terminal.</li> <li>When Output Terminal selects Beep Signal, BEEP terminal input data output to OUT<sub>1</sub> and OUT<sub>2</sub> terminals.</li> </ul> |

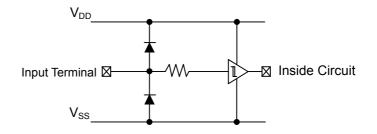

# ■ INPUT TERMINAL STRUCTURE

#### FUNCTIONAL DESCRIPTION

(1) Signal Output

PWM signal for L-ch. and R-ch. output from  $OUT_1$  and  $OUT_2$  terminals respectively. These signals are converted to analog signal by external 2nd-order or over LC filter. The output driver power supplied from  $V_{DD}$  and  $V_{SS}$  are required high response power supply against voltage fluctuation like as switching regulator because Output THD is effected by power supply stability.

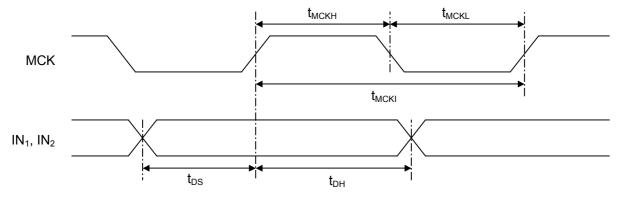

(2) Master Clock

Master clock (MCK) is synchronized the Audio signal input ( $IN_1$ ,  $IN_2$ ). The setup time and the hold time should be keep the AC characteristics because  $IN_1$  and  $IN_2$  are fetched with the rising edge of MCK. MCK requires small jitter as possible because Jitter down S/N ratio.

And,  $OUT_1$  and  $OUT_2$  occur the pop noise when MCK is stopped in operation without standby mode.

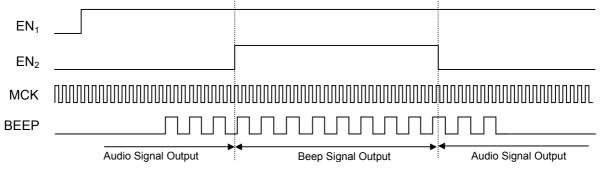

#### (3) Output Control

Output circuit is selected by the condition of  $EN_1$  and  $EN_2$  terminals.

| EN <sub>2</sub> | EN <sub>1</sub> | Output State of OUT <sub>1</sub> & OUT <sub>2</sub> |

|-----------------|-----------------|-----------------------------------------------------|

| 0               | 0               | Standby(High impedance)                             |

| 0               | 1               | Audio Signal Output                                 |

| 1               | 0               | BPZ Output                                          |

| 1               | 1               | Beep Signal Output                                  |

#### (4) Beep Function

The beep signal must be input before the rising edge of EN<sub>2</sub> signal and must be stopped after the falling edge of EN<sub>2</sub> signal.

# ■ ABSOLUTE MAXIMUM RATINGS

| _                   |                                     |                | (~                           | Га=25°С) |  |

|---------------------|-------------------------------------|----------------|------------------------------|----------|--|

| PARAMET             | ER                                  | SYMBOL         | RATING                       | UNIT     |  |

| Supply Voltage      | Supply Voltage V <sub>DD</sub> -0.3 |                | -0.3 to +4.0                 | V        |  |

| Input Voltage       |                                     | Vin            | -0.3 to V <sub>DD</sub> +0.3 | V        |  |

| Operating Temperate | Operating Temperature               |                | -40 to +85                   | °C       |  |

| Storage Temperature |                                     | Tstg           | -40 to +125                  | °C       |  |

| Power Dissipation   | SSOP10                              | P <sub>D</sub> | 280                          | mW       |  |

Note 1) All voltage values are specified as  $V_{SS}$ =0V.

Note 2) If the LSI is used on condition beyond the absolute maximum rating, the LSI may be destroyed. Using LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the electrical characteristics conditions will cause malfunction and poor reliability.

Note 3) Decoupling capacitors should be connected between  $V_{DD}$ - $V_{SS}$  due to the stabilized operation.

## ELECTRICAL CHARACTERISTICS

| (Ta=25°C, V <sub>DD</sub> =3.0V, V <sub>SS</sub> =0.0V, Load Impedance=16 $\Omega$ , f <sub>S</sub> =44.1kHz, unless otherwise noted) |                  |                                                                                                   |                        |                    |                        |      |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------|------------------------|--------------------|------------------------|------|

| PARAMETER                                                                                                                             | SYMBOL           | CONDITIONS                                                                                        | MIN.                   | TYP.               | MAX.                   | UNIT |

| $V_{DD}$ Supply Voltage                                                                                                               | $V_{DD}$         |                                                                                                   | 2.7                    | 3.0                | 3.6                    | V    |

| BPZ Driving Voltage                                                                                                                   | $V_{\text{BPZ}}$ |                                                                                                   | V <sub>DD</sub> /2-0.2 | V <sub>DD</sub> /2 | V <sub>DD</sub> /2+0.2 | V    |

| Output Driver<br>High side Resistance                                                                                                 | R <sub>H</sub>   | V <sub>OUT</sub> =V <sub>DD</sub> -0.1V                                                           | -                      | 1.5                | 2                      | Ω    |

| Output Driver<br>Low side Resistance                                                                                                  | RL               | V <sub>OUT</sub> =0.1V                                                                            | -                      | 1.5                | 2                      | Ω    |

| Beep<br>High side Current                                                                                                             | I <sub>BH</sub>  | V <sub>OUT</sub> =V <sub>DD</sub> -1V                                                             | 100                    | 250                | 600                    | uA   |

| Beep<br>Low side Current                                                                                                              | I <sub>BL</sub>  | V <sub>OUT</sub> =1V                                                                              | 100                    | 250                | 600                    | uA   |

| Power Supply Current<br>At Standby                                                                                                    | I <sub>ST</sub>  | Stopping MCK, $IN_1$ , $IN_2$ , BEEP                                                              | -                      | -                  | 1                      | uA   |

| Power Supply Current<br>At Operating                                                                                                  | I <sub>DD</sub>  | No-load operating<br>IN <sub>1</sub> , IN <sub>2</sub> =32f <sub>S</sub><br>MCK=256f <sub>S</sub> | -                      | 1                  | 2                      | mA   |

| Input Voltage                                                                                                                         | V <sub>IH</sub>  |                                                                                                   | 0.7V <sub>DD</sub>     | -                  | V <sub>DD</sub>        | V    |

|                                                                                                                                       | V <sub>IL</sub>  |                                                                                                   | 0                      | -                  | 0.3V <sub>DD</sub>     | V    |

| Input Leakage Current                                                                                                                 | I <sub>LK</sub>  |                                                                                                   | -                      | -                  | ±1                     | uA   |

# TIMING CHARACTERISTICS

Audio Signal Input

(Ta=25°C, V<sub>DD</sub>=3.0V, V<sub>SS</sub>=0.0V, unless otherwise noted)

| PARAMETER                                   | SYMBOL            | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------------|-------------------|------------|------|------|------|------|

| MCK Frequency                               | f <sub>мскі</sub> |            | 8    | -    | 25   | MHz  |

| MCK Pulse Width (H)                         | t <sub>мскн</sub> |            | 12   | -    | -    | ns   |

| MCK Pulse Width (L)                         | t <sub>MCKL</sub> |            | 12   | -    | -    | ns   |

| IN <sub>1</sub> ,IN <sub>2</sub> Setup Time | t <sub>DS</sub>   |            | 20   | -    | -    | ns   |

| IN <sub>1</sub> ,IN <sub>2</sub> Hold Time  | t <sub>DH</sub>   |            | 20   | -    | -    | ns   |

Note 4) t<sub>MCKI</sub> shows the cycle of the MCK signal.

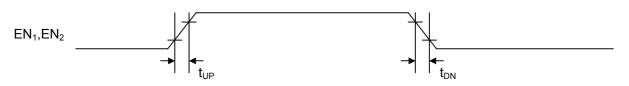

Output Control Signal Input

(Ta=25°C, V<sub>DD</sub>=3.0V, V<sub>SS</sub>=0.0V, unless otherwise noted)

| PARAMETER | SYMBOL          | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|-----------|-----------------|------------|------|------|------|------|

| Rise Time | t <sub>UP</sub> |            | -    | -    | 100  | ns   |

| Fall Time | t <sub>DN</sub> |            | -    | -    | 100  | ns   |

Note 5) All timings are based on 30% and 70% voltage level of  $V_{\mbox{\tiny DD}}.$

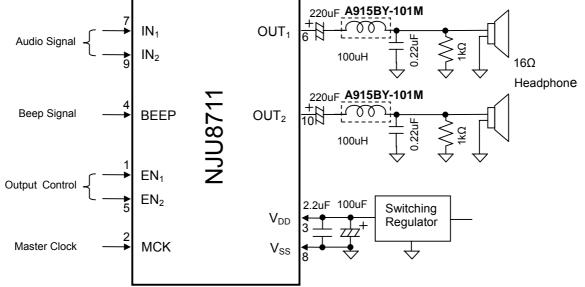

APPLICATION CIRCUIT

Stereo OTL configuration

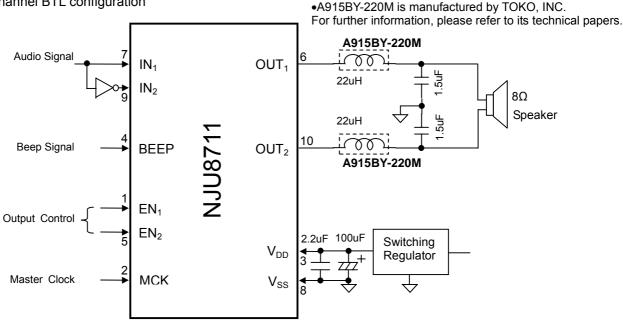

•A915BY-220M is manufactured by TOKO, INC. For further information, please refer to its technical papers.

• 1 channel BTL configuration

- Note 6) De-coupling capacitors must be connected between each power supply pin and GND pin.

- Note 7) The power supply for V<sub>DD</sub> require fast driving response performance such as a switching regulator for THD.

- Note 8) The bigger capacitor value of AC-coupling capacitors for headphone outputs realize better frequency response characteristics, especially low frequency area.

- Note 9) The above circuit shows only application example and dose not guarantee the any electrical characteristics. Therefore, please consider and check the circuit carefully to fit your application.

New Japan Radio Co., Ltd.

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

New Japan Radio Co.,Ltd.