# **1-Bit Gate Pulse Modulator**

The NLHV001 is a 1-bit gate pulse modulator designed to translate logic voltages for TFT LCD panels. This part translates a low voltage logic input signal to an output voltage of 15 V to 38 V. In addition, the NLV001 provides a user selectable delay and fall time on the high-to-low edge of the output signal. The delay and fall times are controlled by the magnitudes of the external and capacitor resistor, respectively.

#### Features

- Gate Pulse Modulation (GPM)

- TFT LCD Flicker Compensation Circuit

- Reduction of Coupling Effect Between Gate Line and Pixel

- Provides Power Sequencing Circuit for Gate Driver IC

- Wide Power Supply Operation: 15 V to 38 V

- Adjustable Output Delay and Fall Time

- This is a Pb–Free Device

#### **Typical Applications**

• TFT LCDs

#### Important Information

• ESD Protection for All Pins: Human Body Model (HBM) > 3000 V

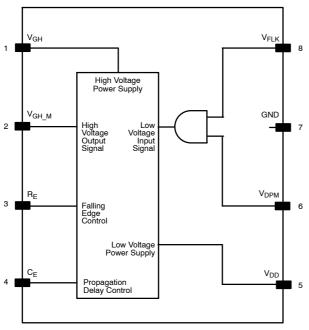

Figure 1. Block Diagram

# **ON Semiconductor®**

http://onsemi.com

(Note: Microdot may be in either location)

\*Date Code orientation may vary depending upon manufacturing location.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 10 of this data sheet.

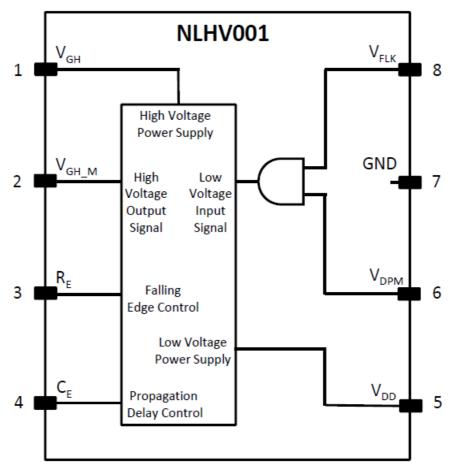

### **PIN DESCRIPTION**

| Pin | Pin Name          | Pin Function                                                                  | Comment                                                                                                                                                                                                                                                                                                      |

|-----|-------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>GH</sub>   | Power Supply Input                                                            | V <sub>GH</sub> = 15 to 38 V                                                                                                                                                                                                                                                                                 |

| 2   | V <sub>GH_M</sub> | Output                                                                        | This output directly drives the power supply of Gate Driver IC                                                                                                                                                                                                                                               |

| 3   | R <sub>E</sub>    | $R_{E}$ pin used to set the falling edge time $(t_{fall})$                    | The Delay time is programmed by connecting resistor $\rm R_{E}$ to $\rm V_{GH}$ and capacitor $\rm C_{E}$ to ground.                                                                                                                                                                                         |

| 4   | C <sub>E</sub>    | C <sub>E</sub> pin used to set the propagation delay time (t <sub>phl</sub> ) |                                                                                                                                                                                                                                                                                                              |

| 5   | V <sub>DD</sub>   | Reference to input                                                            | The reference input pin is used to reduce flicker. The reference input voltage is as follows: $V_{DD} \le V_{GH} - 8.5 \text{ V}, V_{DD} = 0 \text{ to } 25 \text{ V}$                                                                                                                                       |

| 6   | V <sub>DPM</sub>  | Signal input 1                                                                | $ \begin{array}{l} V_{DPM} \mbox{ single input voltage is as follows:} \\ V_{DPM} = 0 \mbox{ V to } V_{GH}. \\ The \mbox{ V}_{DPM} \mbox{ pin is used to create a delay with the } V_{GH} \mbox{ to prevent system latch-up. } V_{DPM} \mbox{ also determines the time } V_{GH} \mbox{ is ON}. \end{array} $ |

| 7   | GND               | Ground                                                                        |                                                                                                                                                                                                                                                                                                              |

| 8   | V <sub>FLK</sub>  | Signal input 2                                                                | $V_{FLK}$ single input voltage is as follows: $V_{DPM}$ = 0 V to $V_{GH}.$ The $V_{FLK}$ determines the ON/OFF time of the TFT LCD and is produced from LCD timing controller module.                                                                                                                        |

#### Figure 2. Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                                        | Condition | Value       | Unit |

|-------------------|------------------------------------------------------------------|-----------|-------------|------|

| V <sub>GH</sub>   | DC Supply Voltage                                                |           | -0.5 to +40 | V    |

| V <sub>DD</sub>   | DC Supply Voltage                                                |           | -0.5 to +40 | V    |

| V <sub>FLK</sub>  | Input Voltage V <sub>FLK</sub>                                   |           | -0.5 to +40 | V    |

| V <sub>DPM</sub>  | Input Voltage V <sub>DPM</sub>                                   |           | -0.5 to +40 | V    |

| $V_{GH} - V_{CE}$ | Differential Voltage Between $V_{GH}$ and $V_{CE}$ Pins (Note 1) |           | 9.5         | V    |

| Ι <sub>ΙΚ</sub>   | DC Input Diode Current                                           |           | <b>≥</b> 50 | mA   |

| I <sub>OK</sub>   | DC Output Diode Current                                          |           | <b>≥</b> 50 | mA   |

| Ι <sub>Ο</sub>    | DC Output Current                                                |           | 50          | mA   |

| I <sub>GH</sub>   | DC Supply Current Per Supply Pin                                 |           | 50          | mA   |

| PD                | Power Dissipation                                                |           | 200         | mW   |

| TJ                | Junction Temperature                                             |           | 95          | °C   |

| T <sub>STG</sub>  | Storage Temperature                                              |           | -65 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. A differential voltage between the  $V_{GH}$  and  $V_{CE}$  pins ( $V_{GH} - V_{CE}$ ) occurs during the power-up and power-down procedure. The voltages on the  $V_{GH}$  and  $C_E$  pins are equal at steady-state conditions after power-up.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                           | Parameter                                                        | Test Condition                              | Min | Тур | Max             | Unit   |

|----------------------------------|------------------------------------------------------------------|---------------------------------------------|-----|-----|-----------------|--------|

| V <sub>GH</sub>                  | DC Supply Voltage (Note 2)                                       | $V_{GH} - V_{DD} \ge 8.5 V$                 | 15  | -   | 38              | V      |

| V <sub>DD</sub>                  | DC Supply Voltage                                                | $V_{DD} \le V_{GH} - 8.5 V$                 | 0   | -   | 25              | V      |

| V <sub>FLK</sub>                 | Input Voltage V <sub>FLK</sub>                                   | V <sub>GH_M</sub> = V <sub>GH</sub> – 1.2 V | 1.5 | -   | V <sub>GH</sub> | V      |

| V <sub>DPM</sub>                 | Input Voltage V <sub>DPM</sub>                                   | V <sub>GH_M</sub> = V <sub>DD</sub> + 1.5 V | 0   | -   | V <sub>GH</sub> | V      |

| T <sub>A</sub>                   | Operating Temperature Range                                      |                                             | -40 | -   | 85              | V      |

| V <sub>GH</sub> -V <sub>CE</sub> | Differential Voltage Between $V_{GH}$ and $V_{CE}$ Pins (Note 3) |                                             | -   | -   | 5.5             | v      |

|                                  |                                                                  | C <sub>E</sub> = 5 pF                       |     | 0.2 |                 |        |

|                                  |                                                                  | C <sub>E</sub> = 10 pF                      |     | 0.4 |                 |        |

|                                  |                                                                  | C <sub>E</sub> = 50 pF                      |     | 0.6 |                 |        |

| $\Delta t$ / $\Delta V_{GH}$     | Safe V <sub>GH</sub> Power–Up Slew Rate (Note 4)                 | C <sub>E</sub> = 150 pF                     | - 1 | 0.7 | _               | μs / V |

|                                  |                                                                  | C <sub>E</sub> = 220 pF                     |     | 0.8 |                 |        |

|                                  |                                                                  | C <sub>E</sub> = 500 pF                     | 1   | 1.2 |                 |        |

|                                  |                                                                  | C <sub>E</sub> = 1000 pF                    |     | 2.2 |                 |        |

Maximum recommended V<sub>GH</sub> supply voltage guaranteed by design.

A differential voltage between the V<sub>GH</sub> and V<sub>CE</sub> pins (V<sub>GH</sub> - V<sub>CE</sub>) occurs during the power-up and power-down procedure. The voltages on the V<sub>GH</sub> and C<sub>E</sub> pins are equal at steady-state conditions after power-up.

It is recommended that a ceramic or tantalum decoupling capacitor of 0.1 to 1 μF is used on the V<sub>GH</sub> power supply voltage. The capacitor should be placed adjacent to the NLHV001 and connected between V<sub>GH</sub> and Ground.

| Symbol               | Parameter                                         | Test Condition                                                                                                                                                  | Min                   | Тур                   | Max                   | Unit |

|----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|

| $V_{FLK_H}$          | FLK High Voltage                                  | V <sub>GH_M</sub> = V <sub>GH</sub> – 1.6                                                                                                                       | 1.5                   | -                     | V <sub>GH</sub>       | V    |

| V <sub>FLK_L</sub>   | FLK Low Voltage                                   | V <sub>GH_M</sub> = V <sub>DD</sub> + 1.5                                                                                                                       | 0                     | -                     | 0.5                   | V    |

| V <sub>DPM_H</sub>   | DPM High Voltage                                  | $V_{FLK} = 0 V, V_{GH_M} = V_{DD} - 0.2 V$                                                                                                                      | 1.5                   | -                     | V <sub>GH</sub>       | V    |

| V <sub>DPM_L</sub>   | DPM Low Voltage                                   | $V_{FLK} = 0 \text{ V},  V_{GH\_M} \leq 0.6 \text{ V}$                                                                                                          | 0                     | _                     | 0.5                   | V    |

| I <sub>DPM</sub>     | DPM ON Current                                    | $V_{FLK} = 3 V, V_{GH_M} = V_{GH}$                                                                                                                              | 0.2                   | 0.4                   | 2                     | mA   |

| R <sub>C</sub>       | R <sub>C</sub> (Resistor of V <sub>DPM</sub> pin) | $\label{eq:V_GH} \begin{array}{l} V_{GH} = 22 \ V, \ R_C \approx \left(V_{GH} - 0.9\right) \ / \\ I_{DPM} \ (Application \ Circuits \ 2 \ and \ 3) \end{array}$ | 10                    | 45                    | 100                   | kΩ   |

| V <sub>GH_M, H</sub> | Output High Voltage                               | l <sub>O</sub> = 10 mA                                                                                                                                          | V <sub>GH</sub> – 1.6 | V <sub>GH</sub> – 0.7 | -                     | V    |

| V <sub>GH_M, R</sub> | Output Reset Voltage                              | V <sub>DPM</sub> = 0 V, V <sub>FLK</sub> = 3 V                                                                                                                  |                       |                       | 0.6                   |      |

|                      |                                                   | V <sub>DPM</sub> = 0 V, V <sub>FLK</sub> = 0 V                                                                                                                  |                       | _                     |                       | V    |

| V <sub>GH_M, L</sub> | Output Low Voltage                                | $V_{DPM} = 3 V, V_{FLK} = 0 V,$<br>$I_O = -1 m A$                                                                                                               | V <sub>DD</sub> - 0.2 | V <sub>DD</sub> + 0.3 | V <sub>DD</sub> + 0.8 | V    |

| I <sub>GH</sub>      | Power Supply Input Current                        | $V_{GH}$ = 35 V, $V_{DD}$ = 15 V,<br>$V_{FLK}$ = $V_{DPM}$ = 3.3 V, $I_O$ = 0                                                                                   | -                     | 3.5                   | -                     | mA   |

| I <sub>DD</sub>      | Reference Input Current                           | V <sub>GH</sub> = 35 V, V <sub>DD</sub> = 15 V,<br>V <sub>FLK</sub> = 0 V, V <sub>DPM</sub> = 3.3 V, I <sub>O</sub> = 0                                         | -                     | 40                    | -                     | μΑ   |

| ELECTRICAL CHARACTERISTICS (V <sub>GH</sub> = 20 V, V <sub>DD</sub> = 10 V, V <sub>DPM</sub> = 2.2 V, V <sub>FLK</sub> = 2.2 V, V <sub>GH</sub> − V <sub>DD</sub> ≥ 8.5 V, T <sub>a</sub> = 25 °C, unless |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| otherwise noted.)                                                                                                                                                                                         |  |

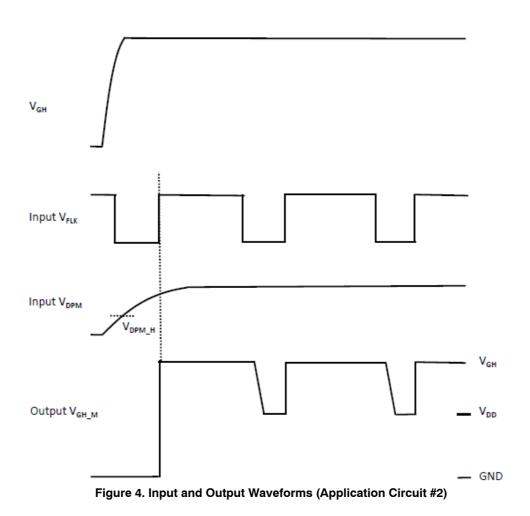

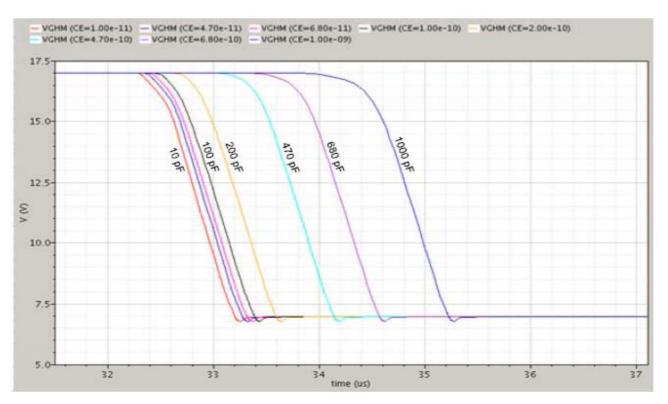

Figure 5. V<sub>GH\_M</sub> Output Propagation Delay (t<sub>phl</sub>) is controlled by C<sub>E</sub> (Application Circuit #1, V<sub>GH</sub> = 18 V, V<sub>DD</sub> = 7 V, R<sub>E</sub> = 3.9 k $\Omega$ , R<sub>L</sub> = 15 k $\Omega$ , C<sub>L</sub> = 220 pF, T<sub>a</sub> = 25 °C)

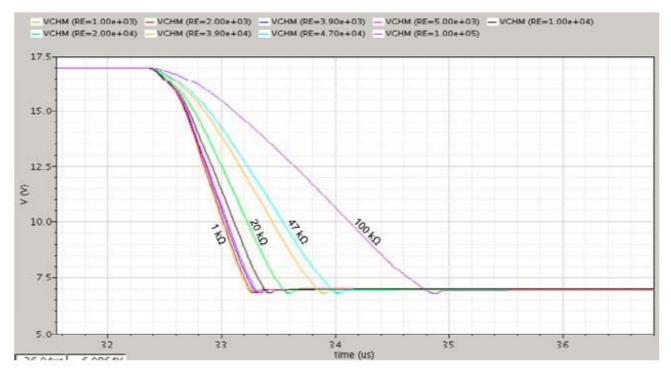

Figure 6. V<sub>GH\_M</sub> Output Transition Falling Edge (t<sub>fall</sub>) is controlled by R<sub>E</sub> (Application Circuit #1,  $V_{GH}$  = 18 V, V<sub>DD</sub> = 7 V, C<sub>E</sub> = 47 pF, R<sub>L</sub> = 15 k $\Omega$ , C<sub>L</sub> = 220 pF, T<sub>a</sub> = 25 °C)

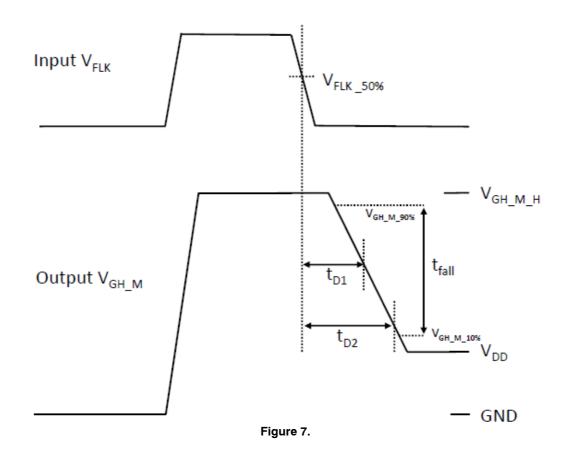

#### **Definition of Delay Time**

$t_{D1} = Delay Time 1 (t_{D_50-50}) = V_{FLK_50\%} to [V_{DD} + ((V_{GH_M_H}) - V_{DD}) x 0.50)]$  $t_{D2} = Delay Time 2 (t_{D_50-15}) = V_{FLK_50\%} to [V_{DD} + ((V_{GH_M_H}) - V_{DD}) x 0.15)]$  $t_{fall} = 90-to-10\% Fall Time = [V_{DD} + ((V_{GH_M_H}) - V_{DD}) x 0.90)] - [V_{DD} + ((V_{GH_M_H}) - V_{DD}) x 0.10)]$

#### **DELAY TIME CHARACTERISTICS**

(Application Circuit #1, V\_{DPM} = 3 V, V\_{FLK} = 3 V, R\_E = 15 k\Omega, R<sub>L</sub> = 15 kΩ, C<sub>L</sub> = 220 pF, T<sub>A</sub> = 25°C)

| Parameter                            | Test Condition                                                           | Тур | Unit |

|--------------------------------------|--------------------------------------------------------------------------|-----|------|

|                                      | V <sub>GH</sub> = 17 V, V <sub>DD</sub> = 6.7 V, C <sub>E</sub> = 100 pF | 2.4 | μs   |

|                                      | $V_{GH}$ = 17 V, $V_{DD}$ = 6.7 V, $C_{E}$ = 240 pF                      | 2.8 | μs   |

|                                      | V <sub>GH</sub> = 22.4 V, V <sub>DD</sub> = 10 V, C <sub>E</sub> = 91 pF | 2.3 | μs   |

| Delay Time 2 (t <sub>D_50-15</sub> ) | $V_{GH}$ = 22 V, $V_{DD}$ = 10 V, $C_{E}$ = 220 pF                       | 2.8 | μs   |

|                                      | $V_{GH}$ = 25.4 V, $V_{DD}$ = 15.4 V, $C_{E}$ = 56 pF                    | 2.4 | μs   |

|                                      | $V_{GH}$ = 25.4 V, $V_{DD}$ = 15.4 V, $C_E$ = 130 pF                     | 2.5 | μs   |

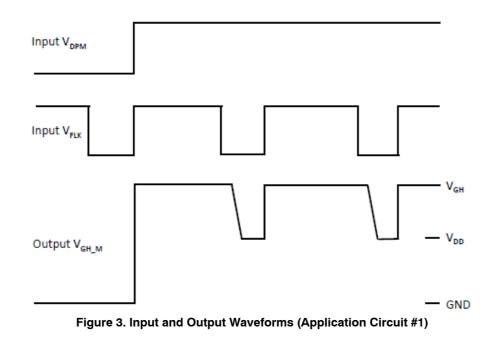

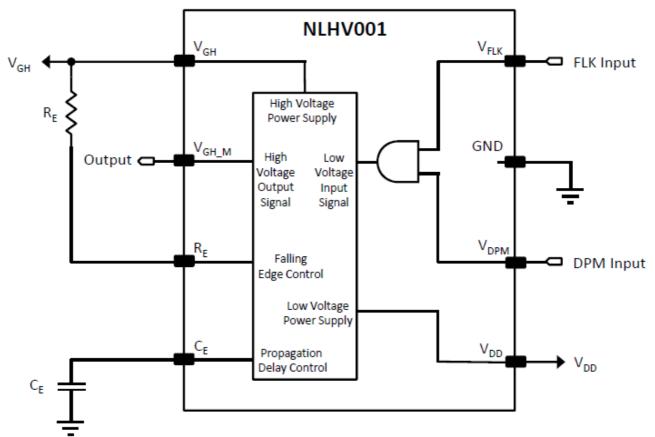

Figure 8. Application #1 Circuit Schematic

Notes:

1.  $V_{DPM}$  can rise only after  $V_{GH}$  is valid.

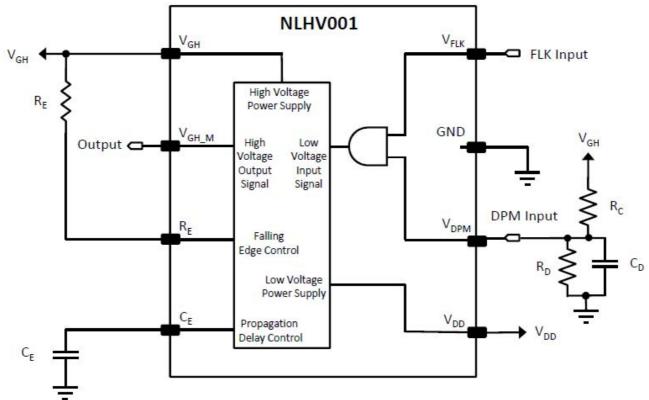

Notes:

- 1.  $V_{DPM}$  is produced by a Low Pass Filter (LPF) on  $V_{GH}$  pin with  $R_C$  and  $C_D$ .

- 2.  $R_{\rm D}$  is a  $V_{DPM}$  pull–down resistor.

# APPLICATION 2: $V_{\text{GH}\_\text{M}}$ SIGNAL DELAY TIME CHARACTERISTICS

| V <sub>GH</sub> (V) | V <sub>DD</sub> (V) | C <sub>D</sub> (μF) | R <sub>D</sub> (kΩ) | R <sub>C</sub> (kΩ) | V <sub>GH_M</sub> ON Delay Time (when<br>V <sub>GH</sub> ON) t <sub>on</sub> (ms) | V <sub>DPM</sub> Pin Discharge Time (when<br>V <sub>GH</sub> OFF) t <sub>off</sub> (ms) |

|---------------------|---------------------|---------------------|---------------------|---------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                     |                     | 1                   | 15                  | 50                  | 17.9                                                                              | 3.4                                                                                     |

| 22                  | 12                  | 1                   | 1.5                 | 20                  | 5.5                                                                               | 1.4                                                                                     |

|                     |                     | 1                   | 0.620               | 10                  | 1.7                                                                               | 0.74                                                                                    |

#### **APPLICATION 2: FUNCTION DESCRIPTION**

| Name           | Comment                                                           | Function                                                       |  |

|----------------|-------------------------------------------------------------------|----------------------------------------------------------------|--|

| R <sub>C</sub> | $R_{C}$ and $C_{D}$ determines the time when the $V_{DPM}$ pin is |                                                                |  |

| CD             | charged.                                                          | $t_{on}$ = Time when V <sub>GH_M</sub> is high                 |  |

| R <sub>D</sub> | $R_D$ determines the time when the $V_{DPM}$ pin is discharged.   | $t_{off}$ = Time when V <sub>DPM</sub> pin is fully discharged |  |

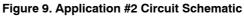

Figure 10. Application #3 Circuit Schematic

#### **APPLICATION 3: FUNCTION DESCRIPTION**

| Name           | Comment                                                     | Function                                     |

|----------------|-------------------------------------------------------------|----------------------------------------------|

| R <sub>A</sub> | $\rm R_A$ and $\rm R_B$ set the $\rm V_{DD}$ voltage.       | $V_{DD} = V_{GH} \times (R_B / (R_A + R_B))$ |

| R <sub>B</sub> |                                                             |                                              |

| R <sub>C</sub> | $R_C$ determines the voltage that $V_DPM$ pin becomes high. |                                              |

Notes:

1. V<sub>DPM</sub> produced by external R<sub>C</sub> and internal R and C.

2.  $V_{DD}\xspace$  created from external resistors  $R_A\xspace$  and  $R_B.$

3.  $V_{GH}$  should be higher than 18 V to meet  $V_{DPM \ H.}$

4.  $R_A = 15 \text{ k}\Omega$ ,  $R_B = 10 \text{ k}\Omega$ ,  $R_C = 45 \text{ k}\Omega$ ,  $R_E = 15 \text{ k}\Omega$ ,  $R_L = 15 \text{ k}\Omega$ ,  $C_E = 220 \text{ pF}$ ,  $C_L = 100 \text{ pF}$

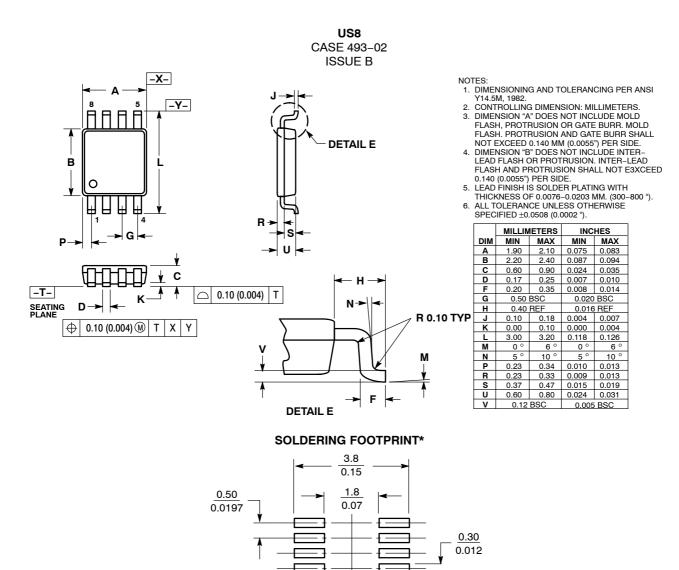

#### **DEVICE ORDERING INFORMATION**

| Device Order Number | Package Type     | Shipping <sup>†</sup> |

|---------------------|------------------|-----------------------|

| NLHV001USG          | US8<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### PACKAGE DIMENSIONS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

1.0

0.0394

**ON Semiconductor** and **ON** are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemic.com/site/pdf/Patent-Marking.pdf. SCILLC protects for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC products for any paricular purpose, nor other application is intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, and claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the neglicable copyright as a fuel applicable to manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

$\left(\frac{\text{mm}}{\text{inches}}\right)$

SCALE 8:1

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative