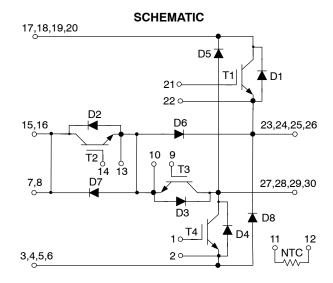

## **Q1PACK Module**

This high-density, integrated power module combines high-performance IGBTs with rugged anti-parallel diodes.

#### **Features**

- Extremely Efficient Trench with Fieldstop Technology

- Low Switching Loss Reduces System Power Dissipation

- Module Design Offers High Power Density

- Low Inductive Layout

- Q1PACK Package with Press-Fit and Solder Pins

#### **Typical Applications**

- Solar Inverters

- Uninterruptable Power Supplies

## ON Semiconductor®

www.onsemi.com

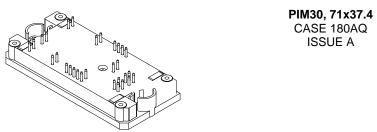

#### **PACKAGE PICTURE**

Q1PACK CASE 180AD PRESS FIT Q1PACK CASE 180AQ SOLDER PINS

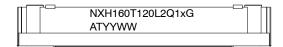

### **DEVICE MARKING**

x = P or S

G = Pb-Free Package

AT = Assembly & Test Site Code YYWW = Year and Work Week Code

#### **PIN ASSIGNMENTS**

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 14 of this data sheet.

Table 1. ABSOLUTE MAXIMUM RATINGS

| Rating                                                                                                    | Symbol           | Value | Unit |

|-----------------------------------------------------------------------------------------------------------|------------------|-------|------|

| HALFBRIDGE IGBT INVERSE DIODE (D1, D4)                                                                    |                  |       |      |

| Peak Repetitive Reverse Voltage                                                                           | $V_{RRM}$        | 1200  | V    |

| Forward Current, DC @ T <sub>h</sub> = 80°C                                                               | I <sub>F</sub>   | 20    | Α    |

| Repetitive Peak Forward Current T <sub>pulse</sub> limited by T <sub>jmax</sub>                           | I <sub>FRM</sub> | 80    | Α    |

| Power Dissipation per Diode $T_j = T_{jmax} \qquad \qquad T_h = 80^{\circ}C$                              | P <sub>tot</sub> | 51    | W    |

| Maximum Junction Temperature                                                                              | T <sub>J</sub>   | 150   | °C   |

| HALFBRIDGE IGBT (T1, T4)                                                                                  |                  |       |      |

| Collector-emitter voltage                                                                                 | V <sub>CES</sub> | 1200  | V    |

| Collector current @ T <sub>h</sub> = 80°C                                                                 | I <sub>C</sub>   | 140   | А    |

| Pulsed Collector Current, T <sub>pulse</sub> Limited by T <sub>jmax</sub>                                 | I <sub>CM</sub>  | 480   | А    |

| Power Dissipation per IGBT $T_{j} = T_{jmax} \qquad \qquad T_{h} = 80^{\circ}C$                           | P <sub>tot</sub> | 280   | W    |

| Gate-emitter voltage                                                                                      | $V_{GE}$         | ±20   | V    |

| Short Circuit Withstand Time $V_{GE} = 15 \text{ V}, V_{CE} = 600 \text{ V}, T_J \le 150^{\circ}\text{C}$ | T <sub>SC</sub>  | 10    | μs   |

| Maximum Junction Temperature                                                                              | T <sub>J</sub>   | 150   | °C   |

| NP DIODE (D6, D7)                                                                                         |                  |       |      |

| Peak Repetitive Reverse Voltage                                                                           | $V_{RRM}$        | 650   | V    |

| Forward Current, DC @ T <sub>h</sub> = 80°C                                                               | I <sub>F</sub>   | 58    | А    |

| Repetitive Peak Forward Current, T <sub>pulse</sub> limited by T <sub>Jmax</sub>                          | I <sub>FRM</sub> | 200   | А    |

| Power Dissipation Per Diode $T_j = T_{jmax}$ $T_h = 80^{\circ}C$                                          | P <sub>tot</sub> | 89    | W    |

| Maximum Junction Temperature                                                                              | TJ               | 150   | °C   |

| NP IGBT (T2, T3)                                                                                          |                  |       |      |

| Collector-emitter voltage                                                                                 | V <sub>CES</sub> | 650   | V    |

| Collector current @ T <sub>h</sub> = 80°C                                                                 | I <sub>C</sub>   | 83    | А    |

| Pulsed collector current, T <sub>pulse</sub> limited by T <sub>Jmax</sub>                                 | I <sub>CM</sub>  | 235   | А    |

| Power Dissipation Per IGBT $T_j = T_{jmax} \qquad T_h = 80^{\circ}C$                                      | P <sub>tot</sub> | 117   | W    |

| Gate-emitter voltage                                                                                      | V <sub>GE</sub>  | ±20   | V    |

| Short Circuit Withstand Time $V_{GE}$ = 15 V, $V_{CE}$ = 400 V, $T_{J}$ $\leq$ 150°C                      | T <sub>sc</sub>  | 5     | μs   |

| Maximum Junction Temperature                                                                              | TJ               | 150   | °C   |

| NP INVERSE DIODE (D2, D3)                                                                                 |                  |       |      |

| Peak Repetitive Reverse Voltage                                                                           | $V_{RRM}$        | 650   | V    |

| Forward Current, DC @ T <sub>h</sub> = 80°C                                                               | I <sub>F</sub>   | 17    | А    |

| Repetitive Peak Forward Current, $T_{\text{pulse}}$ limited by $T_{\text{Jmax}}$                          | I <sub>FRM</sub> | 68    | Α    |

| Power Dissipation Per Diode $T_j = T_{jmax} \qquad T_h = 80^{\circ}C$                                     | P <sub>tot</sub> | 28    | W    |

| Maximum Junction Temperature                                                                              | TJ               | 150   | °C   |

| HALFBRIDGE DIODE (D5, D8)                                                                                 |                  |       |      |

| Peak Repetitive Reverse Voltage                                                                           | $V_{RRM}$        | 1200  | V    |

| Forward Current, DC @ T <sub>h</sub> = 80°C (per diode)                                                   | I <sub>F</sub>   | 45    | А    |

| Repetitive Peak Forward Current, T <sub>pulse</sub> limited by T <sub>Jmax</sub>                          | I <sub>FRM</sub> | 180   | А    |

| Power Dissipation Per Diode $T_j = T_{jmax}$ $T_h = 80^{\circ}C$                                          | P <sub>tot</sub> | 78    | W    |

|                                                                                                           |                  |       | •    |

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Rating                                          | Symbol             | Value                          | Unit      |

|-------------------------------------------------|--------------------|--------------------------------|-----------|

| HALFBRIDGE DIODE (D5, D8)                       | <u>.</u>           |                                |           |

| Junction Temperature                            | T <sub>J</sub>     | 150                            | °C        |

| THERMAL PROPERTIES                              |                    |                                |           |

| Operating Temperature under switching condition | T <sub>VJ OP</sub> | -40 to (T <sub>jmax</sub> -25) | °C        |

| Storage Temperature range                       | T <sub>stg</sub>   | -40 to 125                     | °C        |

| INSULATION PROPERTIES                           |                    |                                |           |

| Isolation test voltage, t = 1 sec, 60 Hz/50 Hz  | V <sub>is</sub>    | 3000                           | $V_{RMS}$ |

| Creepage distance                               |                    | 12.7                           | mm        |

| Clearance                                       |                    | 8.06                           | mm        |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Table 2. ELECTRICAL CHARACTERISTICS (T<sub>.J</sub> = 25°C unless otherwise specified)

| Parameter                             | Test Conditions                                                                                                                                 | Symbol               | Min    | Тур          | Max       | Unit |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|--------------|-----------|------|

| HALFBRIDGE IGBT INVERSE DIODE (D1     | , D4) CHARACTERISTICS                                                                                                                           |                      |        |              |           |      |

| Forward voltage                       | $I_F = 7 \text{ A}, T_j = 25^{\circ}\text{C}$<br>$I_F = 7 \text{ A}, T_j = 125^{\circ}\text{C}$                                                 | V <sub>F</sub>       | -<br>- | 1.46<br>1.49 | 2.7<br>_  | V    |

| Thermal Resistance - chip-to-heatsink | Thermal grease, Thickness = 2 Mil $\pm$ 2%, $\lambda$ = 1 W/mK                                                                                  | R <sub>thJH</sub>    |        | 1.864        |           | °C/W |

| HALFBRIDGE IGBT (T1, T4) CHARACTE     | RISTICS                                                                                                                                         |                      |        |              |           |      |

| Collector-emitter saturation voltage  | $V_{GE}$ = 15 V, $I_{C}$ = 160 A, $T_{j}$ = 25°C $V_{GE}$ = 15 V, $I_{C}$ = 160 A, $T_{j}$ = 125°C                                              | V <sub>CE(sat)</sub> | -      | 2.06<br>2.10 | 2.50<br>— | V    |

| Gate-emitter threshold voltage        | $V_{GE} = V_{CE}$ , $I_C = 6$ mA                                                                                                                | V <sub>GE(TH)</sub>  | 5.0    | 5.80         | 6.50      | V    |

| Collector-emitter cutoff current      | V <sub>GE</sub> = 0 V, V <sub>CE</sub> = 1200 V                                                                                                 | I <sub>CES</sub>     | -      | -            | 800       | μΑ   |

| Gate leakage current                  | V <sub>GE</sub> = 20 V, V <sub>CE</sub> = 0 V                                                                                                   | I <sub>GES</sub>     | -      | -            | 800       | nA   |

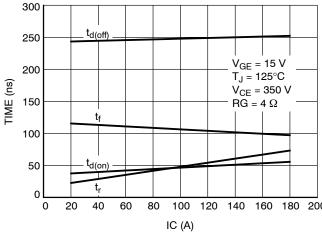

| Turn-on delay time                    | T <sub>j</sub> = 125°C                                                                                                                          | t <sub>d(on)</sub>   | -      | 55           | _         | ns   |

| Rise time                             | $V_{CE} = 350 \text{ V, } I_{C} = 100 \text{ A}$                                                                                                | t <sub>r</sub>       | =      | 50           | =         |      |

| Turn-off delay time                   | $V_{GE} = \pm 15 \text{ V}, R_G = 4 \Omega$                                                                                                     | t <sub>d(off)</sub>  | -      | 430          | _         |      |

| Fall time                             |                                                                                                                                                 | t <sub>f</sub>       | _      | 105          | _         |      |

| Turn on switching loss                |                                                                                                                                                 | E <sub>on</sub>      | -      | 2.73         | _         | mJ   |

| Turn off switching loss               |                                                                                                                                                 | E <sub>off</sub>     | -      | 3.58         | _         |      |

| Input capacitance                     | $V_{CE} = 25 \text{ V. } V_{GE} = 0 \text{ V. } f = 10 \text{ kHz}$                                                                             | C <sub>ies</sub>     | _      | 38164        | _         | pF   |

| Output capacitance                    |                                                                                                                                                 | C <sub>oes</sub>     | _      | 644          | _         |      |

| Reverse transfer capacitance          |                                                                                                                                                 | C <sub>res</sub>     | _      | 784          | _         |      |

| Gate charge total                     | V <sub>CE</sub> = 600 V, I <sub>C</sub> = 160 A, V <sub>GE</sub> = 15 V                                                                         | $Q_g$                | _      | 1664         | _         | nC   |

| Thermal Resistance - chip-to-heatsink | Thermal grease, Thickness = 2 Mil $\pm$ 2%, $\lambda$ = 1 W/mK                                                                                  | R <sub>thJH</sub>    |        | 0.337        |           | °C/W |

| NP DIODE (D6, D7) CHARACTERISTICS     |                                                                                                                                                 |                      |        |              |           |      |

| Forward voltage                       | $V_{GE} = 0 \text{ V}, I_F = 150 \text{ A}, T_j = 25^{\circ}\text{C}$<br>$V_{GE} = 0 \text{ V}, I_F = 150 \text{ A}, T_j = 125^{\circ}\text{C}$ | V <sub>F</sub>       | -<br>- | 2.15<br>2.36 | 2.60<br>- | V    |

| Reverse leakage current               | V <sub>CE</sub> = 650 V, V <sub>GE</sub> = 0 V                                                                                                  | lr                   | -      | -            | 200       | μΑ   |

| Reverse recovery time                 | T <sub>j</sub> = 125°C                                                                                                                          | trr                  | -      | 225          | _         | ns   |

| Reverse recovery charge               | $V_{CE} = 350 \text{ V}, I_{C} = 100 \text{ A}$                                                                                                 | Qrr                  | -      | 6.15         | _         | μC   |

| Peak reverse recovery current         | $V_{GE} = \pm 15 \text{ V}, R_G = 4 \Omega$                                                                                                     | Irrm                 | -      | 85           | _         | Α    |

| Peak rate of fall of recovery current |                                                                                                                                                 | di/dtmax             | -      | 1315         | _         | A/μs |

| Reverse recovery energy               |                                                                                                                                                 | Err                  | -      | 1.336        | _         | mJ   |

| Thermal Resistance - chip-to-heatsink | Thermal grease,<br>Thickness = 2 Mil $\pm$ 2%, $\lambda$ = 1 W/mK                                                                               | RthJH                | -      | 1.07         | _         | °C/W |

**Table 2. ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C unless otherwise specified)

| Parameter Test Conditions             |                                                                                                                                                   | Symbol               | Min    | Тур          | Max  | Unit |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|--------------|------|------|

| NP IGBT (T2, T3)                      |                                                                                                                                                   |                      |        |              |      |      |

| Collector-emitter saturation voltage  | $V_{CE}$ = 15 V, $I_{C}$ = 150 A, $T_{j}$ = 25°C $V_{CE}$ = 15 V, $I_{C}$ = 150 A, $T_{j}$ = 125°C                                                | V <sub>CE(sat)</sub> | -<br>- | 1.65<br>1.84 | 2.0  | V    |

| Gate-emitter threshold voltage        | $V_{GE} = V_{CE}$ , $I_C = 8 \text{ mA}$                                                                                                          | V <sub>GE(TH)</sub>  | 5.0    | 6.10         | 6.90 | V    |

| Collector-emitter cutoff current      | V <sub>GE</sub> = 0 V, V <sub>CE</sub> = 650 V                                                                                                    | I <sub>CES</sub>     | -      | _            | 400  | μΑ   |

| Gate leakage current                  | V <sub>GE</sub> = 20 V, V <sub>CE</sub> = 0 V                                                                                                     | I <sub>GES</sub>     | -      | _            | 800  | nA   |

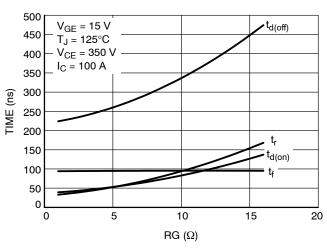

| Turn-on delay time                    | T <sub>j</sub> = 125°C                                                                                                                            | t <sub>d(on)</sub>   | =      | 46           | =    | ns   |

| Rise time                             | $V_{CE} = 350 \text{ V}, I_{C} = 100 \text{ A}$                                                                                                   | t <sub>r</sub>       | -      | 48           | _    |      |

| Turn-off delay time                   | $V_{GE} = \pm 15 \text{ V}, R_G = 4 \Omega$                                                                                                       | t <sub>d(off)</sub>  | -      | 250          | -    |      |

| Fall time                             |                                                                                                                                                   | t <sub>f</sub>       | -      | 105          | _    |      |

| Turn on switching loss                |                                                                                                                                                   | E <sub>on</sub>      | -      | 1.245        | _    | mJ   |

| Turn off switching loss               |                                                                                                                                                   | E <sub>off</sub>     | -      | 2.525        | _    |      |

| Input capacitance                     | $V_{CE} = 25 \text{ V}, V_{GE} = 0 \text{ V}, f = 10 \text{ kHz}$                                                                                 | C <sub>ies</sub>     | -      | 19380        | -    | pF   |

| Output capacitance                    |                                                                                                                                                   | C <sub>oes</sub>     | -      | 570          | -    |      |

| Reverse transfer capacitance          |                                                                                                                                                   | C <sub>res</sub>     | -      | 496          | -    |      |

| Gate charge total                     | V <sub>CE</sub> = 480 V, I <sub>C</sub> = 150 A, V <sub>GE</sub> = 15 V                                                                           | $Q_g$                | =      | 790          | -    | nC   |

| Thermal Resistance - chip-to-heatsink | Thermal grease,<br>Thickness = 2 Mil $\pm$ 2%, $\lambda$ = 1 W/mK                                                                                 | R <sub>thJH</sub>    | -      | 0.81         | -    | °C/W |

| NP INVERSE DIODE (D2, D3)             |                                                                                                                                                   |                      |        |              |      |      |

| Forward voltage                       | $V_{GE} = 0 \text{ V, } I_F = 15 \text{ A, } T_j = 25^{\circ}\text{C}$<br>$V_{GE} = 0 \text{ V, } I_F = 15 \text{ A, } T_j = 125^{\circ}\text{C}$ | V <sub>F</sub>       | -<br>- | 1.60<br>1.59 | 2.20 | V    |

| Thermal Resistance - chip-to-heatsink | Thermal grease,<br>Thickness = 2 Mil $\pm$ 2%, $\lambda$ = 1 W/mK                                                                                 | R <sub>thJH</sub>    |        | 3.43         |      | °C/W |

| HALFBRIDGE DIODE (D5, D8)             |                                                                                                                                                   |                      |        |              |      |      |

| Forward voltage                       | $V_{GE}$ = 0 V, $I_F$ = 150 A, $T_j$ = 25°C $V_{GE}$ = 0 V, $I_F$ = 150 A, $T_j$ = 125°C                                                          | V <sub>F</sub>       | -<br>- | 2.50<br>2.80 | 3.50 | V    |

| Reverse leakage current               | V <sub>CE</sub> = 1200 V, V <sub>GE</sub> = 0 V                                                                                                   | lr                   | =      | -            | 200  | μΑ   |

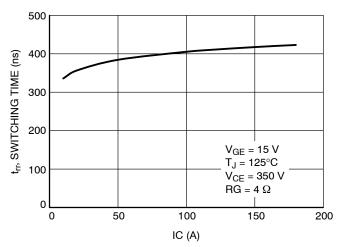

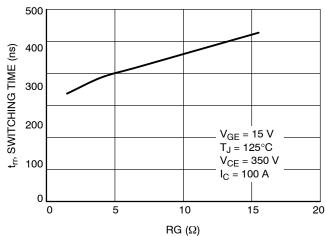

| Reverse recovery time                 | T <sub>j</sub> = 125°C                                                                                                                            | trr                  | =      | 405          | _    | ns   |

| Reverse recovery charge               | $V_{CE} = 350 \text{ V}, I_{C} = 100 \text{ A}$                                                                                                   | Qrr                  | =      | 15.5         | _    | μС   |

| Peak reverse recovery current         | $V_{GE} = \pm 15 \text{ V}, R_G = 4 \Omega$                                                                                                       | Irrm                 | =      | 220          | _    | Α    |

| Peak rate of fall of recovery current |                                                                                                                                                   | di/dtmax             | =      | 5440         | _    | A/μs |

| Reverse recovery energy               |                                                                                                                                                   | Err                  | =      | 5.225        | _    | mJ   |

| Thermal Resistance – chip-to-heatsink | Thermal grease,<br>Thickness = 2 Mil $\pm$ 2%, $\lambda$ = 1 W/mK                                                                                 | RthJH                | -      | 1.213        | -    | °C/M |

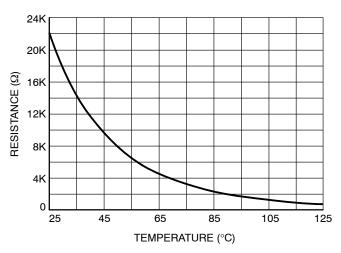

| THERMISTOR CHARACTERISTICS            |                                                                                                                                                   |                      |        |              |      |      |

| Nominal resistance                    |                                                                                                                                                   | R <sub>25</sub>      | _      | 22           | -    | kΩ   |

| Nominal resistance                    | T = 100°C                                                                                                                                         | R <sub>100</sub>     | -      | 1486         | -    | Ω    |

| Deviation of R25                      |                                                                                                                                                   | DR/R                 | -5     | _            | 5    | %    |

| Power dissipation                     |                                                                                                                                                   | $P_{D}$              | -      | 200          | -    | mW   |

| Power dissipation constant            |                                                                                                                                                   |                      | -      | 2            | -    | mW/k |

| B-value                               | B(25/50), tol ±3%                                                                                                                                 |                      | -      | 3950         | -    | K    |

| B-value                               | B(25/100), tol ±3%                                                                                                                                |                      | _      | 3998         | _    | K    |

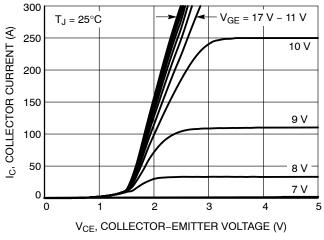

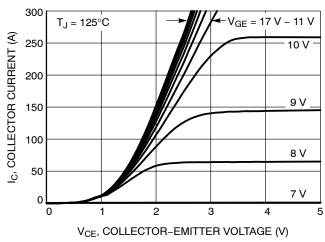

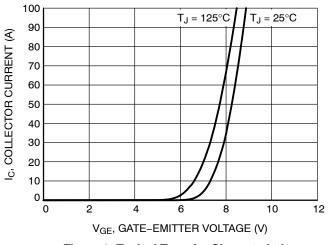

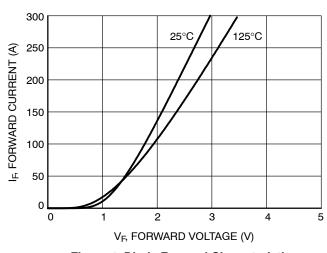

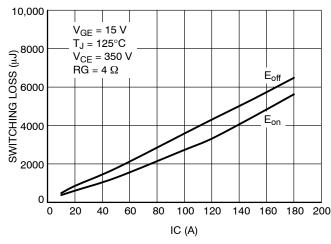

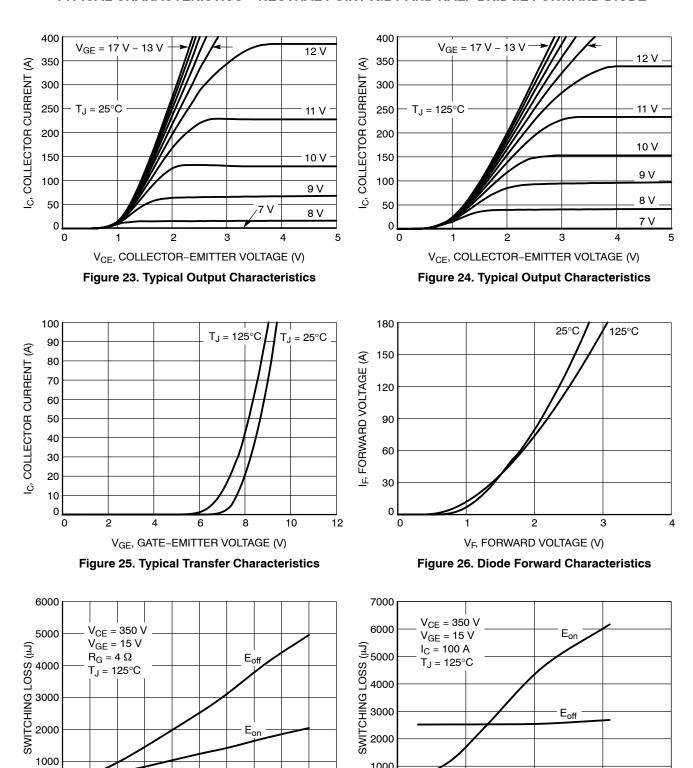

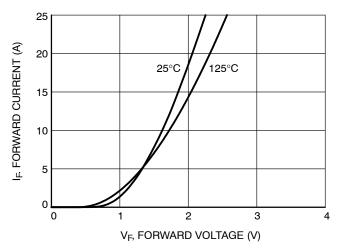

#### TYPICAL CHARACTERISTICS - HALF BRIDGE IGBT AND NEUTRAL POINT FORWARD DIODE

Figure 1. Typical Output Characteristics

Figure 2. Typical Output Characteristics

Figure 3. Typical Transfer Characteristics

Figure 4. Diode Forward Characteristics

Figure 5. Typical Switching Loss vs. IC

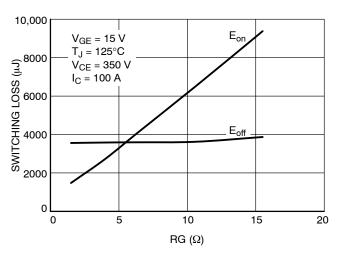

Figure 6. Typical Switching Loss vs. RG

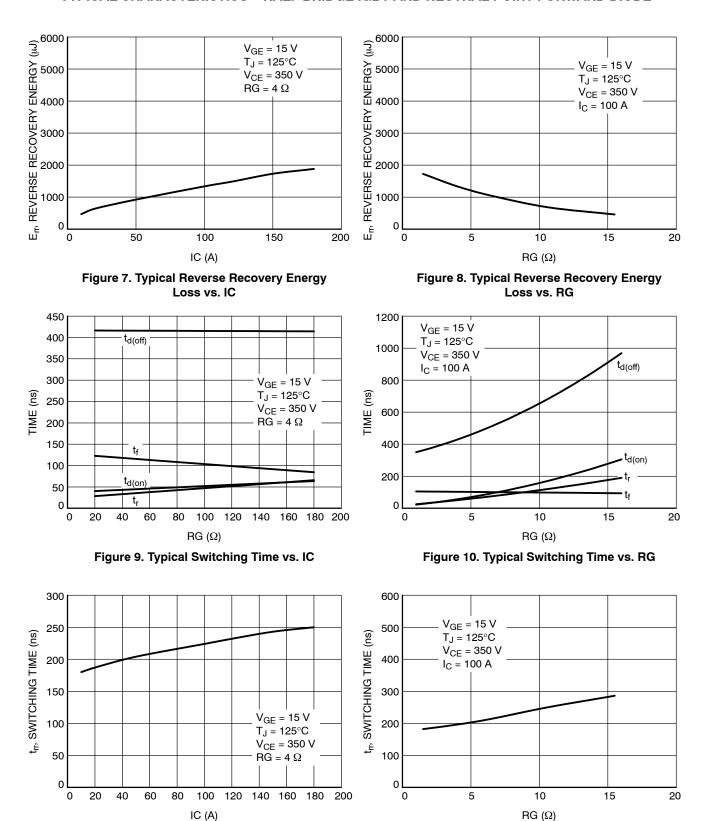

#### TYPICAL CHARACTERISTICS - HALF BRIDGE IGBT AND NEUTRAL POINT FORWARD DIODE

Figure 12. Typical Reverse Recovery Time vs. RG

Figure 11. Typical Reverse Recovery Time vs.

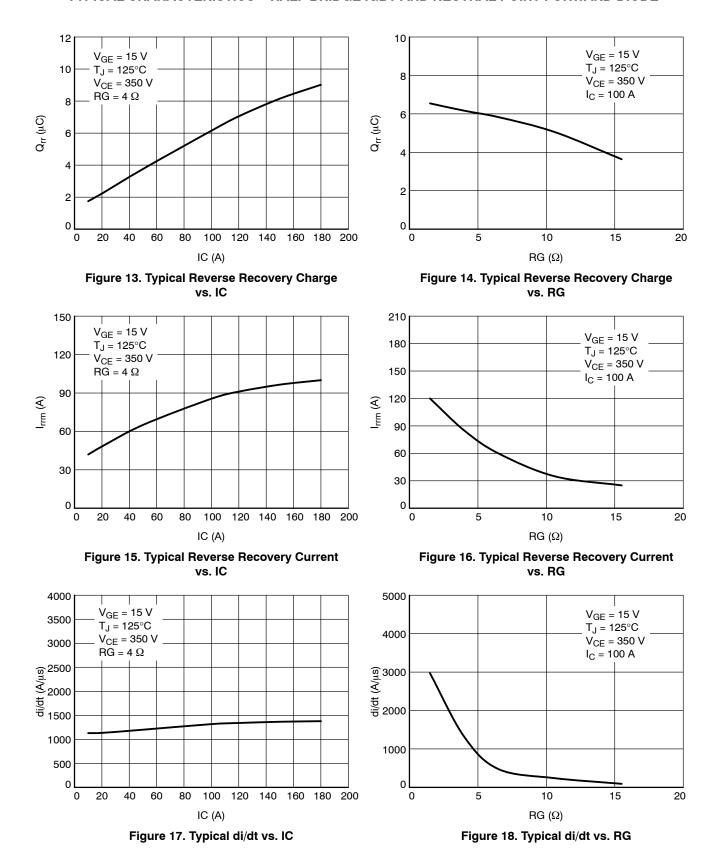

#### TYPICAL CHARACTERISTICS - HALF BRIDGE IGBT AND NEUTRAL POINT FORWARD DIODE

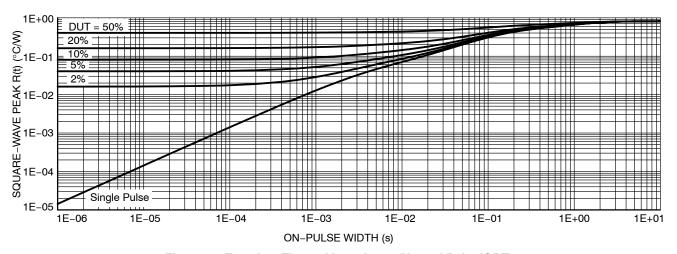

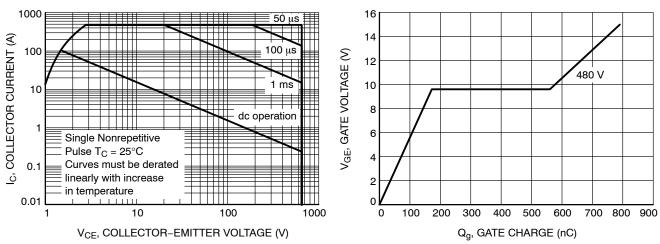

#### TYPICAL CHARACTERISTICS - HALF BRIDGE IGBT AND NEUTRAL POINT FORWARD DIODE

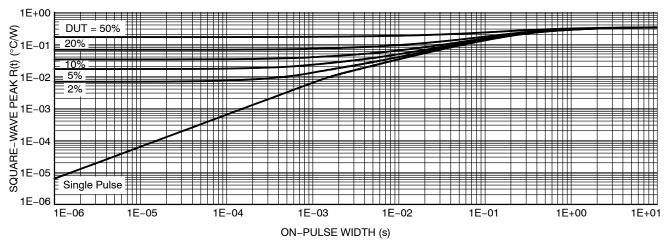

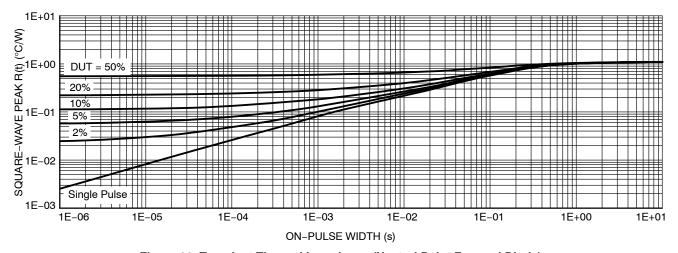

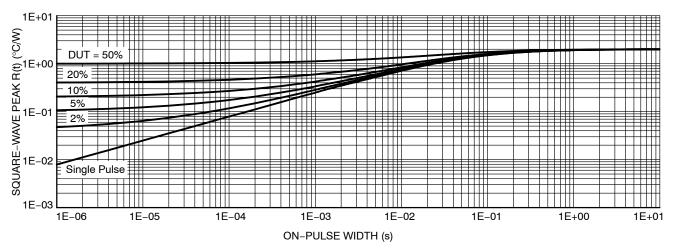

Figure 19. Transient Thermal Impedance (Half Bridge IGBT)

Figure 20. Transient Thermal Impedance (Neutral Point Forward Diode)

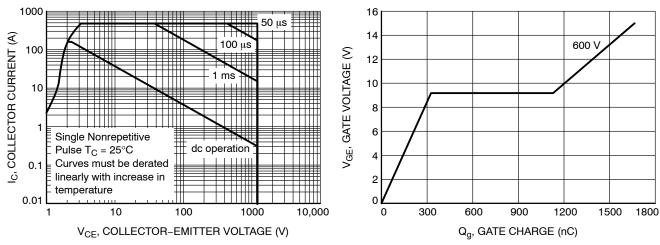

Figure 21. Safe Operating Area

Figure 22. Gate Voltage vs. Gate Charge

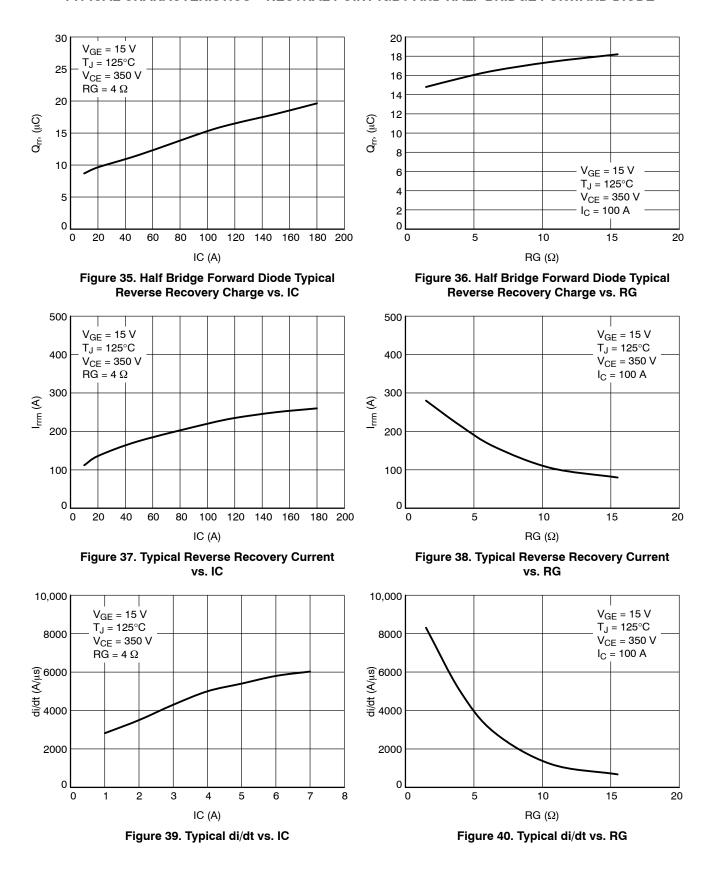

#### TYPICAL CHARACTERISTICS - NEUTRAL POINT IGBT AND HALF BRIDGE FORWARD DIODE

IC (A) Figure 27. Typical Switching Loss vs. IC

140 160 180 200

$RG(\Omega)$ Figure 28. Typical Switching Loss vs. RG

#### TYPICAL CHARACTERISTICS - NEUTRAL POINT IGBT AND HALF BRIDGE FORWARD DIODE

3 8000 V<sub>CE</sub> = 350 V V<sub>GE</sub> = 15 V V<sub>GE</sub> = 15 V V<sub>GE</sub> = 15 V V<sub>GE</sub> = 100 A T<sub>J</sub> = 125°C V<sub>GE</sub> = 15 V V<sub>GE</sub>

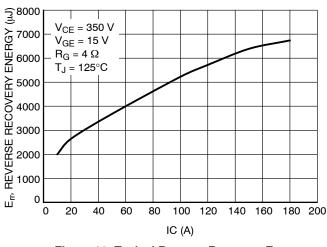

Figure 29. Typical Reverse Recovery Energy Loss vs. IC

Figure 30. Typical Reverse Recovery Energy Loss vs. RG

Figure 31. Typical Switching Time vs. IC

Figure 32. Typical Switching Time vs. RG

Figure 33. Half Bridge Forward Diode Typical Reverse Recovery Time vs. IC

Figure 34. Half Bridge Forward Diode Typical Reverse Recovery Time vs. RG

#### TYPICAL CHARACTERISTICS - NEUTRAL POINT IGBT AND HALF BRIDGE FORWARD DIODE

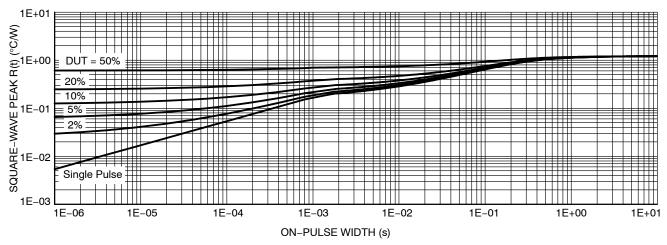

#### TYPICAL CHARACTERISTICS - NEUTRAL POINT IGBT AND HALF BRIDGE FORWARD DIODE

Figure 41. Transient Thermal Impedance (Neutral Point IGBT)

Figure 42. Transient Thermal Impedance (Half Bridge Forward Diode)

Figure 43. Safe Operating Area Figure 44. Gate Voltage vs. Gate Charge

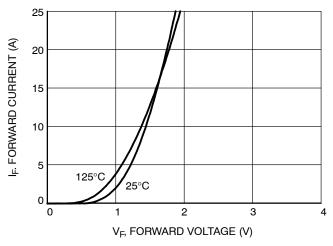

## TYPICAL CHARACTERISTICS - HALF BRIDGE INVERSE DIODE

Figure 45. Transient Thermal Impedance

Figure 46. Diode Forward Characteristics

## TYPICAL CHARACTERISTICS - NEUTRAL POINT INVERSE DIODE

Figure 47. Diode Forward Characteristics

## TYPICAL CHARACTERISTICS - THERMISTOR

Figure 48. Thermistor Characteristics

## **ORDERING INFORMATION**

| Orderable Part Number         | Package                                          | Shipping                |

|-------------------------------|--------------------------------------------------|-------------------------|

| NXH160T120L2Q1PG (Press Fit)  | Q1PACK - Case 180AD<br>(Pb-Free and Halide-Free) | 21 Units / Blister Tray |

| NXH160T120L2Q1SG (Solder Pin) | Q1PACK - Case 180AQ<br>(Pb-Free and Halide-Free) | 21 Units / Blister Tray |

**DATE 28 NOV 2017**

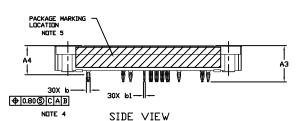

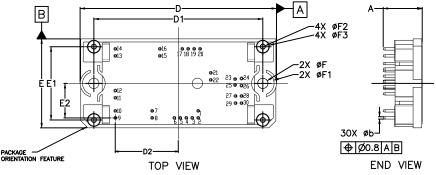

| MOUNTIN | G HOLE P | OSITION | Ц | MOUNTIN | G HOLE P | OSITION |  |

|---------|----------|---------|---|---------|----------|---------|--|

| PIN     | х        | Y       | l | PIN     | X        |         |  |

| 1       | 8.30     | 11.55   |   | 16      | -7.800   | -14.50  |  |

| a       | 8.30     | 14.50   |   | 17      | 1.60     | -14.50  |  |

| з       | 5.80     | 14.50   |   | 18      | 4.10     | -14.50  |  |

| 4       | 3.30     | 14.50   |   | 19      | 6.60     | -14.50  |  |

| 5       | 0.80     | 14.50   |   | 20      | 9.10     | -14.50  |  |

| 6       | -1.70    | 14.50   |   | 21      | 13.60    | -4.40   |  |

| 7       | -11.05   | 11.55   | П | 22      | 13.60    | -1.45   |  |

| 8       | -11.05   | 14.50   |   | 23      | 23.80    | -1.80   |  |

| 9       | -26.50   | 14.50   |   | 24      | 26.50    | -2.05   |  |

| 10      | -26.50   | 11.55   |   | 25      | 23.80    | 01/70   |  |

| 11      | -26.50   | 6.05    |   | 26      | 26.50    | 0.95    |  |

| 12      | -26.50   | 3.05    |   | 27      | 24.00    | 5.30    |  |

| 13      | -26.50   | -11.55  |   | 28      | 26.50    | 5.30    |  |

| 14      | -26.50   | -14.50  |   | 29      | 24.00    | 8.30    |  |

| 15      | -7.80    | -11.55  |   | 30      | 26.50    | 8.30    |  |

NOTE 4

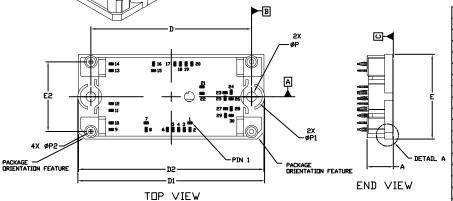

|     | MILLIMETERS |       |  |  |  |

|-----|-------------|-------|--|--|--|

| DIM | MIN.        | NDM.  |  |  |  |

| Α   | 11.10       | 12.10 |  |  |  |

| A3  | 15.50       | 16.50 |  |  |  |

| A4  | 12.88       | BSC   |  |  |  |

| A5  | 0.00        | 0.45  |  |  |  |

| ٥   | 1.61        | 1.71  |  |  |  |

| b1  | 0.75        | 0.85  |  |  |  |

| D   | 70.50       | 71.50 |  |  |  |

| D1  | 82.00       | 83.00 |  |  |  |

| DS  | 81.50       | 82.50 |  |  |  |

| Ε   | 36.90       | 37.90 |  |  |  |

| E2  | 30.30       | 31.30 |  |  |  |

| Р   | 4.30        | 4.50  |  |  |  |

| P1  | 9.30        | 9.70  |  |  |  |

| P2  | 1.90        | 2.10  |  |  |  |

|     | PIN PI | NDITIE | Γ |     | PIN P  | ISITION |

|-----|--------|--------|---|-----|--------|---------|

| PIN | ×      | Y      | 1 | PIN | ×      | Y       |

| 1   | 8.30   | -11.55 | ] | 16  | -7.800 | 14.50   |

| 2   | 8.30   | -14.50 | 1 | 17  | 1.60   | 14.50   |

| 3   | 5.80   | -14.50 | ] | 18  | 4.10   | 14.50   |

| 4   | 3.30   | -14.50 | 1 | 19  | 6.60   | 14.50   |

| 5   | 0.80   | -14.50 | 1 | 20  | 9.10   | 14.50   |

| 6   | -1.70  | -14.50 | 1 | 21  | 13.60  | 4.40    |

| 7   | -11.05 | -11.55 | 1 | 22  | 13.60  | 1.45    |

| 8   | -11.05 | -14.50 |   | 23  | 23.80  | 1.80    |

| 9   | -26.50 | -14.50 | 1 | 24  | 26.50  | 2.05    |

| 10  | -26.50 | -11.55 |   | 25  | 23.80  | -0.70   |

| 11  | -26.50 | -6.05  | 1 | 26  | 26.50  | -0.95   |

| 12  | -26.50 | -3.05  | ] | 27  | 24.00  | -5.30   |

| 13  | -26.50 | 11.55  |   | 28  | 26.50  | -5.30   |

| 14  | -26.50 | 14.50  |   | 29  | 24.00  | -8.30   |

| 15  | -7.80  | 11.55  |   | 30  | 26.50  | -8.30   |

|     |        |        | _ |     |        |         |

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS 6 AND 61 APPLY TO THE PLATED TERMINALS AND ARE MEASURED AT DIMENSION A4.

- 4. POSITION OF THE CENTER OF THE TERMINALS IS DETERMINED FROM DATUM B THE CENTER OF DIMENSION D, X DIRECTION, AND FROM DATUM A, Y DIRECTION. POSITIONAL TOLERANCE, AS NOTED IN DRAWING, APPLIES TO EACH TERMINAL IN BOTH DI

- PACKAGE MARKING IS LOCATED AS SHOWN ON THE SIDE OPPOSITE THE PACKAGE ORIENTATION FEATURES.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code G = Pb-Free Package

AT = Assembly & Test Site Code YYWW = Year and Work Week Code

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON07115G               | Electronic versions are uncontrolled except when                                                      |

|------------------|---------------------------|-------------------------------------------------------------------------------------------------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                                                             |

| DESCRIPTION:     | PIM30 71X37.4 (PRESS FIT) | PAGE 1 OF 2                                                                                           |

| <b>DOCUMENT</b> | NUMBER: |

|-----------------|---------|

| 98AON07115      | G       |

PAGE 2 OF 2

| ISSUE | REVISION                                                                          | DATE        |

|-------|-----------------------------------------------------------------------------------|-------------|

| 0     | RELEASED FOR PRODUCTION. REQ. BY C. ENRIQUEZ.                                     | 04 DEC 2015 |

| Α     | MODIFIED TOP AND SIDE VIEWS AND CHANGED MARKING DIAGRAM. REQ. BY A. LAI.          | 26 FEB 2016 |

| В     | CHANGED DIMENSION TABLE CALLOUTS FROM MIN & NOM TO MIN & MAX. REQ. BY F. ESTRADA. | 01 FEB 2017 |

| С     | CHANGED Y POSITION FOR PIN 15. REQ. BY A. LAI.                                    | 09 MAY 2017 |

| D     | UPDATED MARKING DIAGRAM CODE INFORMATION. REQ. BY A. LAI.                         | 08 NOV 2017 |

| Е     | MODIFED VALUES A, A4, A5 & P2. REQ. BY A. ZHEN.                                   | 28 NOV 2017 |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

|       |                                                                                   |             |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

DATE 25 JUN 2018

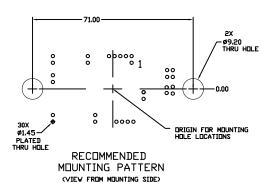

| MOUNTING | HOLE PO | OSITION | П  | MOUNTING | HOLE PO | OSITION |

|----------|---------|---------|----|----------|---------|---------|

| PIN      | Х       | Υ       | ١٢ | PIN      | Υ       |         |

| 1        | 8.30    | 11.55   | I  | 16       | -7.800  | -14.50  |

| 2        | 8.30    | 14.50   |    | 17       | 1.60    | -14.50  |

| 3        | 5.80    | 14.50   |    | 18       | 4.10    | -14.50  |

| 4        | 3.30    | 14.50   |    | 19       | 6.60    | -14.50  |

| 5        | 0.80    | 14.50   | Ι[ | 20       | 9.10    | -14.50  |

| 6        | -1.70   | 14.50   |    | 21       | 13.60   | -4.40   |

| 7        | -11.05  | 11.55   |    | 22       | 13.60   | -1.45   |

| 8        | -11.05  | 14.50   |    | 23       | 23.80   | -1.80   |

| 9        | -26.50  | 14.50   |    | 24       | 26.50   | -2.05   |

| 10       | -26.50  | 11.55   |    | 25       | 23.80   | 0.70    |

| 11       | -26.50  | 6.05    | I  | 26       | 26.50   | 0.95    |

| 12       | -26.50  | 3.05    | ١ſ | 27       | 24.00   | 5.30    |

| 13       | -26.50  | -11.55  |    | 28       | 26.50   | 5.30    |

| 14       | -26.50  | -14.50  |    | 29       | 24.00   | 8.30    |

| 15       | -7.80   | -11.55  |    | 30       | 26.50   | 8.30    |

|          |         |         | _  |          |         |         |

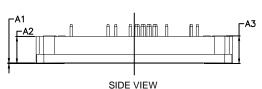

#### MILLIMETERS NOM. MAX. DIM 16.40 16.90 15.90 A1 0.30 0.60 10.90 11.40 11.90 A2 11.10 11.60 12.10 A3 0.90 1.00 1,10 b D 82.00 82.50 83.00 D1 70.50 71.00 71.50 26.50 REF D2 36.90 37.40 37.90 F E1 30.30 30.80 31.30 14.50 REF E2 4.30 4.50 F F1 9.5 REF 2.0 REF F2 5.5 REF F3

| _        |     | PIN POSITION |        |   |     | PIN POSITION |       |  |  |

|----------|-----|--------------|--------|---|-----|--------------|-------|--|--|

| _        | PIN | ×            | Y      | ı | PIN | х            | Y     |  |  |

| <b>⊥</b> | 1   | 8.30         | -11.55 | l | 16  | -7.800       | 14.50 |  |  |

| 의        | 2   | 8.30         | -14.50 | ı | 17  | 1.60         | 14.50 |  |  |

| Ц        | 3   | 5.80         | -14.50 | П | 18  | 4.10         | 14.50 |  |  |

| 2        | 4   | 3.30         | -14.50 | ı | 19  | 6.60         | 14.50 |  |  |

| 의        | 5   | 0.80         | -14.50 | ı | 20  | 9.10         | 14.50 |  |  |

| Ц.       | 6   | -1.70        | -14.50 | ı | 21  | 13.60        | 4.40  |  |  |

| 의        | 7   | -11.05       | -11.55 | ı | 22  | 13.60        | 1.45  |  |  |

| <u>□</u> | 8   | -11.05       | -14.50 | ı | 23  | 23.80        | 1.80  |  |  |

| ↲        | 9   | -26.50       | -14.50 | П | 24  | 26.50        | 2.05  |  |  |

| 0        | 10  | -26.50       | -11.55 | ı | 25  | 23.80        | -0.70 |  |  |

| Ч.       | 11  | -26.50       | -6.05  | ı | 26  | 26.50        | -0.95 |  |  |

| $\dashv$ | 12  | -26.50       | -3.05  | ı | 27  | 24.00        | -5.30 |  |  |

| $\dashv$ | 13  | -26.50       | 11.55  | ı | 28  | 26.50        | -5.30 |  |  |

| $\dashv$ | 14  | -26.50       | 14.50  |   | 29  | 24.00        | -8.30 |  |  |

| $\dashv$ | 15  | -7.80        | 11.55  |   | 30  | 26.50        | -8.30 |  |  |

|          |     |              |        |   |     |              |       |  |  |

| r <del>-</del>      | 71.0000           |                                       | <del></del>                        |

|---------------------|-------------------|---------------------------------------|------------------------------------|

|                     | o o               | ° 1                                   | 2X<br>#9.2000<br>THRU HOLE         |

|                     |                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 80 1                               |

| 30X<br>ø1.4500-     | 0                 |                                       | ORIGIN FOR MOUNTING HOLE LOCATIONS |

| PLATED<br>THRU HOLE | RECOM<br>MOUNTING | MENDED<br>PATTERN                     |                                    |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS 6 AND 61 APPLY TO THE PLATED TERMINALS AND ARE MEASURED AT DIMENSION A4.

- 4. POSITION OF THE CENTER OF THE TERMINALS IS DETERMINED FROM DATUM B THE CENTER OF DIMENSION D, X DIRECTION, AND FROM DATUM A, Y DIRECTION. POSITIONAL TOLERANCE, AS NOTED IN DRAWING, APPLIES TO EACH TERMINAL IN BOTH DIRECTIONS.

- PACKAGE MARKING IS LOCATED AS SHOWN ON THE SIDE OPPOSITE THE PACKAGE ORIENTATION FEATURES.

# GENERIC MARKING DIAGRAM\*

NOTE 4

> XXXXX = Specific Device Code G = Pb-Free Package

AT = Assembly & Test Site Code YYWW = Year and Work Week Code

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON86769G    | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | PIM30, 71x37.4 |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify a

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative