## REAL TIME CLOCK MODULE RTC-64611/64613 APPLICATION MANUAL

#### Characteristics

#### 1. Absolute maximum ratings

| lt                             | em        | Symbol              | Condition                             | Rated value                                                | Ųnit       |  |

|--------------------------------|-----------|---------------------|---------------------------------------|------------------------------------------------------------|------------|--|

| Supply                         | voltage * | V <sub>DD</sub>     | · · · · · · · · · · · · · · · · · · · | -0.5~+7.0                                                  | v          |  |

| Input voltage *                |           | V <sub>IN</sub>     |                                       | -0.5* *~V <sub>DD</sub> +0.3                               | V          |  |

| Allowable output current       |           | t lo t              | 5                                     |                                                            | mA         |  |

| Total allowable output current |           | t Σt <sub>o</sub> i |                                       | 50                                                         | mA         |  |

| Storage                        | RTC-64611 |                     | 01                                    | - 55~ + 85                                                 |            |  |

| temperature                    | RTC-64613 |                     | $V_{DD} = 0V$                         | -55~+125                                                   | °C         |  |

| Soldering conditions           |           |                     | RTC-64611 (Lead part)                 | Temperature: 260°C or less Time                            | a: 10 sec. |  |

|                                |           | T <sub>sol</sub>    | RTC-64613                             | Under 260°C within 10sec×2 or<br>under 230°C within 3 min. |            |  |

\*Allowable value for GND. \* \* -0.3V for 50ns pulse width

#### 2. Operating range

| ltem                  | Symbol          | Condition                    | Range      | Unit |

|-----------------------|-----------------|------------------------------|------------|------|

| Supply voltage        | V <sub>DD</sub> | $Ta = -20 \sim +75^{\circ}C$ | 4.5~5.5    | v    |

| Operating temperature | TOPR            | $V_{pp} = 4.5 \sim 5.5 V$    | - 20~ + 75 | ⊃°   |

#### 3. Frequency characteristics

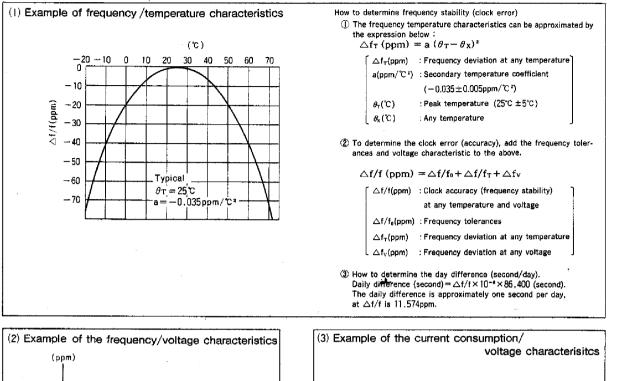

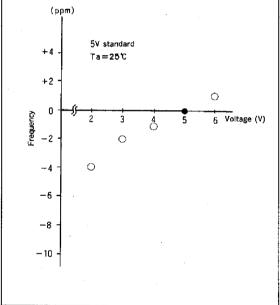

..... ltem Condition Range Unit RTC-64611A +15/- 5 (5±10) RTC-64611B +55/-45 (5±50) Ta=25°C PPM Frequency tolerance  $V_{DD} = 5V$ +25/-15 (5±20) RTC-64613A +55/-45 (5±50) RTC-64613 +10/-120 -10~+70°C (Standard at 25°C) Temperature characteristics PPM +10/-220  $-20 \sim +75^{\circ}$ C (Standard at 25°C) Ta=25°C,  $V_{pp}$ =5V first year ± 5 PPM/year Aging PPM/V Ta=25℃, V<sub>DD</sub>=4.5~5.5V ± 5 Voltage characteristics

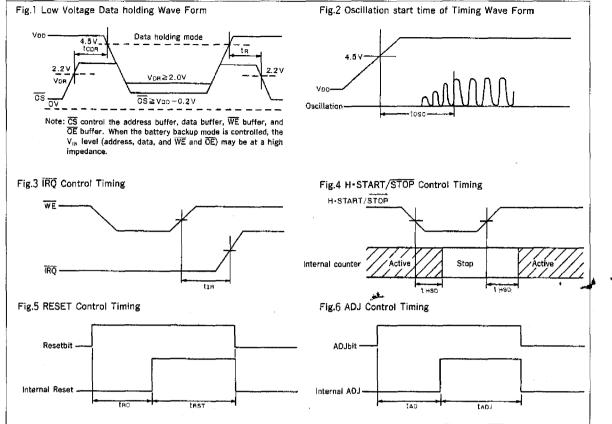

#### 4. Data holding characteristics at low supply voltages

| Item                             | Symbol Condition |                                                                                 | MIN                   | TYP | MAX | Unit |  |

|----------------------------------|------------------|---------------------------------------------------------------------------------|-----------------------|-----|-----|------|--|

| Data holding voltage             | V <sub>DR</sub>  | $\overline{CS} \ge V_{DD} - 0.2V$                                               | 2.0                   | _   | 4.5 | ٧    |  |

| Data holding current consumption | LUDR             | V <sub>DD</sub> =2.0, CS≥1.8V<br>H.START/STOP≥1.8V<br>IRQ with 1 MHz kept open. | _                     |     | 2.0 | μA   |  |

| Chip select data hold time       | TCDR             |                                                                                 | 0                     |     | —   | ПS   |  |

| Operation recovery time          | TR               | See Fig. 1.                                                                     | 85 (t <sub>RC</sub> ) |     | _   | ns   |  |

Note: t<sub>RC</sub>······Read cycle time

#### 5. Oscillation characteristics and control signal timing.

| , item                          | Symbol | Condition   | MIN | ТҮР | MAX | Unit   | ]        |

|---------------------------------|--------|-------------|-----|-----|-----|--------|----------|

| Crystal oscillation start time  | Tosc   | See Fig. 2. |     | —   | 3.0 | sec    | (Note 1) |

| IRQ release time                | TIN    | See Fig. 3. | . — |     | 2.0 | μsec   |          |

| H.START/STOP control delay time | TILSD  | See Fig. 4. | _   |     | 185 | µr sec | ]        |

Note 1: Oscillation start is defined as  $Ta = -20 \sim +75^{\circ}C$  at the applied voltage of  $V_{pp} = 5V \pm 10\%$ .

The oscillation start time at  $V_{\rm DD}$  = 4.5V or less cannot be specified.

Start at temperature:  $Ta \approx -20 \sim +75^{\circ}C$ .

•

| item             | Symbol           | Condition   | MIN | TYP | MAX | Unit  |

|------------------|------------------|-------------|-----|-----|-----|-------|

| Reset delay time | T <sub>RD</sub>  | Pag Ein E   |     | _   | 125 | μsec  |

| Reset time       | T <sub>RST</sub> | See Fig. 5. |     | 122 | 125 | μsec  |

| ADJ delay time   | T <sub>AD</sub>  | 0 E' E      |     | —   | 125 | µ sec |

| ADJ time         | TAD              | See Fig. 6. |     | 122 | 125 | µsec  |

Note 2: When Reset and ADJ have been set, set the next Reset and ADJ after operation is finished. Both Reset and ADJ may be set simultaneously.

#### 6. DC characteristics

| <b>1 b c c c</b>                              | o                                      |                         | V <sub>D0</sub> = 51 | ∕±10%           | V <sub>DD</sub> =    | 2V              | 1 4 74 |

|-----------------------------------------------|----------------------------------------|-------------------------|----------------------|-----------------|----------------------|-----------------|--------|

| ltem                                          | Symbol                                 | Measuring conditions    | MIN                  | MAX             | MIN                  | MAX             | Unit   |

| High level input voltage                      | gh level input voltage V <sub>IN</sub> |                         | 2.2                  | V <sub>DD</sub> | V <sub>DD</sub> -0.2 | ۷ <sub>bb</sub> | ۷      |

| Low level input voltage                       | Vil                                    |                         | -0.3                 | 0.8             | -0.3                 | 0.2             | v      |

| Input leak current                            | I <sub>IN</sub>                        |                         | _                    | <b>±</b> 2      |                      | ± 2             | μA     |

| Three-state leak current                      | I <sub>TSL</sub>                       |                         |                      | ±10             | —                    | ±10             | μA     |

| Output leak current                           | ILOH                                   |                         |                      | ±10             |                      | ±10             | Aپ     |

| High level output voltage<br>(excl. 1Hz, IRQ) | V <sub>on</sub>                        | $I_{on} = -1mA$         | 2.4                  | —               | _                    | _               | v      |

| Low level output voltage                      | V <sub>ot.</sub>                       | I <sub>OL</sub> = 2.1mA |                      | 0.4             |                      |                 | v      |

| Input capacity                                | C <sub>IN</sub>                        | $V_{\rm IN} = 0V$       |                      | 12.5            | —                    | —               | pF     |

| Output capacity                               | CONT                                   | Ta = 25°C<br>f = 1.0MHz |                      | 12.5            | —                    |                 | pF     |

| Current consumption (at bus access) Ipp No Ic |                                        | No load, min, cycle     |                      | 2.0             |                      |                 | mA     |

团 007

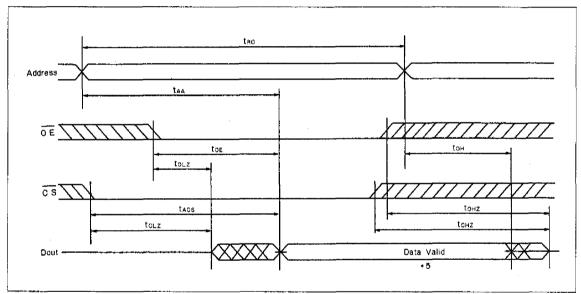

#### 7. AC characteristics (Unless otherwise specified,)

(I) AC characteristics measuring conditions (applicable to the read and write cycles)

- ① Input pulse level: 0.8-2.4V

- ② Input rise/fall time: 5 ns

- ③ I/O timing reference level: 1.5V

- ( Output load: 1 TTL gate +  $C_L$  (100pF)

- (including the scope and jig capacity)

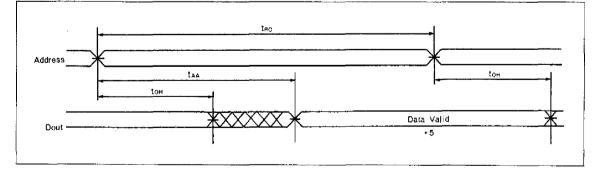

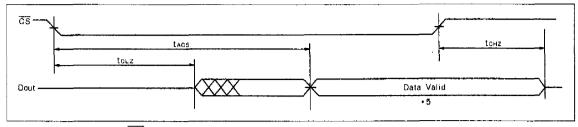

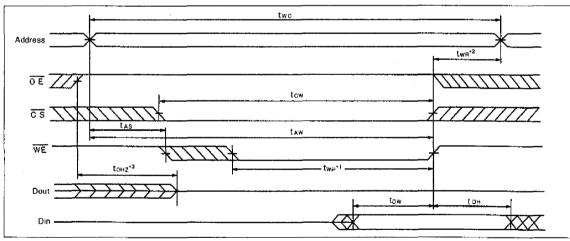

#### (2) Read cycle

| Read cycle                     | Symbol           | MIN | MAX | Unit |

|--------------------------------|------------------|-----|-----|------|

| Read cycle time                | t <sub>RC</sub>  | 85  | _   | ns   |

| Address access time            | t <sub>AA</sub>  | -   | 85  | лѕ   |

| Chip select access time        | t <sub>ACS</sub> | _   | 45  | ns   |

| Output enable access time      | t <sub>oe</sub>  |     | 45  | ns   |

| Output hold time               | t <sub>on</sub>  | 10  | _   | ns   |

| Chip select/output set time    | t <sub>cLZ</sub> | 10  |     | ns   |

| Output enable /output set time | toLz             | 5   | —   | ns   |

| Chip deselect/output floating  | t <sub>cHZ</sub> | 0   | 35  | ns   |

| Output disable/output floating | tonz             | 0   | 35  | ns * |

Note: The bus cannot be accessed in Battery Backup mode.

#### ① Read cycle-1 timing wave form \*1

② Read cycle-2 timing wave form \*1. \*2, and \*4

۰.

③ Read cycle-3 timing wave form \*1, and \*4

\* 1. In read cycle, keep WE "High".

\* 2. The device is always selected in  $\overline{\text{CS}} = V_{\mathrm{fL}}.$

\* 3. The address must be defined simultaneously with or before activation of CS.

\* 4.  $\overline{OE} = V_{1L}$

\* 5. During read, read data varies as the contents of the register change.

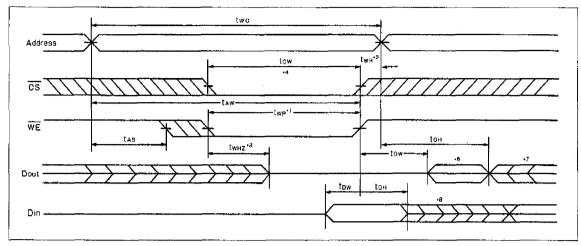

#### (3) Write cycle

| Item                           | Symbol            | MIN        | MAX      | Unit         |

|--------------------------------|-------------------|------------|----------|--------------|

| Write cycle time               | t <sub>wc</sub>   | 85         |          | ns           |

| Chip select time               | · t <sub>cw</sub> | <b>3</b> 5 | —        | ns           |

| Address valid time             | t <sub>AW</sub>   | 75         |          | . л <b>s</b> |

| Address setup time             | t <sub>AS</sub>   | 0          | _        | រាទ          |

| Write pulse time               | t <sub>wP</sub>   | 60         | _        | ns           |

| Address holding time           | t <sub>wn</sub>   | 10         |          | ns           |

| WE output floating             | t <sub>wnz</sub>  | 0          | 35       | ns           |

| Input date set time            | t <sub>DW</sub>   | 40         | <b>—</b> | ns           |

| Input date hold time           | t <sub>DH</sub>   | 0          |          | ns           |

| Output disable/output floating | t <sub>okz</sub>  | 0          | 35       | ns           |

| WE output set time             | tow               | 5          |          | ns           |

Note: During battery backup, the bus cannot be accessed.

#### ① Write cycle 1 timing wave from (when the $\overline{OE}$ clock is used)

\* 1. Write is executed while  $\overline{CS}$  = "Low" overlaps with  $\overline{WE}$  = "Low" (t<sub>wp</sub>).

\* 2. The twice is measured from the "High" transition of CS or WE, whichever is earlier, to the end of the write cycle.

\* 3. During this period, the I/O terminal is in the the output state. Do not apply an input signal with opposite phase to the output.

- 6 -

团 009

② Write cycle 2 timing wave form (when  $\overline{OE} = GND$  is fixed)

- \* 1. Write is executed while  $\overline{CS}$  = "Low" is overlapped with  $\overline{WE}$  = "Low" (t<sub>wP</sub>).

- \* 2. The twe is measured from the "High" transition of CS or WE, whichever is earlier, to the end of the write cycle.

- \* 3. During this period, the I/O terminal is in the output state. Do not apply an input signal with opposite phase to the output.

- \* 4. When the "Low" transition of  $\overline{\text{CS}}$  occurs simultaneously with the "Low" transition of  $\overline{\text{WE}}$  or after the  $\overline{\text{WE}}$  transition, output is kept at high impedance.

- \* 5. OE is always"Low."

- \* 6. Dout is in the same phase as data to be written in this write cycle.

- \* 7. Dout is the data to be read for the next address.

- \* 8. During this period, the I/O terminal goes to the output state when CS is "Low." At this point, do not apply an input signal with opposite phase to the output.

#### Register

#### 1. Register table

|   | A <sub>3</sub> | A <sub>2</sub> | Α, | Ao | b <sub>7</sub><br>(I/O <sub>8</sub> ) | b <sub>6</sub><br>(I/O <sub>7</sub> ) | b <sub>5</sub><br>(I/O <sub>6</sub> ) | b4<br>(1/05)       | b₃<br>(I/O₄)      | b <sub>2</sub><br>(1/O <sub>3</sub> ) | b <sub>1</sub><br>(I/O <sub>2</sub> ) | ь₀<br>(I/O₁)      | Register name             |  |

|---|----------------|----------------|----|----|---------------------------------------|---------------------------------------|---------------------------------------|--------------------|-------------------|---------------------------------------|---------------------------------------|-------------------|---------------------------|--|

| 0 | 0              | 0              | 0  | 0  | *                                     | 1Hz                                   | 2Hz                                   | 4Hz                | 8Hz               | 16Hz                                  | 32Hz                                  | 64Hz              | 64Hz Counter              |  |

| 1 | 0              | 0              | 0  | 1  | *                                     | C-S40                                 | C-S <sub>20</sub>                     | C-S10              | C-Sg              | C-54                                  | C-\$2                                 | C-\$1             | Second digit counter      |  |

| 2 | 0              | 0              | 1  | 0  | *                                     | c-mi₄₀                                | c-mi <sub>20</sub>                    | c-mi <sub>10</sub> | c-mi <sub>s</sub> | c-mi₄                                 | c-mi2                                 | c-mi,             | Minute digit counter      |  |

| 3 | 0              | 0              | 1  | 1  | *                                     | *                                     | ç-h <sub>że</sub>                     | c-h10              | c-h <sub>s</sub>  | c-h₄                                  | c-h <sub>2</sub>                      | c-hı              | Hour digit counter        |  |

| 4 | 0              | 1              | 0  | 0  | *                                     | *                                     | *                                     | *                  | *                 | C-₩₄                                  | C-W2                                  | C-W1              | Day of week digit counter |  |

| 5 | 0              | 1              | 0  | 1  | *                                     | *                                     | c-d <sub>zo</sub>                     | c-d10              | c-d <sub>≇</sub>  | c-d4                                  | c-d <sub>2</sub>                      | c-dı              | Day digit counter         |  |

| 6 | 0              | 1              | 1  | 0  | *                                     | *                                     | *                                     | C-m010             | c-mo <sub>s</sub> | c∙mo₄                                 | c-mo <sub>2</sub>                     | c-mo.             | Month digit counter       |  |

| 7 | 0              | 1              | 1  | 1  | с-у <sub>80</sub>                     | C-Y40                                 | C-Y20                                 | C-y10              | C-y <sub>8</sub>  | C-y₄                                  | c-y <sub>2</sub>                      | с-у,              | Year digit counter        |  |

| 8 | 1              | 0              | 0  | 0  | ENB                                   | 1 Hz                                  | 2Hz                                   | 4Hz                | 8Hz               | 16Hz                                  | 32Hz                                  | 64Hz              | 64Hz alarm                |  |

| 9 | 1              | 0              | 0  | 1  | ENB                                   | a-s <sub>40</sub>                     | a-s20                                 | a-\$10             | a-s,              | a-s4                                  | a-s2                                  | a-s <sub>1</sub>  | Second digit alarm        |  |

| A | 1              | 0              | T  | 0  | ENB                                   | a-mi40                                | a-mi <sub>20</sub>                    | a-mi <sub>10</sub> | a-mie             | a-mi₊                                 | a∙mi₂                                 | a-mi <sub>t</sub> | Minute digit alarm        |  |

| В | 1              | 0              | 1  | 1  | ENB                                   | *                                     | a-h <sub>20</sub>                     | a-h <sub>10</sub>  | a-h <sub>s</sub>  | a-h,                                  | a-h <sub>2</sub>                      | a-h1              | Hour digit alarm          |  |

| С | 1              | 1              | 0  | 0  | ENB                                   | *                                     | *                                     | *                  | *                 | a-w₄                                  | a-w2                                  | a-w <sub>1</sub>  | Day of week digit alarm   |  |

| D | 1              | 1              | 0  | 1  | ENB                                   | . *                                   | a-d <sub>20</sub>                     | a-d <sub>10</sub>  | a-da              | a-d₄                                  | a-d <sub>2</sub>                      | a-d1              | Day digit alarm           |  |

| E | 1              | 1              | 1  | 0  | CF                                    | *                                     | *                                     | CIE                | AIE               | *                                     | *                                     | AF                | Control register A 🛹      |  |

| F | 1              | 1              | 1  | 1  | RAM7                                  | RAM6                                  | RAM5                                  | RAM4               | TEST              | 30sec<br>ADJ                          | RESET                                 | S-START<br>/STOP  | Control register B        |  |

2. Note the following:

(1) In positive logic, "H" of the data bus corresponds to "I" in the register.

•

(2) Do not set date out of the clock, otherwise, a counting error may occur.

(3) When the power is turned on (before initializing) the state of the bits is undefined. Write the registers to set the values.

#### 3. Function of the register bits

| Bit name                        |                                                                                                                                                                                                                                                                                       |                | Fun        | ctions       |             |              |            |            |            |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|--------------|-------------|--------------|------------|------------|------------|--|--|

| * Mark                          | Not used and invalid for write. In                                                                                                                                                                                                                                                    | the read mod   | le, data e | quals "O".   |             |              |            |            |            |  |  |

| 64Hz counter                    | Read-dedicated bit (inavlid for writ                                                                                                                                                                                                                                                  | te). Date is n | ead in bin | ary code.    |             |              |            |            |            |  |  |

| 64Hz alarm                      | Data appears in binary code.                                                                                                                                                                                                                                                          |                |            |              |             |              |            |            |            |  |  |

| Second digit-year digit         | BCD code                                                                                                                                                                                                                                                                              |                |            |              |             |              |            |            |            |  |  |

| Ten o'clock digit               | Only for the 24-hour system.                                                                                                                                                                                                                                                          |                |            |              |             |              |            |            |            |  |  |

| Dau af waals diait              | Encode the days Example:                                                                                                                                                                                                                                                              | Data           | 0          | 1            | 2           | 3            | 4          | 5          | 6          |  |  |

| Day of week digit               | of the week.                                                                                                                                                                                                                                                                          | Day of week    | Sunday     | Monday       | Tuesday     | Wednesday    | Thursday   | Friday     | Saturday   |  |  |

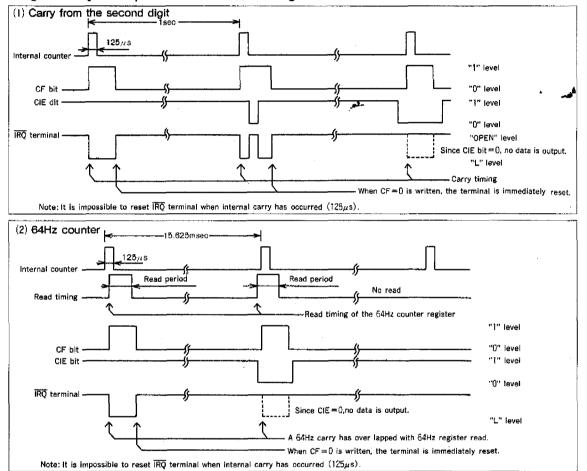

| CF (Carry Flag)                 | Mainly used to read the time. This bit is set to "1" in any of the following conditions:<br>(1) A carry of the second digit has occurred.<br>(2) A 64Hz carry and 64Hz register read overlap.<br>In any condition other than the aboves, the bit can be cleared by writing $CF = 0$ . |                |            |              |             |              |            |            |            |  |  |

| CIE<br>(Carry Interrupt Enable) | When this bit is set to "1", CF bit=1 and $\overline{IRQ}$ terminal=L when the carry conditions are met. When CF=0 is written, $\overline{IRQ}$ terminal=OPEN (cleared). When this bit is set to "0", $\overline{IRQ}$ terminal remains open regardless of the value of the CF bit.   |                |            |              |             |              |            |            |            |  |  |

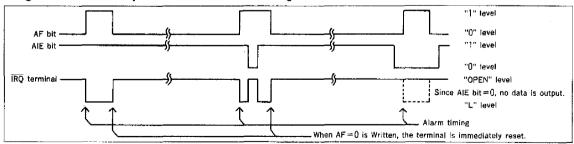

| AIE<br>(Alarm Interrupt Enable) | When this bit is set to "1", AF bit =<br>IRQ terminal = OPEN (cleared). Wh<br>CF bit.                                                                                                                                                                                                 |                |            |              |             |              |            |            |            |  |  |

| AF (Alarm Flag)                 | When the time and calendar match cleared by writing $AF=0$ .                                                                                                                                                                                                                          | the set alar   | m time, t  | nis bit is s | iet to "1". | . In any of  | ther condi | tion, this | bit can be |  |  |

| RAM7 to 4                       | May be used as RAM or flag.                                                                                                                                                                                                                                                           |                |            |              |             |              |            |            |            |  |  |

| TEST                            | This bit is used by us to test the :                                                                                                                                                                                                                                                  | system. The i  | user must  | set this b   | it to () (T | EST=0).      |            |            |            |  |  |

| ADJ                             | In ADJ=1, a 30-second correction                                                                                                                                                                                                                                                      | is executed.   | Simultane  | ously, the   | dividing    | circuit is r | eset.      |            |            |  |  |

| RESET                           | in RESET = 1, the dividing circuit (                                                                                                                                                                                                                                                  | less than 1 s  | econd cou  | nter) is re  | set.        |              |            |            |            |  |  |

| S-START/STOP                    | This bit is used in combination with<br>STOP bit=0, counting stops. Othe<br>START/STOP terminal to GND ("L                                                                                                                                                                            | rwise, the tin |            | •            |             |              |            |            |            |  |  |

团 011

۰.

(The flag is rset)

## **EPSON**

OPEN (Unchanged)

#### 4. Setting the carry interrupt mode

0

| CIE (Carry Interrupt Enable)                             | Condition                                            | CF (Carry Flag)        | <b>IRQ</b> terminal |  |

|----------------------------------------------------------|------------------------------------------------------|------------------------|---------------------|--|

| 1                                                        | A carry has occurred from the second digit, or a 64  | 0→1                    | OPEN→L              |  |

| 0                                                        | Hz carry and a 64Hz register read overlap.           | (The flag is set)      | OPEN (Remains)      |  |

| 1                                                        | No carry has occurred from the second digit, or a 64 | AF=0 is written.       | L→OPEN              |  |

| 0                                                        | Hz carry and a 64Hz register read do not overlap.    | (The flag is reset)    | OPEN (Unchanged)    |  |

|                                                          |                                                      |                        |                     |  |

| tting the alarm interru                                  |                                                      | ·····                  |                     |  |

| etting the alarm interru<br>AIE (Carry Interrupt Enable) |                                                      | AF (Alarm Flag)        | IRQ terminal        |  |

|                                                          | Condition                                            | AF (Alarm Flag)<br>0→1 |                     |  |

|                                                          |                                                      |                        | IRQ terminal        |  |

#### 6. Setting the carry interrupt mode and its reset timing

calendar.

7. Setting the alarm interrupt mode and its reset timing

.

#### Register explanation

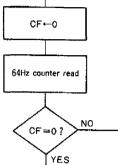

#### 1. 64Hz counter

- (1) The 64Hz counter can read a value of 64 1 Hz (data in binary code ) of the dividing circuit (read only).

- (2) When a carry from the 128 Hz stage (internal counter) and read of this register are overlapped, CF (b7 of the control register A) is set to "1" In this case, read this register again according to the procedure shown in the flowchart below. (A carry takes place once every approximately 8 ms in the 125 μs period.)

- (3) This register is reset using RESET or 30-second ADJ.

# 64Hz count

2. Second - year counters

Exa

- (1) These registers set and count the time and calendar. (2) Each register is in BCD code.

- Example:  $(*, S_{40}, S_{20}, S_{10}, S_3, S_4, S_2, S_1) = (0, 1, 0, 1, 1, 0, 0, 1) \rightarrow 59$  seconds (3) Encode the days of the week for use.

| ample: | data        | 0    | 1    | 2    | 3    | 4    | 5    | 6    |  |

|--------|-------------|------|------|------|------|------|------|------|--|

|        | Day of week | Sun. | Mon. | Tue. | Wed. | Thur | Fri. | Sat. |  |

(4) The time register uses the 24-hour system. The year register uses the western calendar. Leap years are automatically recognized. (Note: A year whose lower two digits are a multiple of four is recognized as a leap year.)

#### (5) A carry is generated once each second in the 125 $\mu s$ period.

- Data read during a carry operation (during CF=1) is not guaranteed. (See the time read procedure on page 14.)

- (6) The second and minute registers are not affected by RESET.

- (7) The hour year registers are not affected by ADJ and RESET.

#### 3. 64Hz and second - year alarm registers

- (1) These registers set the alarm time (the data code is 64Hz; see section "second year registers).

- (2) When the alarm register with its ENB set to "1" matches the counter,AF is set to "1"

- When CIE bit (control register A-b3) has been set to "1", IRQ terminal is set to "Low "level.

#### 4. Control register A

| 1 | <b>b</b> <sub>7</sub> | $\mathbf{b}_6$ | b <sub>5</sub> | <b>b</b> <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | <b>b</b> <sub>1</sub> | b <sub>o</sub> |

|---|-----------------------|----------------|----------------|-----------------------|----------------|----------------|-----------------------|----------------|

|   | CF                    | *              | *              | CIE                   | AIE            | *              | *                     | AF             |

① This register processes flags which come in ansynchronously from the clock circuit.

#### ② Note the following:

Do not use the Set Bit and Clear Bit instructions to "read-modify-write" because a flag may be set after read.

(1) CF (Carry Flag) (b7)

$\bigcirc$  Fiag occurrence

- This bit is set to "1" in hardware when one of the following conditions is met:

- \* When a carry from the second digit has occurred.

\* When a 64Hz carry overlaps with read access to the 64Hz register (see section "64Hz register/counter).

| Carry flag | Function                                                                                                   |

|------------|------------------------------------------------------------------------------------------------------------|

| 0          | After this bit is reset to "0", there was no read at the time of the second digit carry and the 64Hz carry |

| 1          | After this bit is reset to "0", there was a read at the time of the second digit carry or the 64Hz carry   |

② Resetting

Resetting can be accomplished by writing "0"to the CF bit during any period except the carry period. ③ Note the following:

This bit will not accept a write of "1."

(1) CIE (Carry Interrupt Enable ) (b4)

① When this bit is set to "1", the CF is set when the carry condition is met, and the IRQ terminal goes "low". When CF is reset the IRQ terminal returns to the "High"level.

#### 2 Relation between CIE/CF bits and IRQ terminal.

| CIE | CF                                  | IRQ terminal *    | Remarks                                                                                               |

|-----|-------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|

| 1   | $0 \rightarrow 1$ (The flag is set) | High→Low          |                                                                                                       |

| 1   | 1→0 (The flag is reset)             | Low→High          | When the flag is set, IRQ terminal goes "Low".<br>When the flag is reset, IRQ terminal is also reset. |

| 0   | 0 or 1                              | High (No changes) |                                                                                                       |

\* IRQ terminal has an open drain output. Therefore, it must be forced up.

(3) AIE (Alarm Interrupt Enable) (b<sub>3</sub>).

① When this bit is set to "1", the AF is set when the alarm condition is met and the IRQ terminal goes "Low". When the AF is reset, the IRQ terminal returns to the "High" level.

2 Relation between the AIE/AF bits and the IRQ terminal.

| AIE | AF                                     | IRO terminal      | Remarks                                                                                               |

|-----|----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|

| 1   | 0→1 (The flag is set)                  | Hight→Low         |                                                                                                       |

| 1 . | $1 { ightarrow} 0$ (The flag is reset) | Low→High          | When the flag is set, IRQ terminal goes "Low".<br>When the flag is reset, IRO terminal is also reset. |

| 0   | 0 or 1                                 | High (No changes) |                                                                                                       |

(4) AF (Alarm Flag) (b<sub>o</sub>).

① Flag occurrence

This bit set to "1" in hardware when one of the following condition is met: When the set time of the alarm register (only the register with ENB="1") matches the time and calendar of the counter register.

| AF | Function-                                                                               |  |  |  |

|----|-----------------------------------------------------------------------------------------|--|--|--|

| 0  | After the bit is reset to "O", the alarm register does not match the clock and counter. |  |  |  |

| 1  | The alarm register matches the clock and counter (only for the register with ENB set).  |  |  |  |

② Resetting

Reset can be conducted by writing "0" to the AF bit during any period except the alarm time.

③ Note the following:

This bit will not accept write of "1".

#### 5. Control register B

| <b>b</b> <sub>7</sub> | b <sub>6</sub> | b <sub>s</sub>   | b₄   | b <sub>3</sub> | b <sub>2</sub> | b,    | bo               |

|-----------------------|----------------|------------------|------|----------------|----------------|-------|------------------|

| RAM <sub>7</sub>      | RAM₅           | RAM <sub>6</sub> | RAM, | TEST           | ADJ            | Reset | S+START<br>/STOP |

Note: User functions in the state TEST="1" are not guaranteed. Use the system in the state TEST="0".

(I) RAM 7, 6, 5, 4 (b7, 6, 5, 4).

The bit can be used as RAM or flags by writting "1" or "0".

They cannot be used as RAM if TEST = "1".

(2) TEST (b<sub>3</sub>)

This bit is used by us to test the system. Use the system with TEST set to "0".

If TEST = "1", user functions are not guaranteed.

(3) 30-second ADJ (30-second ADJUST) (b<sub>2</sub>)

When this bit is set to "1", the 30-second correction is executed. At this time, 64Hz counter (dividing circuit) is also reset.

\* Before 30 seconds, this bit has "00" seconds without a carry of the minute digit.

\*After 30 seconds, this bit has "00" second with a carry of the minute digit.

② Reset

"1" is held for 250 µs after this bit is set to "1". This bit then automatically returns to "0".

| ADJ bit      | 4                | 250µs MAX.                   |  |

|--------------|------------------|------------------------------|--|

| Internal ADJ | t ad= 125µs MAX. | t <sub>ADJ</sub> =125µs MAX. |  |

سلحق

## RTC-64611/64613

③ Note the following:

Conduct the next writing, only after this bit returns to"0" (is reset),

Writing"0" to this bit is invalid.

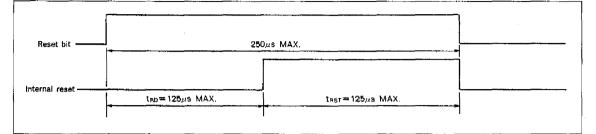

(4) RESET (b1)

$\odot$  When this bit is set to"1", only the dividing circuit is initialized.

2 Reset

"" is held for 250 $\mu$ s after this bit is set to"1". The bit then automatically returns to"0".

③ Note the following:

Conduct the next writing, only after this bit returns to"0" (is reset), Writing"0" to this bit is invalid.

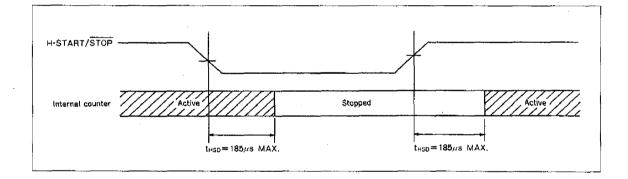

(5) S+START/STOP (Software START/STOP) (b<sub>0</sub>).

Use this function in combination with the H.START/STOP terminal.

| H·START/STOP terminal | H·START/STOP bit | Clock state |  |

|-----------------------|------------------|-------------|--|

| L                     | 0                | Stopped     |  |

| L                     | 1                | Active      |  |

| Н                     | 0                | Active      |  |

| н                     | 1                | Active      |  |

Ø015

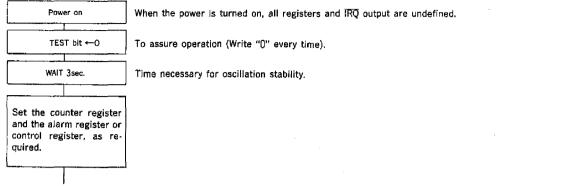

#### Operation procedure

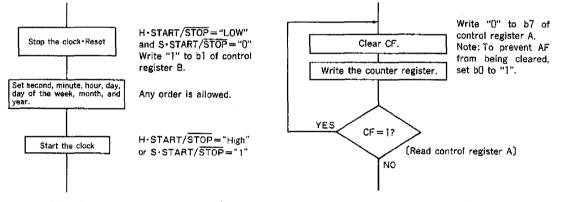

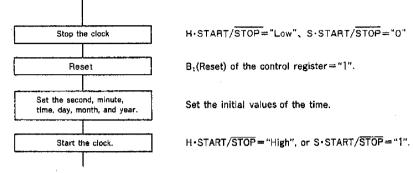

#### 1. Initialization when power on.

Initialization is needed only when the power is initially turned on. To return from battery backup mode, follow the specifications for low supply voltage data hold wave form.

Note: This module has no terminal for resetting registers.

.

Therefore, after the power is turned on, all registers must reinitialized. Before initialization of the registers is completed, follow the instructions below:

(I) Undefined IRQ

As all registers are undefined when the power is turn on, the interruption a carry or alarm may occur. This may cause an interrupt from a carry or may cause an alarm to occur. In the system software, to prevent such error, do not accept any interrupts before all registers are completely initialized.

(2) Undefined calender clock operation

When the power is turned on, the TEST bit is undefined. With this bit="1" the system operates in test mode, then begins normal operation. Set this to"0" before using the clock function.

(3) Undefined countar START/STOP

When the power is turned on, the S.START/STOP bit is undefined.

Starting and stopping of the counter is controlled by the OR logic of this bit and the external terminal H.START/STOP. Set this bit in accordance with the control method.

#### 2. Time setting procedure

(1) To reset the dividing circuit and then set the counter (2) To set the second - year counter

Section (1) indicates the method of stopping the clock and setting the time. This method is effective when the entire calendar clock is exchanged. With this method, programming is easy.

Section (2) indicates the method for setting the time while keeping the clock operating. The method is effective when a part of the calendar clock is exchanged (for example, only data on the second or time is exchanged). The carry flag is used to check the write state. When a carry is generated during write, the written data is automatically updated and an error occurs in the set data. Therefore, when the carry flag has been set to"1", rewriting must be done. The interrupt function can be used to check the carry flag.

Note: A carry of second to year digits is executed once per second in the 125µs period, Therefore, when a carry is detected in write operation, the writing can be done after 125µs from the carry starts. The write must be completed before the next carry starts.

-13 -

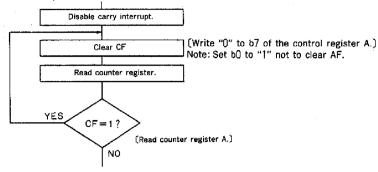

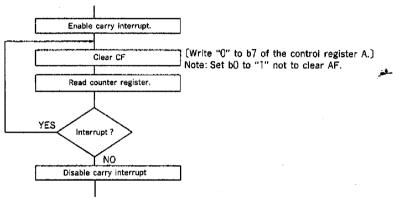

#### 3. Time reading procedure

(1) Interrupt is not used

#### (2) Interrupt is used.

۰.

When a carry occurs during time read, the correct time is unavailabl. In this case, the read must be repeated. The method in (1) does not use an interrupt. The method in (2) uses an interrupt (IRQ terminal). To simplify the program, the method in (1) is generally used.

- Note: 1). The second year digit carry is executed once per second during the 125µs period. When a carry is detected in the read operation, the reading can be done after 125µs from carrystart. Now a normal read is achieved. The read must be completed before the new carry starts.

- 2). The 64Hz counter is carried once each approximately 8 msec, in the 125µs period

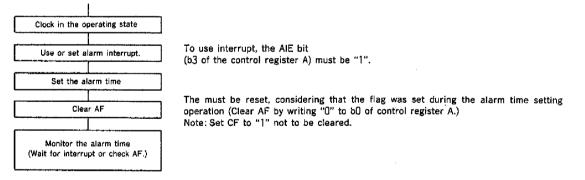

#### 4. Alarm function

The alarm can be generated for any of the 64Hz, second, minute, hour, day of the week, or in any combination of them. For the register to which you want to generate alarm, write "1" to ENB bit of b7 and set the alarm time in the low-order bits. For other registers, write"0" to ENB bit of b7.

When the clock matches the alarm time, the AF bit (b0 of the control register A) is set to"1". Alarm detection may be recognized by reading this bit, however, an interrupt is commonly used. When AIF (b3 of the control register A) has been set to"1", the IRQ terminal goes"Low" when an alarm occurs. Thus, an alarm can be detected.

AF is always set when time register and alarm register match. That is, when the AF bit is reset by writing "0", AF is immediately set again after write. The programmer must be aware of this point.

#### 5. Application as a long term timer

This module contains the counter start/stop function. This function enables the module to be used as a long-term timer. In this application, the timer uses the normal calendar clock function.

This requires setting of the month and year, even if they are not required. For example, When the timer is used with the month setting undefined, the month may end on any day from 28th to 31st. The timer will not indicate when the next month starts.

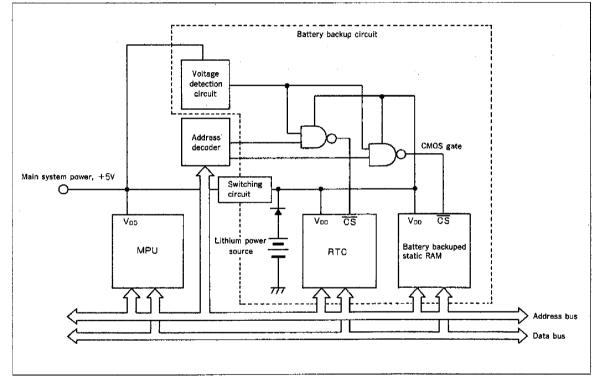

#### System configuration sample

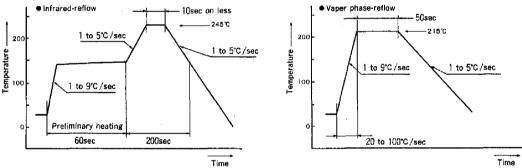

#### Reference data

(µA)

2.5

Ta=25℃ consumption (lop) 2.0 0 O 1.5 Ο 0 Current -1.0-O0.5 ۵ ·(v) ż ż 4 5 6 Voltage ( $V_{\rm DD}$ )

— 16 —

EPSON

Ø 020

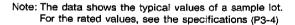

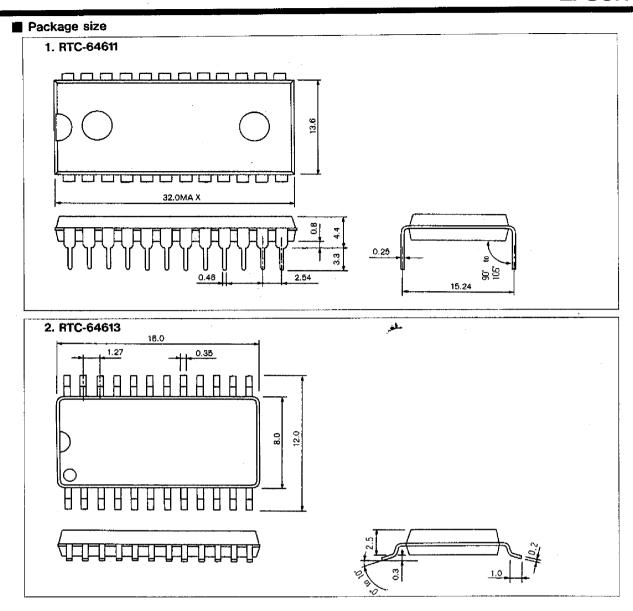

#### Marking layout

٠

#### Precautions

- (1) This module uses a C-MOS IC for low power consumption. This following precautions must be taken to ensure that it is not damaged.

- ① Static electricity

This unit have circuits to protect it from damage caused by static electricity, but exposure to excessive static electricity could damage the IC. Please use conductive packaging or shipping containers. Also, please use grounded soldering irons, measuring circuits, etc. that do not leak.

Noise

Exposing the power source or input/output terminals to excessive noise could cause malfunctioning or a latch up phenomenon. To ensure stable operation, please attach a by pass capacitor (recommend ceramic type) of at least 0.1  $\mu$ F as close as possible to the module's power-source terminal (between V<sub>DD</sub>-GND). Please do not place the module near anything that emits high nois.

③ Voltage level of input terminals

Please make the input terminal voltage level setting as close to the V<sub>DD</sub>-GND potential as possible, since a mid-level potential setting will cause an increase in current consumption, a decrease in the noise margin, and a deterioration of devices.

④ Unused input terminals (with exception of (NC) terminal)

Because the input impedance of input terminals is extremely high, use in the open state may cause malfunctioning due to unset potential or noise. Therefore, unused input terminals should be either pulled up or down. Further, the NC terminal should be grounded in order to avoid noise.

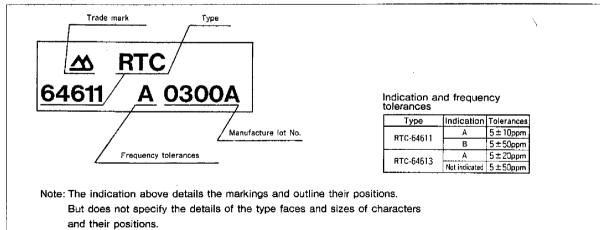

(2) Packaging precautions

#### ① Soldering temperature conditions

I. RTC-64611

Since solder is used on the quartz oscillator, if the temperature inside the package exceeds 150°C, the quartz could deteriorate or be damaged. (Solder conditions: 260°C or less × 10 seconds or less (lead portion)). Either use a solder dip tank or solder by hand. Please refrain from using paper, reflow, infrared, etc.

II. RTC-64613

Be certain to check the mounting temperature before mounting the unit, as the quartz oscillator could deteriorate and be damaged if the temperature inside the package exceeds 260°C. Also, please check the packaging temperature before using RTC-64613 when conditions change.

(Solder conditions: 260°C or less  $\times$  10 seconds or less  $\times$  2 times or fewer, or 230°C or less  $\times$  3 minutes or less) Soldering conditions for SMD products

(The rate of the rise in resin temperature should be as gradual as possible)

5

② Mounting machine

It is possible to use an all-purpose mounting machine, but please be sure to check the machine's suitability at your company before using it, as physical shocks during mounting could lead to damage of the internal quartz crystal. When there is a change in conditions, please use the machine after making the above-mentioned check.

③ Ultrasonic cleaning

Depending on the conditions, ultrasonic cleaning could cause resonance damage to the quartz crystal. Since we are unable to determine the usage conditions (type of cleaning unit, power, time, conditions inside the bath, etc.)

- at our company, we cannot guarantee the safety of this unit when it is cleaned in an ultrasound cleaner.

- ④ Mounting direction

- This module will be damaged if it is mounted backwards, so please make sure that it is packaged in the correct position. (5) Leak between terminals

Since turning on the unit when it is dirty or covered with condensation could lead to leaks between terminals, please clean and dry the module before turning it on.

سافغ

#### Application Manual for RTC-64611/64613

Issued on Nov. 20, 1990

#### SEIKO EPSON CORPORATION

QUARTZ DEVICE DIVISION QD Sales Dept. 8548 Nakaminowa, Minowa-machi, Kamiina-gun, Nagano-ken, 399-46 JAPAN Phone: (0265)79-4755 FAX: (0265)79-9492 \* Please direct inquiries to EPSON AMERICA, INC.

The manufacturer has been approved by the Reliability Center for Electronic Components of Japan (RCJ).