# SYNCHRONOUS 4-BIT COUNTER | \$54160 N74160

S54160 N74160 S54161 N74161 S54162 N74162 S54163 N74163

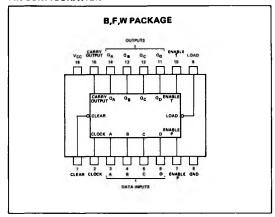

\$54160-B,F,W • \$54161-B,F,W • \$54162-B,F,W • \$54163-B,F,W N74160-B,F • N74161-B,F • N74162-B,F • N74163-B,F

DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

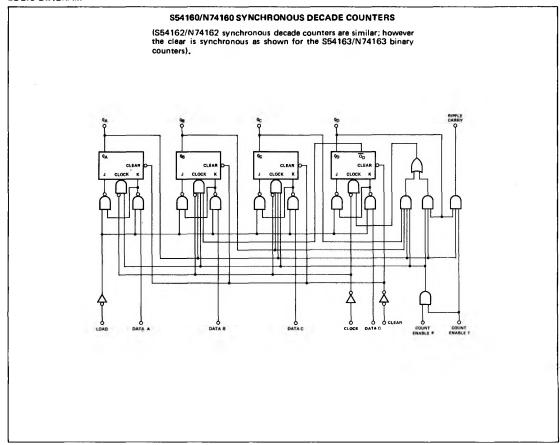

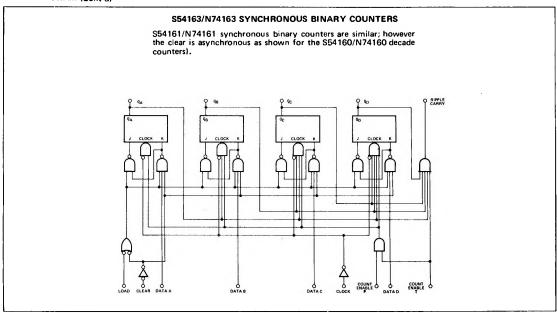

These synchronous, presettable counters feature an internal carry look-ahead for application in high-speed counting schemes. The S54160, S54162, N74160, and N74162 are decade counters and the S54161, S54163, N74161, and N74163 are 4-bit binary counters. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincident with each other when so instructed by the count-enable inputs and internal gating. This mode of operation eliminates the output counting spikes which are normally associated with asynchronous (ripple clock) counters. A buffered clock input triggers the four J-K mester-slave flip-flops on the rising (positive-going) edge of the clock input waveform.

All inputs are diode-clamped to minimize transmission-line effects, thereby simplifying system design. A full fan-out to ten normalized Series 54/74 loads is available from each of the outputs in the low-level state. A fan-out to 20 normalized Series 54/74 loads is provided in the high-level state to facilitate connection of unused inputs and power dissipation is typically 325 milliwatts.

## **PIN CONFIGURATION**

#### LOGIC DIAGRAM

## LOGIC DIAGRAM (Cont'd)

## RECOMMENDED OPERATING CONDITIONS

|                                                          | S54160, S54161<br>S54162, S54163 |     | N74160, N74161<br>N74162, N74163 |      |     | UNIT |      |

|----------------------------------------------------------|----------------------------------|-----|----------------------------------|------|-----|------|------|

|                                                          | MIN                              | NOM | MAX                              | MIN  | NOM | MAX  | Olvi |

| Supply Voltage V <sub>CC</sub>                           | 4.5                              | 5   | 5.5                              | 4.75 | 5   | 5.25 | ١ ١  |

| Normalized Fan-Out from each Output, N: High logic level |                                  |     | 20                               | 1    |     | 20   | ļ    |

| Low logic level                                          |                                  |     | 10                               |      |     | 10   |      |

| Input Clock Frequency, f <sub>clock</sub>                | 0                                |     | 25                               | 0    |     | 25   | МН   |

| Nidth of Clock Pulse, twiclock)                          | 25                               |     |                                  | 25   |     |      | ١,   |

| Nidth of Clear Pulse, tw(clear)                          | 20                               |     | Į.                               | 20   |     |      |      |

| Setup Time, t <sub>setup</sub> : Data Inputs, A,B,C,D    | 15                               |     | ľ                                | 15   |     |      |      |

| Enable P                                                 | 20                               |     | l                                | 20   |     |      | 1    |

| Load                                                     | 15                               |     | Ì                                | 15   |     |      |      |

| Clear                                                    | 20                               |     | 1                                | 20   |     |      |      |

| Hold Time at any Input, thold                            | 0                                |     | 1                                | 0    |     |      |      |

| Operating Free-Air Temperature, T <sub>A</sub>           | -55                              | 25  | 125                              | 0    | 25  | 70   | ٥    |

## ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise specified)

|     | PARAMETER                                                 | TEST CONDITIONS*                                  |                                                   | S54160,S54161<br>S54162,S54163 |       |              | N74160,N74161<br>N74162,N74163 |       |              |      |

|-----|-----------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|--------------------------------|-------|--------------|--------------------------------|-------|--------------|------|

|     | ranameren<br>s                                            | 1231 00                                           | NOTTIONS                                          | MIN                            | TYP** | MAX          | MIN                            | TYP** | MAX          | UNIT |

| VIH | High-level input voltage                                  |                                                   |                                                   | 2                              |       |              | 2                              |       |              | V    |

| VIL | Low-level input voltage                                   | VCC = MAX,                                        |                                                   |                                | 1     | 0.8          |                                |       | 0.8          | l v  |

| vi_ | Input clamp voltage                                       | VCC = MAX,                                        | I <sub>I</sub> = -12mA                            |                                |       | -1.5         |                                |       | -1.5         | V    |

| VOH | High-level output voltage                                 | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8V, | V <sub>IH</sub> = 2V,<br>I <sub>OH</sub> = -800μA | 2.4                            | İ     |              | 2.4                            |       |              | v    |

| VOL | Low-level output voltage                                  | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8V, | V <sub>IH</sub> = 2V,<br>I <sub>OL</sub> = 16mA   |                                |       | 0.4          |                                |       | 0.4          | V    |

| Ŋ   | Input current at maximum<br>input voltage                 | V <sub>CC</sub> = MAX,                            | V <sub>1</sub> = 5.5V                             |                                | İ     | 1            |                                |       | 1            | mA   |

| ΙΗ  | High-level Clock or enable T input current Other inputs   | V <sub>CC</sub> = MAX,                            | V <sub>I</sub> = 2.4V                             |                                |       | 80<br>40     |                                |       | 80<br>40     | μА   |

| IIL | Low-level Clock or enable T<br>input current Other inputs | V <sub>CC</sub> = MAX,                            | V <sub>1</sub> = 0.4V                             |                                |       | -3.2<br>-1.6 |                                |       | -3.2<br>-1.6 | mA   |

| los | Short-circuit output current †                            | V <sub>CC</sub> = MAX                             |                                                   | -20                            |       | -57          | -18                            | ]     | -57          | mA   |

|     | Supply current, all outputs high                          | V <sub>CC</sub> = MAX,                            | See Note 3                                        |                                | 59    | 85           | 1                              | 59    | 94           | mA.  |

| CCL | Supply current, all outputs low                           | V <sub>CC</sub> = MAX,                            | See Note 4                                        |                                | 63    | 91           |                                | 63    | 101          | mA.  |

## DIGITAL 54/74 TTL SERIES = \$54/N74160, \$54/N74161, \$54/N74162, \$54/N74163

## SWITCHING CHARACTERISTICS, $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ , N = 10

|                  | PARAMETER                                                            | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------------------------------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>max</sub> | Maximum input clock frequency                                        |                                              | 25  | 32  | -   | MHz  |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level carry output from clock    | C <sub>L</sub> = 15pF, R <sub>L</sub> = 400Ω |     | 23  | 35  | 1    |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level carry output from clock    |                                              |     | 23  | 35  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level  Q output from clock       |                                              |     | 13  | 20  |      |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level $\Omega$ output from clock |                                              |     | 15  | 23  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level carry output from enable T |                                              |     | 8   | 13  |      |

| <sup>I</sup> PHL | Propagation delay time, high-to-low-level carry output from enable T |                                              |     | 10  | 15  | n    |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level  Q output from clear       |                                              |     | 20  | 30  | n    |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

#### NOTES:

- 3. I<sub>CCH</sub> is measured with the load input high, then again with the load input low, with all other inputs high and all outputs open.

- 4. ICCL is measured with the clock input high, then again with the clock input low, with all other inputs low and all outputs open.

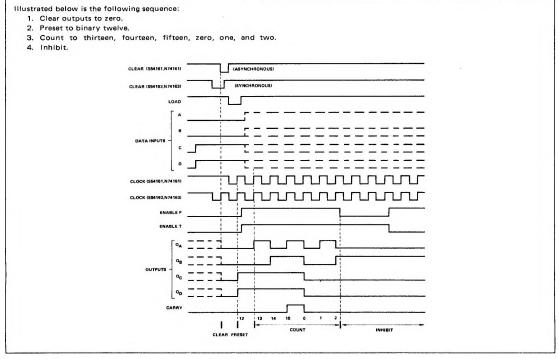

## TYPICAL CLEAR, PRESET, COUNT, AND INHIBIT SEQUENCES FOR 54161, 74161, 54163, 74163 SYNCHRONOUS BINARY COUNTERS

<sup>\*\*</sup> All typical values are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

† Not more than one output should be shorted at a time.

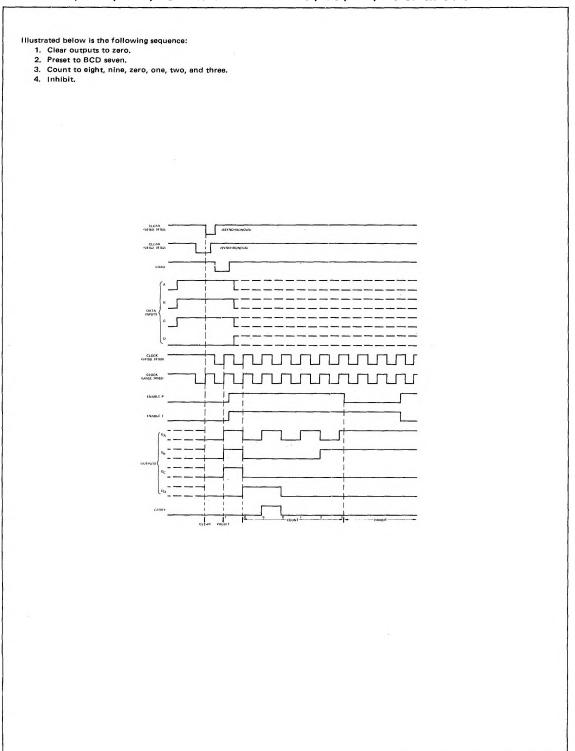

## TYPICAL CLEAR, PRESET, COUNT, AND INHIBIT SEQUENCES FOR 54160, 54162, 74160, 74162 SYNCHRONOUS BINARY COUNTERS

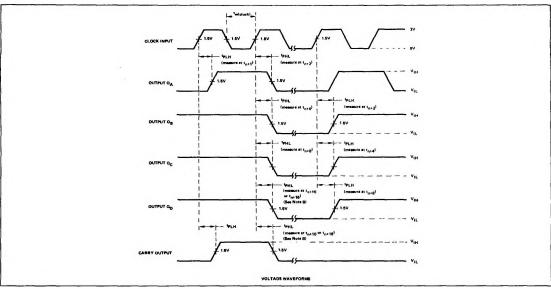

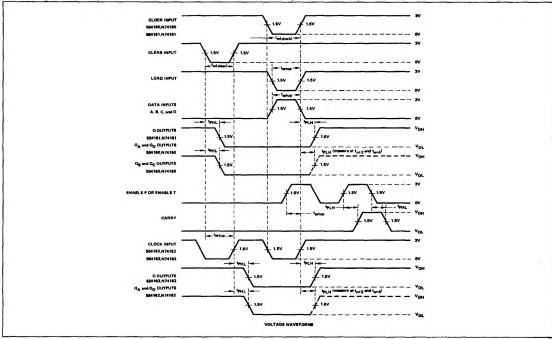

## PARAMETER MEASUREMENT INFORMATION

#### NOTES:

- A. The input pulses are supplied by a generator having the following characteristics:  $t_r \le 10 ns$ ;  $t_f \le 10 ns$ ,  $PRR \le 1$  MHz, duty cycle  $\le 50\%$ ,

- Z<sub>out</sub> ≈ 50Ω. Very PRR to measure f<sub>max</sub>.

B. Outputs Q<sub>D</sub> and carry are tested at t<sub>n+10</sub> for the S54160, S54162, N74160, and N74162, and at t<sub>n+16</sub> for the S64161, S54163, N74161, and N74163, where t<sub>n</sub> is the bit time when all outputs are low.

## NOTES:

- A. The input pulses are supplied by a generator having the following characteristics:  $t_{\rm p} \le 10 {\rm ns}$ ;  $t_{\rm f} \le 10 {\rm ns}$ ; PRR  $\le 1$  MHz, duty cycle  $\le 50 {\rm %}$ ;

- $\rm Z_{out} \approx 50\Omega.$  B. Enable P and enable T setup times are measured at  $t_n$  = 0.

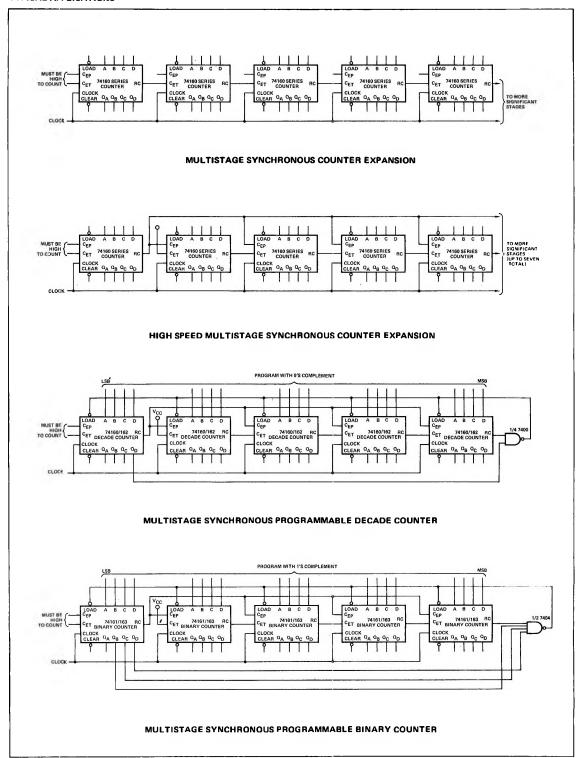

## TYPICAL APPLICATIONS