# GATED FULL ADDER | \$5480

N7480

\$5480-A.F.W . N7480-A.F

# DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

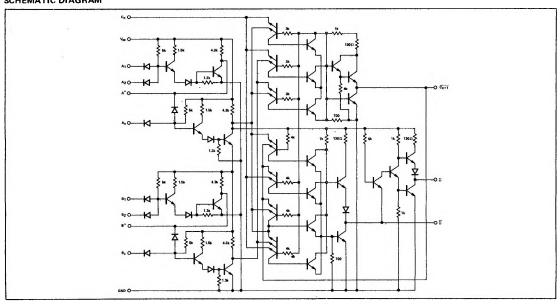

The S5480/N7480 is a single-bit, high-speed, binary full adder with gated complementary inputs, complementary sum ( $\Sigma$  and  $\overline{\Sigma}$ ) outputs and inverted carry output. Designed for medium- and high-speed, multiple-bit, parallel-add/serial-carry applications, the circuit (see schematic diagram) utilizes diode-transistor logic (DTL) for the gated inputs, and high-speed, high-fan-out transistortransistor logic (TTL) for the sum and carry outputs. The circuit is entirely compatible with both DTL and TTL logic families. The implementation of a single-inversion, high-speed, Darlingtonconnected serial-carry circuit minimizes the necessity for extensive "look-ahead" and carry-cascading circuits. The power dissipation has been maintained considerably below that attainable with equivalent standard integrated circuits connected to perform fulladder functions.

TRUTH TABLE (See Notes 1,2, and 3)

| _     | T _ | 1   |                  | = | - |

|-------|-----|-----|------------------|---|---|

| $c_n$ | B   | l A | C <sub>n+1</sub> | Σ | Σ |

| 0     | 0   | 0   | 1                | 1 | 0 |

| 0     | 0   | 1   | 1                | 0 | 1 |

| 0     | 1   | 0   | 1                | 0 | 1 |

| 0     | 1   | 1   | 0                | 1 | 0 |

| 1     | 0   | 0   | 1                | 0 | 1 |

| 1     | 0   | 1   | 0                | 1 | 0 |

| 1     | 1   | 0   | 0                | 1 | 0 |

| 1     | 1   | 1   | 0                | 0 | 1 |

#### NOTES:

- 1.  $A = \overline{A^{\bullet} \cdot A_{c}}$ ,  $B = \overline{B^{\bullet} \cdot B_{c}}$  where  $A^{\bullet} = \overline{A_{1} \cdot A_{2}}$ ,  $B^{\bullet} = \overline{B_{1} \cdot B_{2}}$ . 2. When  $A^{\bullet}$  or  $B^{\bullet}$  are used as inputs,  $A_{1}$  and  $A_{2}$  or  $B_{1}$  and  $B_{2}$

- respectively, must be connected to GND.

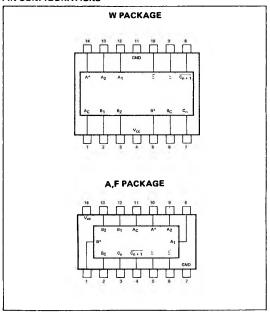

#### PIN CONFIGURATIONS

- When  $A_1$  and  $A_2$  or  $B_1$  and  $B_2$  are used as inputs,  $A^\star$  or  $B^\star$  respectively, must be open or used to perform Dot-OR logic. The voltages are with respect to ground terminal.

- Input signals must be zero or positive with respect to network ground terminal.

### SCHEMATIC DIAGRAM

# **RECOMMENDED OPERATING CONDITIONS**

|                                                          | MIN  | NOM | MAX  | UNIT        |

|----------------------------------------------------------|------|-----|------|-------------|

| Supply Voltage V <sub>CC</sub> : S5480 Circuits          | 4.5  | 5   | 5.25 | <b>&gt;</b> |

| N7480 Circuits                                           | 4.75 | 5   | 5.25 |             |

| Normalized Fan-Out from Outputs: C <sub>n</sub> +1, N    | i    | \   | 5    | 1           |

| $\Sigma$ or $\overline{\Sigma}$ , N                      |      | ĺ   | 10   |             |

| A* or B*, N                                              |      |     | 3    |             |

| Operating Free-Air Temperature Range, TA: S5480 Circuits | -55  | 25  | 125  | °C          |

| N7480 Circuits                                           | 0    | 25  | 70   | °c          |

# ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted):

| PARAMETER           |                                                                                 | TEST CONDITIONS*                                 |                                                  |                | MIN        | TYP**    | MAX        | UNIT             |

|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------|------------|----------|------------|------------------|

| V <sub>in(1)</sub>  | Logical 1 input voltage                                                         | V <sub>CC</sub> = MIN                            |                                                  |                | 2          |          |            | v                |

| V <sub>in(0)</sub>  | Logical 0 input voltage                                                         | V <sub>CC</sub> - MIN                            |                                                  |                |            |          | 8.0        | \ v              |

| V <sub>out(1)</sub> | Logical 1 output voltage                                                        | V <sub>CC</sub> = MIN                            |                                                  |                | 2.4        | 3.5      |            | v                |

| $V_{out(0)}$        | Logical 0 output voltage                                                        | V <sub>CC</sub> = MIN                            |                                                  |                |            | 0.22     | 0.4        | ( v              |

| lin(0)              | Logical 0 level input current at $A_1$ , $A_2$ , $B_1$ , $B_2$ , $A_c$ or $B_c$ | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |          | -1.6       | mA               |

| lin(0)              | Logical 0 level input<br>current at A* or B*                                    | V <sub>CC</sub> = MAX,                           | $V_{in} = 0.4V$                                  |                |            |          | -2.6       | mA               |

| lin(0)              | Logical 0 level input<br>current at C <sub>n</sub>                              | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |          | -8         | mA               |

| <sup>1</sup> in(1)  | Logical 1 level input current at $A_1$ , $A_2$ , $B_1$ , $B_2$ , $A_c$ or $B_c$ | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX  | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | 15<br>1    | μA<br>mA         |

| lin(1)              | Logical 1 level input current at Cn                                             | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | 200<br>1   | μA<br>m <b>A</b> |

| los                 | Short circuit output current at $\Sigma$ or $\Sigma$ †                          | V <sub>CC</sub> = MAX,                           |                                                  | S5480<br>N7480 | -20<br>-18 |          | -57<br>-57 | mA<br>mA         |

| los                 | Short circuit output current at Cn+1†                                           | V <sub>CC</sub> = MAX,                           |                                                  | S5480<br>N7480 | -20<br>-18 |          | -70<br>-70 | mA<br>mA         |

| <sup>I</sup> cc     | Supply current                                                                  | V <sub>CC</sub> = MAX,                           |                                                  | S5480<br>N7480 |            | 21<br>21 | 31<br>35   | mA<br>mA         |

# SWITCHING CHARACTERISTICS, VCC = 5V, TA = 25°C

| PARAMETER¶       | FROM           | то<br>оитрит        | TEST CONDITIONS        |                   | MIN | TYP | MAX | UNIT |

|------------------|----------------|---------------------|------------------------|-------------------|-----|-----|-----|------|

| t <sub>pd1</sub> |                |                     | C <sub>1</sub> = 15pF, | $R_1 = 780\Omega$ |     | 13  | 17  | ns   |

| tpd0             | Cn             | C <sub>n+1</sub>    | C <sub>1</sub> = 15pF, | $R_1 = 780\Omega$ |     | 8   | 12  | ns   |

| <sup>t</sup> pd1 | D              | <u>c</u>            | C = 15pF,              | RL = 780Ω         |     | 18  | 25  | ns   |

| tpd0             | ВС             | C <sub>n+1</sub>    | CL = 15pF,             | R                 |     | 38  | 55  | ns   |

| <sup>t</sup> pd1 | 100            | 24                  | C <sub>1</sub> = 15pF, | $R_L = 400\Omega$ |     | 52  | 70  | ns   |

| <sup>t</sup> pd0 | Ac             | Σ                   | CL = 15pF,             | R = 400Ω          |     | 62  | 80  | ns   |

| <sup>t</sup> pd1 | 1 62           | -                   | C = 15pF,              | $R_1 = 400\Omega$ |     | 38  | 55  | ns   |

| tpd0             | BC             | $\overline{\Sigma}$ | C = 15pF,              | $R_L = 400\Omega$ |     | 56  | 75  | ns   |

| <sup>t</sup> pd1 | 4.20           | 1000                | C = 15pF               |                   |     | 48  | 65  | ns   |

| <sup>t</sup> pd0 | A <sub>1</sub> | A*                  | C = 15pF               |                   |     | 17  | 25  | ns   |

| tpd1             |                |                     | C = 15pF               |                   |     | 48  | 65  | ns   |

| tpd0             | B <sub>1</sub> | В*                  | C = 15pF               |                   |     | 17  | 25  | ns   |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

<sup>\*\*</sup> All typical values are at V<sub>CC</sub>= 5V, T<sub>A</sub> = 25°C

f Not more than one output should be shorted at a time.

$<sup>\</sup>P$  t<sub>pd1</sub> is propagation delay time to logical 1 level. t<sub>pd0</sub> is propagation delay time to logical 0 level.