## ST63RT1

## 8-BIT HCMOS UNIVERSAL ROMLESS MCU FOR TV APPLICATIONS

ADVANCE DATA

- UNIVERSAL ST63XX FAMILY EMULATION CHIP

- 8-BIT ARCHITECTURE

- STATIC HCMOS OPERATION

- 4.5 TO 5.5 V SUPPLY OPERATING RANGE

- 4MHZ OR 8MHZ CLOCK OPTIONS

- PROGRAM ROM: 16K BYTES EXTERNAL

- DATA ROM: USER SELECTABLE SIZE

- DATA RAM: 256 BYTESDATA EEPROM: 128 BYTES

- 120 CERAMIC PGA PACKAGE

- 14/15 BIT PHASE LOCKED LOOP PERIPHE-RAL (PLL)

- 14 BIT VOLTAGE SYNTHESIS TUNING PE-RIPHERAL (VS)

- ON-CHIP 5 LINES BY 15 COLUMNS ON-SCREEN-DISPLAY GENERATOR (OSD)

- THE ON-CHIP OSD CAN BE DISABLED ALLOWING DIRECT DRIVING OF AN EXTER-NAL OSD GENERATOR (ST63RS1).

- 24 SOFTWARE PROGRAMMABLE GENERAL PURPOSE INPUTS/OUTPUTS, INCLUDING 8 DIRECT LED DRIVING OUTPUTS

- TWO TIMERS EACH INCLUDING AN 8-BIT COUNTER WITH A 7-BIT PROGRAMMABLE PRESCALER

- DIGITAL WATCHDOG FUNCTION

- SERIAL PERIPHERAL INTERFACE (SPI) SUP-PORTING S-BUS/I<sup>2</sup>CBUS AND STANDARD SERIAL PROTOCOLS

- FOUR 6-BIT PWM D/A CONVERTERS

- AFC A/D CONVERTER WITH 0.5V RESOLUTION

- INFRARED SIGNAL PRE-PROCESSOR

- FOUR INTERRUPT VECTORS (IR, Timer 1 & 2, OSD VSYNC)

- ON-CHIP CLOCK OSCILLATOR

- ON-BOARD POWER-ON RESET CIRCUITRY

- ALL ROM TYPES ARE SUPPORTED BY PIN-TO-PIN PIGGYBACK VERSIONS.

- BYTE EFFICIENT INSTRUCTION SET

- BIT TEST AND JUMP INSTRUCTIONS

- WAIT, STOP AND BIT MANIPULATION IN-STRUCTIONS

- 1.625µs TCYCLE (8.0 MHz clock)

- TRUE LIFO 6-LEVEL STACK

- THE DEVELOPMENT TOOL OF THE ST63XX MICROCONTROLLERS CONSISTS OF THE EMST63-HW/TVS EMULATION AND DEVELOPMENT SYSTEM CONNECTED VIA A STANDARD RS232 SERIAL LINE TO AN MS-DOS<sup>TM</sup> PC.

## **GENERAL DESCRIPTION**

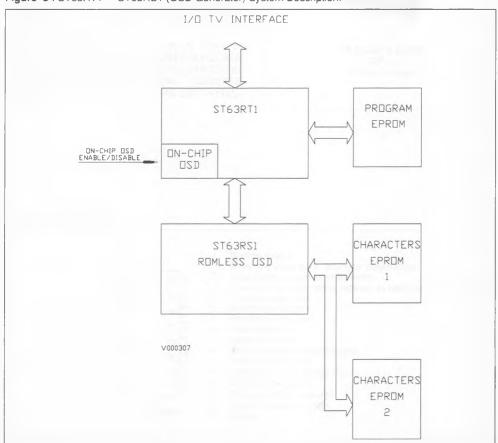

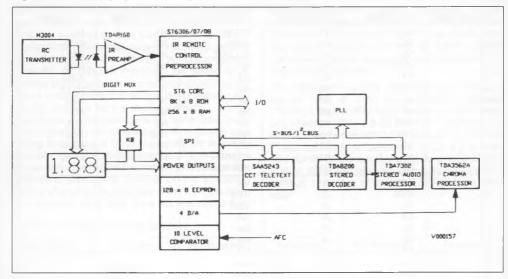

The ST63RT1 universal romless device is the emulation device of the 8-bit HCMOS ST63XX MCU family, a series of devices specially oriented to TV applications. Different packages and configurations are available to offer different performance/cost tradeoffs. All ST63XX members are based on a building block approach: to a common Core is associated a combination of on-chip peripherals (macrocells) available from a standard library. These peripherals are designed with the same Core technology providing full compatibility, short design and testing time. Many of these macrocells are specially dedicated to TV applications. The ST63RT1 romless device offers all the macrocells available on the different ST63 masked devices. On the ST63RT1 instead of on-chip program and data ROM, the relevant "address" and "data" lines are lead out so that

an external memory can be addressed. The addressing capability of this device is 16K; in addition the on-chip OSD of the ST63RT1 can be disabled and an external OSD generator (ST63RS1) can be addressed to allow the generation of customized onscreen character sets.

The macrocells of the ST63RS1 are: two 8-bit counter with a 7-bit programmable prescaler (Timer), a Digital Watchdog Timer, a Serial Peripheral Interface (SPI), a 6-Bit PWM D/A Converter, an AFC A/D converter with 0.5V resolution, a 14/15 bit Phase Locked Loop peripheral (PLL), a 5 lines by 15 columns On-screen display generator (OSD) and a 14 bit Voltage synthesis tuning peripheral (VS). In addition 128 bytes of on-chip EEPROM are available.

Figure 1: ST63RT1 Pin Assignment.

| Pin Number | Function | Pin Number | Function | Pin Number | Function |

|------------|----------|------------|----------|------------|----------|

| A1         | NC       | F1         | PC4      | L1         | NC       |

| A2         | RESET    | F2         | IDB4     | L2         | NC       |

| A3         | IDB6     | F3         | PC3/BLK  | L3         | NC       |

| A4         | PA2      | F4         | NA       | L4         | OUT1     |

| A5         | IDB7     | F5         | NA       | L5         | DA4      |

| A6         | AD0      | F6         | NA       | L6         | AD13     |

| A7         | AD1      | F7         | NA       | L7         | AD8      |

| A8         | D3       | F8         | NA       | L8         | AD5      |

| A9         | D2       | F9         | NA       | L9         | CDEDLD   |

| A10        | D0       | F10        | NA       | L10        | BSW3     |

| A11        | PA5      | F11        | PB0      | L11        | NC       |

| A12        | VDD      | F12        | PB1      | L12        | IAB3     |

| A13        | NC       | F13        | PB2/VSYN | L13        | KBY0     |

| B1         | NC       | G1         | PC7/B    | M1         | NC       |

| B2         | NC       | G2         | PC5/R    | M2         | NC       |

| B3         | NC       | G3         | PC6/G    | M3         | DA1      |

| B4         | PA0      | G4         | NA       | M4         | DA3      |

| B5         | PA3      | G5         | NA       | M5         | VDD      |

| B6         | CE       | G6         | NA       | M6         | AD10     |

| B7         | D6       | G7         | NA       | M7         | AD9      |

| B8         | D4       | G8         | NA       | M8         | AD6      |

| B9         | D1       | G9         | NA       | M9         | AD2      |

| B10        | PA4      | G10        | NA       | M10        | BSW0     |

| B11        | PA6      | G11        | PB4      | M11        | NC       |

| B12        | NC       | G12        | PB5/SCL  | M12        | NC       |

| B13        | NC       | G13        | PB3/HSYN | M13        | NC       |

Figure 1: ST63RT1 Pin Assignment - Cont'ed

| Pin Number                                                                     | Function                                                                                    | Pin Number                                                                     | Function                                                 | Pin Number                                                                     | Function                                                                                     |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| C1<br>C2<br>C3<br>C4<br>C5<br>C6<br>C7<br>C8<br>C9<br>C10<br>C11<br>C12<br>C13 | NC<br>NC<br>NC<br>OSCOUT<br>PA1<br>VSS<br>D7<br>D5<br>IAB2<br>PA7<br>NC<br>NC               | H1<br>H2<br>H3<br>H4<br>H5<br>H6<br>H7<br>H8<br>H9<br>H10<br>H11<br>H12<br>H13 | PLLIN IDB3 PLLOUT NA | N1<br>N2<br>N3<br>N4<br>N5<br>N6<br>N7<br>N8<br>N9<br>N10<br>N11<br>N12<br>N13 | NC<br>IDB0<br>DA2<br>IAB5<br>AD12<br>AD11<br>IAB4<br>AD7<br>AD4<br>AD3<br>BSW1<br>BSW2<br>NC |

| D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7<br>D8<br>D9<br>D10<br>D11<br>D12<br>D13 | PCO<br>IDB5<br>NC<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA<br>NC<br>NC<br>TEST | J1 J2 J3 J4 J5 J6 J7 J8 J9 J10 J11 J12 J13                                     | VS IDB2 VSS NA NA NA NA NA NA NA NA OSDOSCIN OSDOSCO     | NIO                                                                            |                                                                                              |

| E1<br>E2<br>E3<br>E4<br>E5<br>E6<br>E7<br>E8<br>E9<br>E10<br>E11<br>E12<br>E13 | PC2-ON/OFF PC1 OSCIN NA                                 | K1<br>K2<br>K3<br>K4<br>K5<br>K6<br>K7<br>K8<br>K9<br>K10<br>K11<br>K12        | IRIN IDB1 NC NA      |                                                                                |                                                                                              |

NC: Not Connected

NA: Not Available

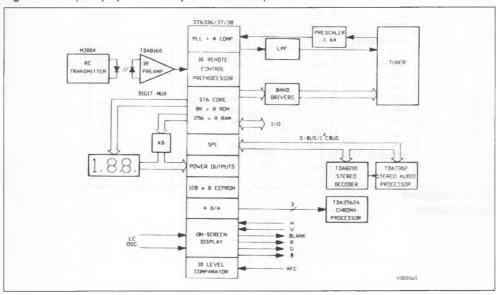

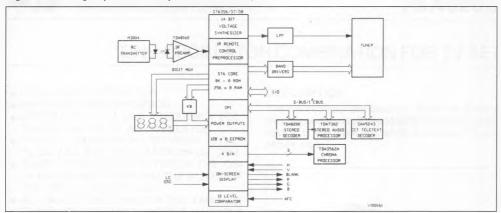

Figure 2: Frequency Synthesis TV System with External PLL.

Figure 3: Frequency Synthesis TV System with On-chip PLL and OSD.

Figure 4: Voltage Synthesis TV System with On-chip OSD.

Figure 5: ST63RT1 - ST63RS1 (OSD Generator) System Description.