# **Signetics**

# TDA8442 Quad DAC With I<sup>2</sup>C Interface

**Product Specification**

### **Linear Products**

### DESCRIPTION

The TDA8442 consists of four 6-bit D/A converters and 3 output ports. This IC was designed to provide I<sup>2</sup>C control, by replacing the potentiometers, for the TDA3560-series single-chip color decoders. Control of the IC is performed via the two-line, bidirectional I<sup>2</sup>C bus.

### **FEATURES**

- 6-bit resolution

- 3 output ports

- I<sup>2</sup>C control

### **APPLICATIONS**

- I<sup>2</sup>C interface control

- System control

- Switching

### ORDERING INFORMATION

| DESCRIPTION                 | TEMPERATURE RANGE | ORDER CODE |

|-----------------------------|-------------------|------------|

| 16-Pin Plastic DIP (SOT-38) | -20°C to +70°C    | TDA8442N   |

### ABSOLUTE MAXIMUM RATINGS

| SYMBOL                                        | PARAMETER                                                                                      | RATING                                                                                                                                                                                         | UNIT |

|-----------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>CC</sub>                               | Supply voltage range (Pin 9)                                                                   | -0.3 to +13.2                                                                                                                                                                                  | ٧    |

| VSDA<br>VSCL<br>VGC2<br>VGC2N<br>VGC1<br>VDAX | Input/output voltage ranges (Pin 4) (Pin 5) (Pin 6) (Pin 12) (Pin 11) (Pins 1 to 3 and Pin 16) | -0.3 to +13.2<br>-0.3 to +13.2<br>-0.3 to V <sub>CC</sub> <sup>1</sup><br>-0.3 to V <sub>CC</sub> <sup>1</sup><br>-0.3 to V <sub>CC</sub> <sup>1</sup><br>-0.3 to V <sub>CC</sub> <sup>1</sup> | >    |

| P <sub>TOT</sub>                              | Total power dissipation                                                                        | 1                                                                                                                                                                                              | w    |

| TA                                            | Operating ambient temperature range                                                            | -20 to +70                                                                                                                                                                                     | °C   |

| T <sub>STG</sub>                              | Storage temperature range                                                                      | -65 to +150                                                                                                                                                                                    | °C   |

#### NOTE:

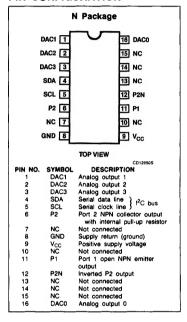

### PIN CONFIGURATION

<sup>1.</sup> Pin voltage may exceed  $V_{\text{CC}}$  if the current in that pin is limited to 10mA.

**TDA8442**

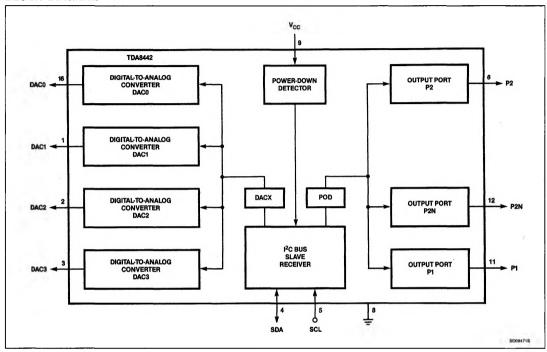

### **BLOCK DIAGRAM**

**TDA8442**

DC AND AC ELECTRICAL CHARACTERISTICS  $T_A = +25$ °C;  $V_{CC} = 12V$ , unless otherwise specified.

| CYMPO                   |                                                                    |                                   | LIMITS |                    |      |

|-------------------------|--------------------------------------------------------------------|-----------------------------------|--------|--------------------|------|

| SYMBOL                  | PARAMETER                                                          | Min                               | Тур    | Max                | UNIT |

| Supplies                |                                                                    |                                   |        |                    |      |

| V <sub>CC</sub>         | Supply voltage (Pin 9)                                             | 10.8                              | 12     | 13.2               | ٧    |

| Icc                     | Supply currents (no outputs loaded) (Pin 9)                        |                                   | 12     |                    | mA   |

| I <sup>2</sup> C bus in | puts SDA (Pin 4) and SCL (Pin 5)                                   | -                                 |        |                    |      |

| V <sub>IH</sub>         | Input voltage High <sup>1</sup>                                    | 3                                 |        | V <sub>CC</sub> -1 | V    |

| VIL                     | Input voltage Low                                                  | -0.3                              |        | 1.5                | V    |

| I <sub>IH</sub>         | Input current High <sup>1</sup>                                    |                                   |        | 10                 | μА   |

| I <sub>IL</sub>         | Input current Low <sup>1</sup>                                     |                                   |        | 10                 | μА   |

| I <sup>2</sup> C bus or | utput SDA (Pin 4) (open-collector)                                 |                                   |        |                    |      |

| V <sub>OL</sub>         | Output voltage Low at I <sub>OL</sub> = 3.0mA                      |                                   |        | 0.4                |      |

| loL                     | Maximum output sink current                                        |                                   | 5      |                    | mA   |

| Ports P2 a              | and P2N (Pins 6 and 12) (NPN collector output with pull            | -up resistor to V <sub>CC</sub> ) |        | •                  |      |

| Ro                      | Internal pull-up resistor to V <sub>CC</sub>                       | 5                                 | 10     | 15                 | kΩ   |

| V <sub>OL</sub>         | Output voltage Low at I <sub>OL</sub> = 2mA                        |                                   |        | 0.4                | V    |

| loL                     | Maximum output sink current                                        | 2                                 | 5      |                    | mA   |

| Port P1 (P              | Pin 11) (open NPN emitter output)                                  | •                                 |        | •                  |      |

| Гон                     | Output current High at 0 < V <sub>O</sub> < V <sub>CC</sub> - 1.5V | 14                                |        |                    | mA   |

| loL                     | Output leakage current at 0 < V <sub>O</sub> < V <sub>CC</sub> V   |                                   |        | 100                | μА   |

| Digital-to-a            | analog outputs Output DAC0 (Pin 16)                                | •                                 |        |                    |      |

| V <sub>OMAX</sub>       | Maximum output voltage (unloaded) <sup>2</sup>                     | 3                                 |        |                    | V    |

| V <sub>OMIN</sub>       | Minimum output voltage (unloaded) <sup>2</sup>                     |                                   |        | 1                  | V    |

| V <sub>OLSB</sub>       | Positive value of smallest step <sup>2</sup> (1 LSB)               | 0                                 |        | 100                | mV   |

|                         | Deviation from linearity                                           |                                   | -      | 150                | mV   |

| Z <sub>O</sub>          | Output impedance at -2 < I <sub>O</sub> < +2mA                     |                                   |        | 70                 | Ω    |

| -I <sub>OH</sub>        | Maximum output source current                                      | 2                                 |        | 6                  | mA   |

| loL                     | Maximum output sink current                                        | 2                                 | 8      |                    | mA   |

| Output DA               | AC1 (Pin 1)                                                        | '                                 |        |                    |      |

| V <sub>OMAX</sub>       | Maximum output voltage (unloaded) <sup>2</sup>                     | 4                                 |        |                    | ٧    |

| V <sub>OMIN</sub>       | Minimum output voltage (unloaded) <sup>2</sup>                     |                                   |        | 1.7                | V    |

| V <sub>OLSB</sub>       | Positive value of smallest step <sup>2</sup> (1 LSB)               | 0                                 |        | 120                | mV   |

|                         | Deviation from linearity                                           |                                   |        | 170                | mV   |

| z <sub>o</sub>          | Output impedance at -2 < I <sub>O</sub> < +2mA                     |                                   |        | 70                 | Ω    |

| _l <sub>OH</sub>        | Maximum output source current                                      | 2                                 |        | 6                  | mA   |

| loL                     | Maximum output sink current                                        | 2                                 | 8      | 1                  | mA   |

**TDA8442**

### DC AND AC ELECTRICAL CHARACTERISTICS (Continued) T<sub>A</sub> = +25°C; V<sub>CC</sub> = 12V, unless otherwise specified.

|                   |                                                                                                    | LIMITS |     |      |      |

|-------------------|----------------------------------------------------------------------------------------------------|--------|-----|------|------|

| SYMBOL            | PARAMETER                                                                                          | Min    | Тур | Max  | UNIT |

| Output DA         | C2 (Pin 2)                                                                                         |        | •   |      | -    |

| V <sub>OMAX</sub> | Maximum output voltage (unloaded) <sup>2</sup>                                                     | 4      |     |      | ٧    |

| V <sub>OMIN</sub> | Minimum output voltage (unloaded) <sup>2</sup>                                                     |        |     | 1.7  | V    |

| Volse             | Positive value of smallest step <sup>2</sup> (1 LSB)                                               | 0      |     | 120  | mV   |

|                   | Deviation from linearity                                                                           |        |     | 170  | mV   |

| Zo                | Output impedance at -2 < I <sub>O</sub> < +2mA                                                     |        |     | 70   | Ω    |

| -l <sub>OH</sub>  | Maximum output source current                                                                      | 2      |     | 6    | mA   |

| loL               | Maximum output sink current                                                                        | 2      | 8   |      | mA   |

| Output DA         | C3 (Pin 3)                                                                                         |        |     |      |      |

| V <sub>OMAX</sub> | Maximum output voltage (unloaded) <sup>2</sup>                                                     | 10     |     |      | V    |

| V <sub>OMIN</sub> | Minimum output voltage (unloaded) <sup>2</sup>                                                     |        |     | 1    | V    |

| Volse             | Positive value of smallest step <sup>2</sup> (1 LSB)                                               | 0      |     | 350  | mV   |

|                   | Deviation from linearity                                                                           |        |     | 0.50 | ٧    |

| Z <sub>O</sub>    | Output impedance at -2 < I <sub>O</sub> < +2mA                                                     |        |     | 70   | Ω    |

| -loh              | Maximum output source current                                                                      | 2      |     | 6    | mA   |

| loL               | Maximum output sink current                                                                        | 2      | 8   |      | mA   |

| Power-dov         | vn reset                                                                                           | •      |     |      |      |

| V <sub>CCD</sub>  | Maximum value of V <sub>CC</sub> at which power-down reset is active                               | 6      |     | 10   | ٧    |

| t <sub>R</sub>    | Rise time of V <sub>CC</sub> during power-on (V <sub>CC</sub> rising from 0V to V <sub>CCD</sub> ) | 5      |     |      | μs   |

### NOTES:

<sup>1.</sup> If  $V_{CC} < 1V$ , the input current is limited to  $10 \mu A$  at input voltages up to 13.2V.

<sup>2.</sup> Values are proportional to V<sub>CC</sub>.

**TDA8442**

### **FUNCTIONAL DESCRIPTION**

#### **Control**

Analog control is facilitated by four 6-bit digital-to-analog converters (DAC0 to DAC3). The values of the output voltages from the DACs are set via the  $\rm I^2C$  bus.

The high-current output port (P1) is suitable for switching between internal and external RGB signals. It is an open NPN emitter output capable of sourcing 14mA (minimum).

The two output ports (P2 and P2N) can be used for NTSC/PAL switching. These are NPN collector outputs with internal pull-up resistors of  $10k\Omega$  (typical). Both outputs are capable of sinking up to 2mA with a voltage drop of less than 400mV. If one output is programmed to be Low, the other output will be High, and vice versa.

#### Reset

The power-down reset mode occurs whenever the positive supply voltage falls below 8.5V (typical) and resets all registers to a defined state.

### **OPERATION**

#### Write

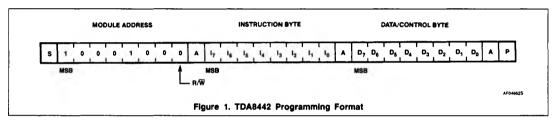

The TDA8442 is controlled via the I<sup>2</sup>C bus. Programming of the TDA8442 is performed using the format shown in Figure 1.

Acknowledge (A) is generated by the TDA8442 only when a valid address is received and the device is not in the power-down reset mode ( $V_{CG} > 8.5V$  (typ)).

### **Control**

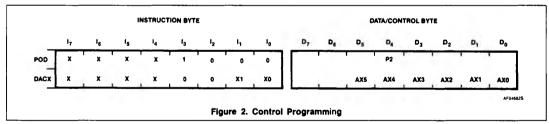

Control is implemented by the instruction bytes POD (port output data) and DACX

(digital-to-analog converter control), and the corresponding data/control bytes (see Figure 2)

POD Bit P1 — If a '1' is programmed, the P1 output is forced High. If a '0' is programmed, or after a power-down reset, the P1 output is Low (high-impedance state).

POD Bit P2/P2N — If a '1' is programmed, the P2 output goes High and the P2N output goes Low. If a '0' is programmed, and after a power-down reset, the P2 output is Low and the P2N output is High.

DAX Bits AX5 to AX0 — The digital-toanalog converter selected corresponds to the decimal equivalent of the two bits X1 and X0. The output voltage of the selected DAC is programmed using Bits AX5 to AX0, the lowest value being all AX5 to AX0 data at '0', or when power-down reset has been activated.

**TDA8442**

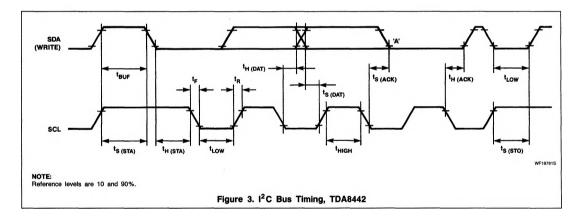

I<sup>2</sup>C BUS TIMING

Bus loading conditions:  $4k\Omega$  pull-up resistor to +5V; 200pF capacitor to GND. All values are referred to  $V_{IH}=3V$  and  $V_{IL}=1.5V$ .

| SYMBOL                             | PARAMETER                             |      | LIMITS |      |      |

|------------------------------------|---------------------------------------|------|--------|------|------|

|                                    |                                       | Min  | Тур    | Max  | UNIT |

| t <sub>BUF</sub>                   | Bus free before start                 | 4    |        |      | μs   |

| tsu, tsta                          | Start condition setup time            | 4    |        |      | μs   |

| t <sub>HD</sub> , t <sub>STA</sub> | Start condition hold time             | 4    |        |      | μs   |

| t <sub>LOW</sub>                   | Low period SCL, SDA                   | 4    |        |      | μs   |

| t <sub>HIGH</sub>                  | High period SCL                       | 4    |        |      | μs   |

| t <sub>R</sub>                     | Rise time SCL, SDA                    |      |        | 1    | μs   |

| t <sub>F</sub>                     | Fall time SCL, SDA                    |      |        | 0.30 | μs   |

| tsu, tDAT                          | Data setup time (write)               | 0.25 |        |      | μs   |

| t <sub>HD</sub> , t <sub>DAT</sub> | Data hold time (write)                | 0    |        |      | μs   |

| tsu, tack                          | Acknowledge (from TDA8442) setup time |      |        | 2    | μs   |

| tho, tack                          | Acknowledge (from TDA8442) hold time  | 0    |        |      | μs   |

| tsu, tsto                          | Stop condition setup time             | 4    |        |      | μs   |