# UM83C003

# Hard Disk Controller Interface

ADVANCED PRODUCT DESCRIPTION

#### **Features**

- Interfaces to PC XT systems with Hard-Disk controller

- I/O channel ready signal generator (generates wait state)

- Clock generator

### **General Description**

The UM83C003 incorporates several functions in a single package. Implementation of these functions occurs by combining random logic. The UM83C003 contains the following circuits:

Clock Generator

- Sector buffer RAM addressing and control

- Data bus drives directly to slot.

- 68-pin PLCC package.

- Supports MFM Disk Controller

Sector Buffer RAM Addressing and Control Data Bus Interface Control HDC Status & Control Port

The UM83C003 connects directly to the Host interface Data/Command and intraboard Command/Data buses.

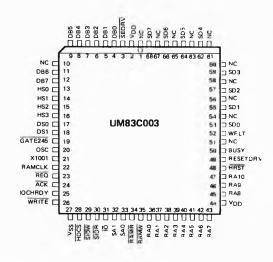

### Pin Configuration

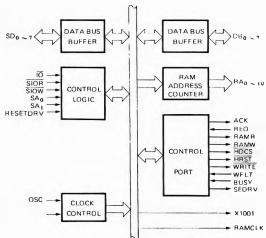

### **Block Diagram**

### **Absolute Maximum Ratings\***

| Operating Temperature   |  | <br> |  |  | 0°C to +70°C    |

|-------------------------|--|------|--|--|-----------------|

| Storage Temperature     |  |      |  |  |                 |

| All Output Voltages     |  | <br> |  |  | $-0.5$ to + 7 \ |

| All Input Voltages      |  | <br> |  |  | $-0.5$ to + 7 \ |

| Supply Voltage $V_{CC}$ |  | <br> |  |  | $-0.5$ to + 7 \ |

| Power Dissipation       |  | <br> |  |  | 1V              |

### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D. C. Electrical Characteristics ( $V_{CC} = 5.0V \pm 5\%$ , $T_A = 0 \sim 70^{\circ}C$ )

| Symbol          | Characteristic                                                                                               | Min.       | Тур. | Max.            | Unit |

|-----------------|--------------------------------------------------------------------------------------------------------------|------------|------|-----------------|------|

| V <sub>IH</sub> | Input High Voltage                                                                                           | 2.0        | _    | V <sub>cc</sub> | V    |

| VIL             | Input Low Voltage                                                                                            | 0          | -    | 0.8             | V    |

| V <sub>OH</sub> | Output High Voltage $I_{Load} = -6.4\text{mA (SD0} \sim \text{SD7)}$ $I_{Load} = -3.2\text{mA (all others)}$ | 2.4<br>2.4 | =    | -               | V    |

| VOL             | Output Low Voltage  I Load = 6.4mA (SD0 ~ SD7)  I Load = 3.2mA (all others)                                  | -          | =    | 0.4<br>0.4      | V    |

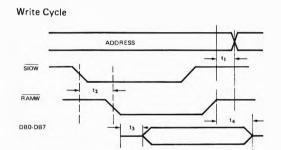

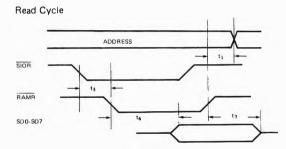

### **AC Characteristics**

| Symbol         | Item                       | Min. | Max. | Unit |

|----------------|----------------------------|------|------|------|

| tı             | Address hold time          | 10   | _    | ns   |

| t <sub>2</sub> | RAMW time delay            | -    | 50   | ns   |

| t <sub>3</sub> | RAMW low to data output    | -    | 60   | ns   |

| t <sub>4</sub> | Data hold time             | _    | 15   | ns   |

| tş             | RAMR time delay            | -    | 40   | ns   |

| t <sub>6</sub> | RAMR low to data output    | -    | 140  | ns   |

| t <sub>7</sub> | RAMR high to data High Z   | _    | 60   | ns   |

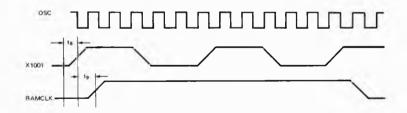

| t <sub>8</sub> | OSC to X1001 delay time    |      | 50   | ns   |

| tg             | X1001 to RAMCLK delay time |      | 25   | ns   |

#### Capacitance

| Parameter                                     | Max.     | Unit     |

|-----------------------------------------------|----------|----------|

| Output Capacitance<br>SD0 ~ SD7<br>All others | 50<br>20 | pF<br>pF |

# Pin Description

| Number                              | Symbol               | I/O | Description                                                                                                                                                                                                       |

|-------------------------------------|----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53, 55, 57<br>59, 62, 64,<br>66, 68 | SD0-SD7              | 1/0 | These lines provide data bus bit0-bit7 for system microprocessor.                                                                                                                                                 |

| 4, 5, 6, 7,<br>8, 9, 11, 12         | DB0-DB7              | 1/0 | These lines provide data bus bit0-bit7 for static RAM, & controller.                                                                                                                                              |

| 3                                   | SEDRV                | ı   | This command line indicates selection of drive no, or drive head no. This signal is active low.                                                                                                                   |

| 20                                  | OSC                  | ı   | This signal is supported by the external oscillator. The working frequency is 30 MHz.                                                                                                                             |

| 23<br>24                            | REQ<br>ACK           | 0   | These signal pins indicate that another master is requesting a local bus. The chip receiving the REQ will issue ACK as an acknowledgement in the RAM CLK clock cycle. These signals are active low.               |

| 29                                  | SIOW                 | I   | This command line is an input control signal used by the CPU to load information into the chip. This signal is active low.                                                                                        |

| 30                                  | SIOR                 | I   | This command line is an input control signal used by the CPU to read the control signal. It is active low.                                                                                                        |

| 31                                  | ĪŌ                   | 1   | A "Low" on this chip enables the chip. No reading or writing will occur unless the chip is selected. This signal is active low.                                                                                   |

| 33                                  | SA0                  |     | These inputs are normally connected to the address bus.                                                                                                                                                           |

| 32                                  | SA1                  | 1   |                                                                                                                                                                                                                   |

| 49                                  | RESETDRV             | 1   | A "High" on the input which resets all control registers on the chip.                                                                                                                                             |

| 50                                  | BUSY                 | ı   | BUSY is high when the operation is in process. The CPU can read the status of the controller used by this pin.                                                                                                    |

| 51                                  | NC                   |     |                                                                                                                                                                                                                   |

| 52                                  | WFLT                 | 1   | When the drive encounters an error in process. It sends an error signal to the controller to indicate "Write fault". The CPU can read the error message of the controller used by this pin. It is active high.    |

| 13, 14,<br>15, 16                   | HSO, HS1<br>HS2, HS3 | 0   | No. of the drive head. 16 heads are selected.                                                                                                                                                                     |

| 17, 18                              | DS0, DS1             | 0   | No. of the disk. 4 disks are selected.                                                                                                                                                                            |

| 19                                  | GATE245              | 0   | This signal pin is optional. If the sink current of SDO-SD7 is not enough to drive the system data bus, the gate 74LS245 is directly connected by using this pin.                                                 |

| 21                                  | X1001                | 0   | When MFMSW is high, X1001 is OSC/3. Otherwise, X1001 is OSC/2.                                                                                                                                                    |

| 22                                  | RAMCLK               | 0   | When MFMSW is high. RAMCLK is OSC/9. Otherwise, RAMCLK is OSC/6.                                                                                                                                                  |

| 25                                  | IOCHRDY              | 0   | When this signal is active high, it may use this line during a write operation if more time is needed to store the data from the bus. It also holds the data long enough for the system microprocessor to sample. |

| 26                                  | WRITE                | 0   | This command line indicates that the UM83C001 chip fetches a read or write operation. This signal is active low.                                                                                                  |

## Pin Descriptions (Continued)

| Number                                              | Symbol   | I/O | Description                                                                                                             |

|-----------------------------------------------------|----------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 28                                                  | HDCS     | 0   | A "Low" on this input enables the UM83C001 chip. No reading or writing will occur unless the UM83C001 chip is selected. |

| 35                                                  | RAMW     | 0   | The command line indicates that the CPU is loading information into static RAM. This signal is active low.              |

| 34                                                  | RAMR     | 0   | The command line indicates that the static RAM is sending data to the data bus. This signal is active low.              |

| 48                                                  | HRST     | 0   | HRST is an active low output dervied from the RESETDRV input.                                                           |

| 36, 37, 38,<br>39, 40, 41,<br>42, 43, 45,<br>46, 47 | RA0-RA10 | 0   | The signals are connected to the static RAM address. The data in the static RAM is read or written by the controller.   |

# **Timing Waveforms**

## **Clock Timing**